コマンド ラインからの Simulink モデルの HDL コードの生成

HDL コード生成オプションをカスタマイズおよび編集してから、コマンド ラインでコードを生成できます。この例では、[コンフィギュレーション パラメーター] ダイアログ ボックスを使用して対称 FIR フィルター モデルの HDL コードを生成する方法を説明します。

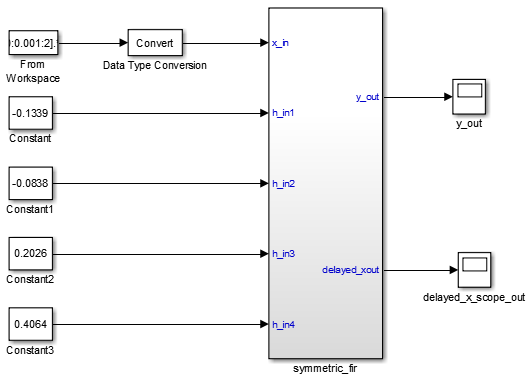

FIR フィルター モデル

HDL コードを生成する前に、モデルは HDL コード生成と互換性がなければなりません。HDL 互換性についてモデルのチェックと更新を行うには、HDL コード アドバイザーを使用した Simulink モデルの HDL 互換性のチェックを参照してください。関数 hdlsetup を使用して、モデル パラメーターをカスタマイズすることもできます。

hdlsetup(gcs)

この例では、HDL コード生成と互換性のある対称 FIR フィルター モデルを使用します。このモデルをコマンド ラインで開くには、次を入力します。

sfir_fixed

モデルは、HDL 設計に適した作業分担を使用します。

フィルターのアルゴリズムを実装する

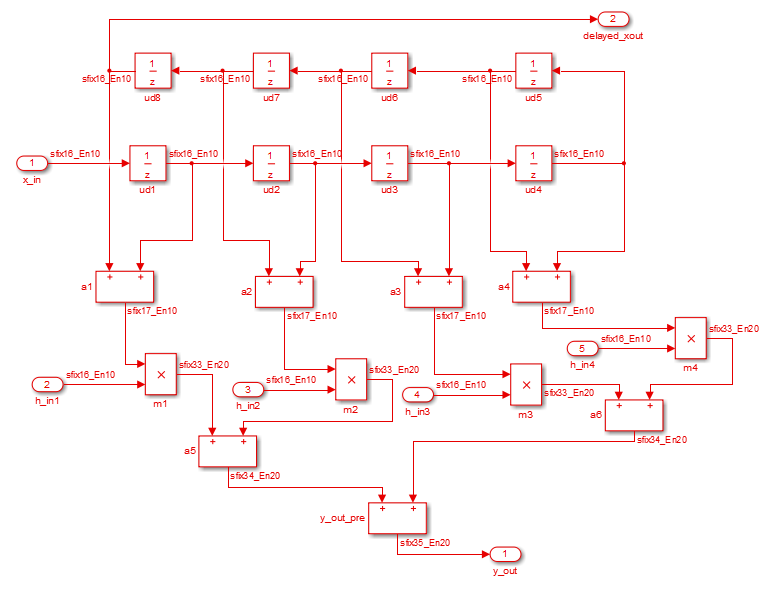

symmetric_firサブシステムがテスト対象デバイス (DUT) です。HDL エンティティはこのサブシステムから生成されます。サブシステムを駆動する最上位のモデル コンポーネントはテスト ベンチとして機能します。

最上位モデルは symmetric_fir サブシステムに対して 16 ビットの固定小数点入力信号を生成します。Signal From Workspace ブロックはフィルターに対するテスト入力 (スティミュラス) 信号を生成します。4 つの Constant ブロックがフィルター係数を示しています。Scope ブロックはシミュレーションに使用され、HDL コード生成には使用されません。

symmetric_fir サブシステムに移動するには、次を入力します。

open_system('sfir_fixed/symmetric_fir')

フォルダーの作成と関連ファイルのコピー

MATLAB® で、以下を実行します。

sl_hdlcoder_workという名前のフォルダーを作成します。たとえば、次のようにします。mkdir C:\work\sl_hdlcoder_worksl_hdlcoder_workは、モデル例とフォルダーのローカル コピーおよび生成された HDL コードを保存します。MATLAB フォルダー ツリー内にないフォルダーの場所を使用します。sl_hdlcoder_workを作業フォルダーにします。たとえば、次のようにします。cd C:\work\sl_hdlcoder_worksfir_fixedモデルのローカル コピーを現在の作業フォルダーに保存します。モデルを開いたままにしておきます。

HDL コードの生成

DUT の HDL コードを生成するには、関数 makehdl を使用します。たとえば、symmetric_fir サブシステムの HDL コードを生成するには、次を入力します。

makehdl('sfir_fixed/symmetric_fir')HDL コードを生成する前にカスタマイズを指定するには、関数 hdlset_param を使用します。関数 makehdl でさまざまな名前と値のペアの引数を使用して、HDL コードの生成中に HDL コード生成オプションをカスタマイズすることもできます。たとえば、Verilog コードを生成するには、TargetLanguage プロパティを使用します。

makehdl('sfir_fixed/symmetric_fir', 'TargetLanguage', 'Verilog')

hdlset_param を使用している場合、モデルのこのパラメーターを設定してから、関数 makehdl を実行します。hdlset_param('sfir_fixed', 'TargetLanguage', 'Verilog') makehdl('sfir_fixed/symmetric_fir')

HDL Coder™ は、コードの生成前にモデルをコンパイルします。端子のデータ型などのモデルの表示オプションによっては、コードの生成後にモデルの外観が変わることがあります。コードの生成が進むにつれて、HDL Coder によって MATLAB コマンド ラインに次のリンクを備えた進行状況を示すメッセージが表示されます。

コンフィギュレーション パラメーターが適用されたモデルを示すコンフィギュレーション セットへのリンク。

生成されたファイルへのリンク。MATLAB エディターでファイルを表示するには、リンクをクリックします。

symmetric_fir.vhd:VHDL コード。このファイルにはsymmetric_fir.vhdフィルターを実装する RTL アーキテクチャとエンティティ定義が含まれています。symmetric_fir_compile.do: 生成された VHDL コードをコンパイルする Siemens® ModelSim™ コンパイル スクリプト (vcom コマンド)。symmetric_fir_synplify.tcl: Synplify® 合成スクリプト。symmetric_fir_map.txt:このレポートは、生成されたエンティティをエンティティを生成したサブシステムにマッピングします。マッピング ファイルを使用したコードのトレースを参照してください。

プロセスが終了すると次のメッセージが表示されます。

### HDL Code Generation Complete.