このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

HDL コード生成オプションの設定

[コンフィギュレーション パラメーター] ダイアログ ボックスの HDL コード生成オプション

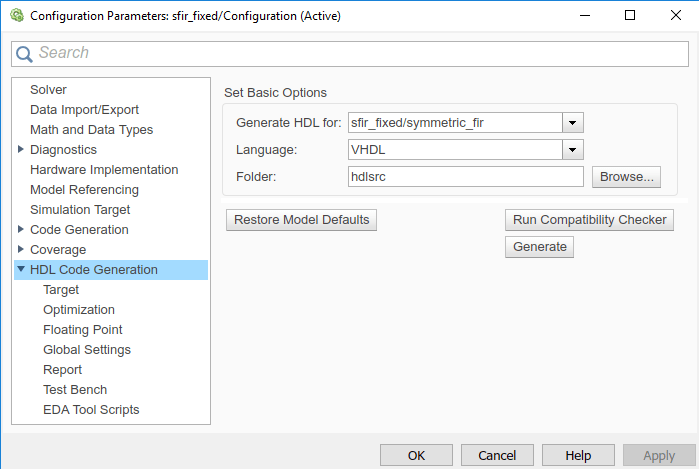

次の図は、[コンフィギュレーション パラメーター] ダイアログ ボックスの最上位の [HDL コード生成] ペインを示しています。このダイアログ ボックスを開くには、アプリ ギャラリーで [HDL Coder] をクリックします。[HDL コード] タブが表示されます。[準備] セクションで、[設定] をクリックします。

メモ

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] ペインが表示された後、[ヘルプ] ボタンをクリックすると [コンフィギュレーション パラメーター] ダイアログ ボックスに関する一般的なヘルプが表示されます。

Simulink ツールストリップの [HDL コード] タブ

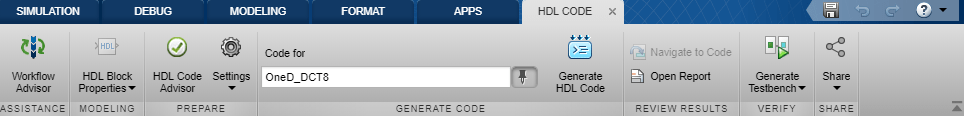

Simulink® ツールストリップには、アクセスする必要がある場合のみ、表示されるコンテキスト タブが含まれています。[HDL コード] タブにアクセスするには、Simulink ツールストリップの [アプリ] タブから [HDL Coder] アプリを開きます。

[HDL コード] タブは、HDL コード生成オプションへのショートカットを提供します。このタブを使用してコード生成を開始することもできます。

オプションは次のとおりです。

[ワークフロー アドバイザー]: HDL ワークフロー アドバイザーを開きます。

[HDL ブロック プロパティ]: Simulink ライブラリ ブラウザーで HDL 互換ブロック ライブラリを開くか、モデルで選択するブロックの [HDL ブロック プロパティ] ダイアログ ボックスを開きます。

メモ

HDL 互換ブロック ライブラリを開いた後に、ライブラリ ブラウザーを既定のビューに戻すには、ライブラリ ブラウザーで

ボタンをクリックします。

ボタンをクリックします。[HDL Code アドバイザー]: モデルの HDL コード アドバイザーまたは選択した Subsystem を開きます。

[設定]: [コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] ペインを開きます。

[レポート オプション]: [HDL コード生成] 、 [レポート] ペインを開きます。

[モデルから HDL 設定を削除]: "HDL コンフィギュレーション コンポーネント" は、HDL Coder™ によって生成され、モデルに追加される内部データです。このコンポーネントにより [コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] ペインを表示し、[HDL コード生成] ペインを使用して HDL コード生成オプションを設定できます。HDL コード生成コンフィギュレーション コンポーネントをモデルから削除するには、このオプションを選択します。詳細については、HDL コンフィギュレーション コンポーネントの追加または削除を参照してください。

[次のコード]: HDL コードを生成する最上位の Subsystem またはモデルを選択します。このオプションは、[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] ペインの [HDL を生成] オプションに対応します。

[HDL コードの生成]: HDL コードの生成を開始します。[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [グローバル設定] 、 [詳細設定] タブの [HDL コードを生成] チェック ボックスと同様です。

コードに移動: モデルのブロックを選択し、そのブロックについて生成された HDL コードに移動します。この設定を使用するには、生成されたトレーサビリティ レポートが必要です。

[レポートを開く]: このレポートがパスに存在する場合、コード生成レポートを開きます。そうでない場合は、このボタンで HDL チェック レポートを開きます。

テスト ベンチを生成: テスト ベンチ コードの生成を開始します。[コンフィギュレーション パラメーター] ダイアログ ボックスの [テスト ベンチを生成] ボタンと同様です。このボタンを使用するために、[HDL を生成] メニューでサブシステムを選択していない場合は、[テスト ベンチを生成] メニュー オプションは利用できません。

HDL Verifier™ がインストールされている場合、HDL コシミュレーション モデルまたは SystemVerilog DPI コンポーネントを生成できます。

共有: モデルの知的財産を開示せずにサードパーティと共有できる保護モデルを生成します。

ブロックのコンテキスト メニューの HDL コード オプション

HDL Coder でサポートされているブロックを右クリックすると、ブロックのコンテキスト メニューに [HDL コード] サブメニューが表示されます。サブメニューの項目は、次のようにして決定されます。

ブロック タイプ: サブシステムについては、サブシステムに固有なオプションの一部がメニューで利用可能になります。

ブロックまたはサブシステムのコードおよびトレーサビリティ情報が生成されているかどうか。

メモ

Simulink ツールストリップの [HDL コード] タブからコンテキスト メニューのオプションにアクセスすることもできます。このタブにアクセスするには、[アプリ] タブから [HDL Coder] アプリを開きます。

[HDL コード] サブメニューのオプションを以下にまとめています。

| オプション | 説明 | 対象 |

|---|---|---|

| サブシステムの互換性チェック | サブシステムに対して HDL の互換性チェッカー (checkhdl) を実行します。 | サブシステムのみに利用できます。 |

| サブシステムに対する HDL を生成 | HDL コード ジェネレーター (makehdl) を実行し、サブシステムのコードを生成します。 | サブシステムのみに利用できます。 |

| HDL Coder プロパティ | [コンフィギュレーション パラメーター] ダイアログ ボックスの最上位の [HDL コード生成] ペインを表示します。 | ブロックまたはサブシステムに利用できます。 |

| HDL ブロック プロパティ | ブロックまたはサブシステムの [ブロック プロパティ] ダイアログ ボックスを開きます。詳細は、HDL モデルおよびブロック パラメーターの設定と表示を参照してください。 | ブロックまたはサブシステムに利用できます。 |

| HDL ワークフロー アドバイザー | サブシステムの HDL ワークフロー アドバイザーを開きます。 | サブシステムのみに利用できます。 |

| コードに移動 | [HTML コード生成レポート] ウィンドウをアクティブにし、選択したブロックまたはサブシステムに対して生成されたコードの先頭を表示します。詳細については、トレーサビリティを使用した Simulink モデルと HDL コード間の移動を参照してください。 | ブロックまたはサブシステムに対するコードとトレーサビリティ レポートの両方が生成されている場合に有効になります。 |

[HDL ブロック プロパティ] ダイアログ ボックス

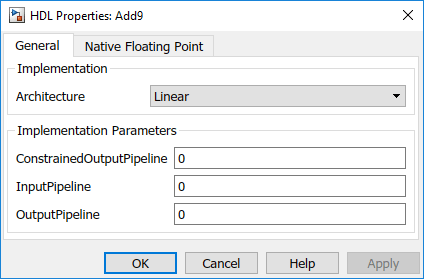

HDL Coder には、多数のブロック タイプ用に選択可能な代替の "ブロックの実装" が用意されています。それぞれの実装は、速度やチップ面積などのさまざまな特性に最適化されています。[HDL プロパティ] ダイアログ ボックスにより、選択したブロックの実装を選択できます。

ほとんどのブロック実装には、ブロックのコード生成をより詳細に制御するための "実装パラメーター" をいくつかサポートしています。[HDL プロパティ] ダイアログ ボックスにより、ブロックに実装パラメーターを設定できます。

次の図は、ブロックの [HDL プロパティ] ダイアログ ボックスを示したものです。

個別またはブロックのグループに実装および実装パラメーターを指定する方法がいくつかあります。HDL モデルおよびブロック パラメーターの設定と表示を参照してください。