hdl.treesum

説明

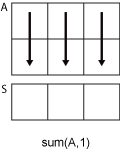

S = hdl.treesum(A)

Aがベクトルの場合、hdl.treesum(A)は要素の和を返します。Aが行列の場合、hdl.treesum(A)は各列の和を含む行ベクトルを返します。

関数 hdl.treesum は Tree アーキテクチャを使用して要素の加算を行います。Tree アーキテクチャの加算によって、クリティカル パスはより短くなり、それにより、MATLAB Function ブロックから HDL コードを生成する際のレイテンシが削減されます。HDL コードを生成する際に、関数 hdl.treesum は要素の加算を行うのに必要な一致する遅延の量を削減します。

例

入力引数

出力引数

拡張機能

バージョン履歴

R2022a で導入