このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

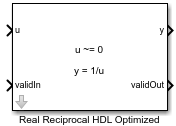

Real Reciprocal HDL Optimized

CORDIC アルゴリズムを使って逆数を計算して最適化された HDL コードを生成

ライブラリ:

Fixed-Point Designer HDL Support /

Math Operations

説明

Real Reciprocal HDL Optimized ブロックは、1/u を計算します。ここで、u は実数スカラーです。

例

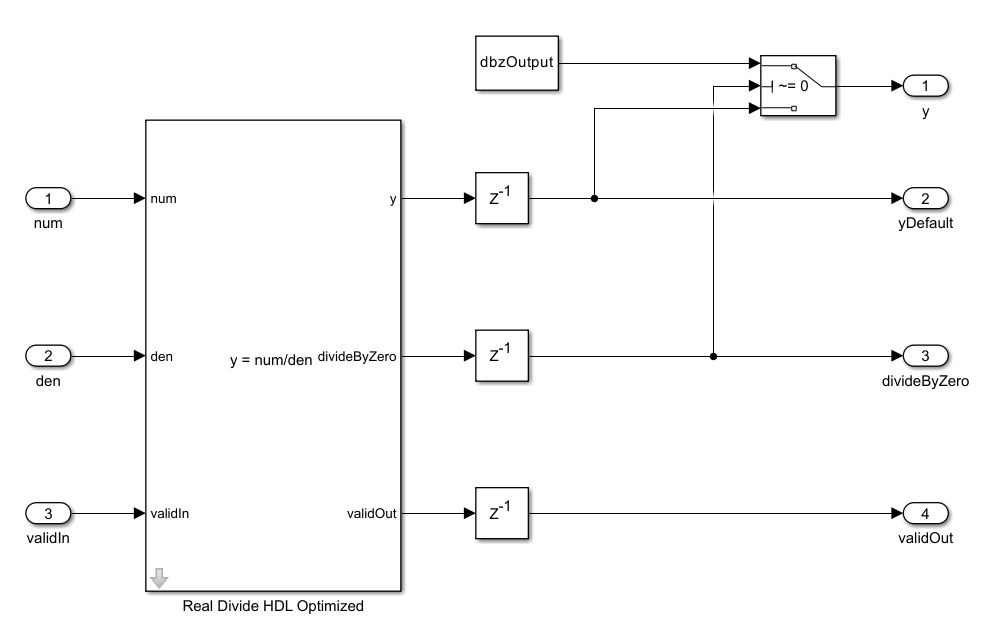

Customize Output Value of Real Divide HDL Optimized Block When Denominator Is Zero

Use the divideByZero port to customize the value of the block output when division by zero occurs.

- R2024b 以降

- ライブ スクリプトを開く

How to Set CORDIC Input Word Length and Maximum Shift Value to Achieve Desired Precision

Provides a starting point for the input data type and number of iterations or maximum shift value required for the CORDIC algorithm to achieve a desired accuracy.

制限

Real Reciprocal HDL Optimized ブロックではデータ型オーバーライドはサポートされていません。

端子

入力

出力

逆数。[出力データ型] パラメーターで指定されたデータ型の実数スカラーとして返されます。

データ型: single | double | fixed point

R2024b 以降

y 出力端子の値がゼロ除算演算の結果であるかどうか。boolean スカラーとして返されます。この信号の値が 1 (true) の場合、y 端子の対応する出力値はゼロ除算の結果です。この信号の値が 0 (false) の場合、y 端子の対応する出力値は非ゼロ値による除算の結果です。

既定のゼロ除算の動作の説明については、ゼロ除算の動作を参照してください。

依存関係

この端子を有効にするには、[ゼロ除算端子を表示] パラメーターを選択します。

データ型: Boolean

出力データが有効であるかどうか。boolean スカラーとして返されます。この制御信号の値が 1 (true) の場合、ブロックは端子 y の出力を正常に計算しています。この値が 0 (false) の場合、出力データは有効ではありません。

データ型: Boolean

パラメーター

出力 y のデータ型。fixdt(1,18,10)、single、double、fixdt(1,16,0)、またはユーザー指定のデータ型式として指定します。型は直接指定されるか、Simulink.NumericType などのデータ型オブジェクトとして表現されます。

R2024b において: このパラメーターでは、符号なしデータ型がサポートされています。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

ブロック パラメーターの値をプログラムで取得するには、関数 get_param を使用します。

| パラメーター: | OutputType |

| 値: | fixdt(1,18,10) (既定値) | single | double | fixdt(1,16,0) | <data type expression> |

| データ型: | char | string |

例: set_param(gcb,"OutputType","fixdt(1,16,0)")

R2024b 以降

divideByZero 端子を表示する場合は、このパラメーターを選択します。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

ブロック パラメーターの値をプログラムで取得するには、関数 get_param を使用します。

| パラメーター: | dbzPort |

| 値: | 0 (false) (既定値) | 1 (true) |

| データ型: | logical |

例: set_param(gcb,"dbzPort",1)

R2024b 以降

入力の語長に基づいて CORDIC の最大シフト値を自動選択します。このパラメーターが選択されている場合、既定の CORDIC の maximumShiftValue は wl - 1 に等しくなります。ここで、wl = u.WordLength + ~issigned(u) です。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

ブロック パラメーターの値をプログラムで取得するには、関数 get_param を使用します。

| パラメーター: | autoMaximumShiftVal |

| 値: | on (既定値) | off |

| データ型: | char | string |

例: set_param(gcb,"autoMaximumShiftVal","off")

R2024b 以降

双曲線ベクトル CORDIC の最大シフト値。正の整数値スカラーとして指定します。このパラメーターの既定値は wl - 1 です。ここでは wl = u.WordLength + ~issigned(u) です。

依存関係

このパラメーターを有効にするには、[入力の語長に基づいて CORDIC の最大シフト値を自動選択] パラメーターをクリアします。

ヒント

詳細については、カスタマイズ可能なパイプラインを参照してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

ブロック パラメーターの値をプログラムで取得するには、関数 get_param を使用します。

| パラメーター: | maximumShiftValue |

| 値: | 10 (既定値) | positive integer-valued scalar |

| データ型: | char | string |

例: set_param(gcb,"maximumShiftValue","10")

R2024b 以降

パイプライン ステージごとに実行する CORDIC の反復回数。正の整数値のスカラーとして指定します。

詳細については、カスタマイズ可能なパイプラインを参照してください。詳細と、このパラメーターがレイテンシとハードウェア リソースの使用率に与える影響を示す例については、Real Reciprocal HDL Optimized ブロックとのインターフェイスとハードウェア リソースの使用を参照してください。

プログラムでの使用

ブロック パラメーターの値をプログラムで設定するには、関数 set_param を使用します。

ブロック パラメーターの値をプログラムで取得するには、関数 get_param を使用します。

| パラメーター: | nIterPerReg |

| 値: | 1 (既定値) | positive integer-valued scalar |

| データ型: | char | string |

例: set_param(gcb,"nIterPerReg","2")

ヒント

Real Reciprocal HDL Optimized ブロックの動作は

fixed.cordicReciprocal関数と同じです。関数への入力が 2 進小数点でスケーリングされた固定小数点データ型をもつ実数の場合、関数とブロックはビット単位で正確に一致する結果を提供します。

アルゴリズム

CORDIC は、COordinate Rotation DIgital Computer の略語です。ギブンス回転に基づく CORDIC アルゴリズムは、Shift-Add 反復演算のみを必要とするため、ハードウェア効率が最も優れたアルゴリズムの 1 つです (参考文献を参照)。CORDIC アルゴリズムは、明示的な乗数を必要としません。CORDIC を使用すると、正弦関数、余弦関数、逆正弦関数、逆余弦関数、逆正接関数、ベクトル振幅関数などのさまざまな関数を計算できます。また、このアルゴリズムは除算、平方根、双曲線、対数などの関数にも使用できます。

CORDIC アルゴリズムの精度は、使用されるデータ型と CORDIC カーネルの最大シフト値または最大反復回数の関数になります。より語長が長いデータ型を使用し、CORDIC アルゴリズムの反復回数を増やすほど、結果の数値誤差を減らすことができます。ただし、これを行うと計算のレイテンシも増加し、より多くのハードウェア リソースが利用されます。詳細については、How to Set CORDIC Input Word Length and Maximum Shift Value to Achieve Desired Precisionを参照してください。

入力 u がゼロで固定小数点データ型の場合、出力 y は upperbound( と等しくなります。Output datatype)

浮動小数点入力については、Real Divide HDL Optimized ブロックは IEEE® Standard 754 に従います。

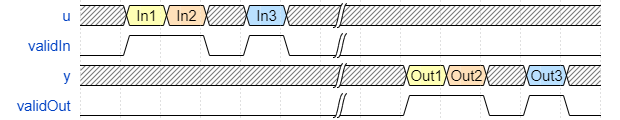

Real Reciprocal HDL Optimized ブロックは、完全にパイプライン化されるという性質から、連続するクロック サイクルを含む任意のサイクルで入力データを受け入れることができます。入力データをブロックに送信するには、validIn 信号が true でなければなりません。ブロックが計算を終え、出力を送信する準備ができると、1 クロック サイクルの間、validOut を true に変更します。連続するサイクルの入力のセットの場合、連続するサイクルでも validOut が true に設定されます。

レイテンシは入力から対応する出力までとして定義されます。たとえば、次の図では、In1 から Out1 まで、In2 から Out2 まで、In3 から Out3 までです。

レイテンシは入力のデータ型によって異なります。これを次の表にまとめます。

| 入力の型 | レイテンシ |

|---|---|

固定小数点またはスケーリングされた double |

ここで、

|

浮動小数点 | 0 |

Real Reciprocal HDL Optimized ブロックは、反復正規化と CORDIC ベースの除算アルゴリズムを実装する完全にパイプライン化されたアーキテクチャを使用します。入力 u が固定小数点またはスケーリングされた double データ型の場合、ブロックは計算に複数のパイプライン ステージを使用します。入力が符号付きデータ型の場合、正規化には nextpow2(u.WordLength) 回の反復が必要です。CORDIC の反復回数は、[CORDIC の最大シフト値] パラメーターの値によって異なります。語長が長いほど分解能は高くなりますが、処理にはより多くの反復が必要になります。Real Reciprocal HDL Optimized ブロックはパイプライン ステージごとに複数回の反復を実行できるため、生成された HDL コードでクリティカル パスは長くなりますが、レイテンシは短縮します。

たとえば、入力 u の語長が 18 の場合、正規化には 5 回の反復が必要です。[入力の語長に基づいて CORDIC の最大シフト値を自動選択] パラメーターが選択されている場合、CORDIC の最大シフト値は 18 - 1 = 17 となり、17 回の反復が必要になります。反復の総数は 5 + 17 = 22 で、ブロックのレイテンシは ceil((total number of iterations)/nIterPerReg) + 1 です。パイプライン レジスタごとの反復回数が 1 に設定されている場合、ブロック レイテンシは 23 です。パイプライン レジスタごとの反復回数が 2 に設定されている場合、ブロック レイテンシは 12 です。パイプライン レジスタごとの反復回数が必要な反復の総数より大きい場合、ブロックは 1 つのパイプライン ステージですべての反復を実行し、合計レイテンシは 2 に最小化されます。

このブロックは、Simulink® HDL ワークフロー アドバイザーを使用した HDL コード生成をサポートしています。例については、Simulink モデルからの HDL コード生成と FPGA 合成 (HDL Coder)およびImplement Digital Downconverter for FPGA (DSP HDL Toolbox)を参照してください。

この例のデータは、Xilinx® Zynq®-7000 xc7z045 SoC でブロックを合成して生成したものです。合成ツールは Vivado® v2023.1.2 です。

次の合成結果は、レイテンシとハードウェア リソースの使用率に対する [パイプライン レジスタあたりの反復回数] パラメーターの影響を示しています。

nIterPerReg = 1合成には次のパラメーターが使用されました。

入力データ型:

sfix18_en10出力データ型:

sfix18_en10入力次元: スカラー

入力の語長に基づいて CORDIC の最大シフト値を自動選択:

onパイプライン レジスタあたりの反復回数:

1ターゲット周波数: 500 MHz

この構成のレイテンシ: 23

| リソース | 使用 | 使用可能 | 使用率 (%) |

|---|---|---|---|

| スライス LUT | 815 | 218600 | 0.37 |

| スライス レジスタ | 703 | 437200 | 0.16 |

| DSP | 0 | 900 | 0.00 |

| ブロック RAM タイル | 0 | 545 | 0.00 |

| URAM | 0 | 0 |

値 | |

|---|---|

| 要件 | 2 ns (500 MHz) |

| データ パス遅延 | 1.74 ns |

| スラック | 0.176 ns |

| クロック周波数 | 548.25 MHz |

nIterPerReg = 2合成には次のパラメーターが使用されました。

入力データ型:

sfix18_en10出力データ型:

sfix18_en10入力次元: スカラー

入力の語長に基づいて CORDIC の最大シフト値を自動選択:

onパイプライン レジスタあたりの反復回数:

2ターゲット周波数: 300 MHz

この構成のレイテンシ: 12

| リソース | 使用 | 使用可能 | 使用率 (%) |

|---|---|---|---|

| スライス LUT | 705 | 218600 | 0.32 |

| スライス レジスタ | 374 | 437200 | 0.09 |

| DSP | 0 | 900 | 0.00 |

| ブロック RAM タイル | 0 | 545 | 0.00 |

| URAM | 0 | 0 |

値 | |

|---|---|

| 要件 | 3.3333 ns (300 MHz) |

| データ パス遅延 | 2.65 ns |

| スラック | 0.676 ns |

| クロック周波数 | 376.32 MHz |

nIterPerReg = 3合成には次のパラメーターが使用されました。

入力データ型:

sfix18_en10出力データ型:

sfix18_en10入力次元: スカラー

入力の語長に基づいて CORDIC の最大シフト値を自動選択:

onパイプライン レジスタあたりの反復回数:

3ターゲット周波数: 200 MHz

この構成のレイテンシ: 9

| リソース | 使用 | 使用可能 | 使用率 (%) |

|---|---|---|---|

| スライス LUT | 680 | 218600 | 0.31 |

| スライス レジスタ | 281 | 437200 | 0.06 |

| DSP | 0 | 900 | 0.00 |

| ブロック RAM タイル | 0 | 545 | 0.00 |

| URAM | 0 | 0 |

値 | |

|---|---|

| 要件 | 5 ns (200 MHz) |

| データ パス遅延 | 3.889 ns |

| スラック | 1.125 ns |

| クロック周波数 | 258.06 MHz |

参照

[1] Volder, Jack E. “The CORDIC Trigonometric Computing Technique.” IRE Transactions on Electronic Computers. EC-8, no. 3 (Sept. 1959): 330–334.

[2] Andraka, Ray. “A Survey of CORDIC Algorithm for FPGA Based Computers.” In Proceedings of the 1998 ACM/SIGDA Sixth International Symposium on Field Programmable Gate Arrays, 191–200. https://dl.acm.org/doi/10.1145/275107.275139.

[3] Walther, J.S. “A Unified Algorithm for Elementary Functions.” In Proceedings of the May 18-20, 1971 Spring Joint Computer Conference, 379–386. https://dl.acm.org/doi/10.1145/1478786.1478840.

[4] Schelin, Charles W. “Calculator Function Approximation.” The American Mathematical Monthly, no. 5 (May 1983): 317–325. https://doi.org/10.2307/2975781.

拡張機能

傾きとバイアス表現は固定小数点データ型ではサポートされていません。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

このブロックには 1 つの既定の HDL アーキテクチャがあります。

| 一般 | |

|---|---|

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

R2024b において: FlattenHierarchy | 生成された HDL コードから PWM Reference Generator ブロック階層を削除します。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

固定小数点データ型のみをサポートします。

バージョン履歴

R2021a で導入Real Reciprocal HDL Optimized ブロックにいくつかの改善が加えられました。

カスタム パイプラインが新しい [CORDIC の最大シフト値] パラメーターと [パイプライン レジスタあたりの反復回数] パラメーターを介してサポートされます。

このブロックのレイテンシが短縮されました。レイテンシは、指定されたデータ型とパイプライン構成によって異なります。詳細については、Real Reciprocal HDL Optimized ブロックとのインターフェイスを参照してください。

HDL リソースの使用率がさらに最適化され、必要なハードウェア リソースが減りました。合成結果の例については、ハードウェア リソースの使用を参照してください。

対応する出力がゼロ除算の結果である場合にフラグを出力するオプションの divideByZero 端子が追加されました。

Real Reciprocal HDL Optimized ブロックの [出力データ型] パラメーターで符号なしデータ型がサポートされるようになりました。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)