HDL コード生成

FPGA または ASIC で DSP 設計を実装するには、HDL Coder™ を使用して Simulink または MATLAB からコードを生成します。このツールは、合成可能で移植可能な VHDL® と Verilog® のコードを生成し、生成されたコードのシミュレーションやテスト、検証をすばやく行うための VHDL と Verilog のテスト ベンチも生成します。

DSP System Toolbox™ およびDSP HDL Toolboxでサポートされているブロックには、フィルター、数学演算および信号処理のほか、FFT (DSP HDL Toolbox)、Discrete FIR Filter (DSP HDL Toolbox)、NCO (DSP HDL Toolbox) の各ブロックなど、リソースの使用とパフォーマンスについて最適化されたアルゴリズムが含まれています。DSP HDL Toolbox™ は、ハードウェアに適したアーキテクチャを実装するブロックと System object を提供します。DSP HDL Toolbox のブロックと System object には、スーパー サンプル レートとも呼ばれるギガサンプル/秒 (GSPS) を実現する高スループット ストリーミング インターフェイス、ハードウェア制御信号に加え、アルゴリズムのさまざまなハードウェア実装を選択するオプションもあります。

HDL Coder を使用して DSP System Toolbox のブロックから HDL コードを生成する方法の例については、FPGA 用マルチチャネル FIR フィルターを参照してください。DSP HDL Toolbox の概要については、Implement FFT Algorithm for FPGA (DSP HDL Toolbox)を参照してください。System object™ から HDL コードを生成するには、Generate HDL Code for IIR Filter (DSP HDL Toolbox)を参照してください。

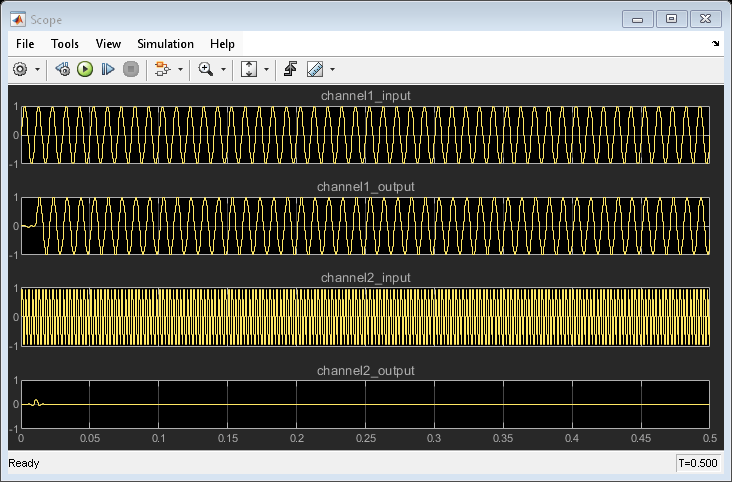

Simulink または MATLAB で設計をデバッグするには、ロジック アナライザーの波形ビューアーを使用します。

Simulink 可視化ツール

| ロジック アナライザー | 時間の経過に沿った遷移と状態の可視化、測定および解析 |

トピック

- HDL コード生成をサポートするブロックの検索

Simulink ライブラリ ブラウザーおよびドキュメンテーション内で、HDL コード生成をサポートするブロックを検索。

- High-Throughput HDL Algorithms (DSP HDL Toolbox)

Choose a block that supports frame-based processing for HDL code generation.

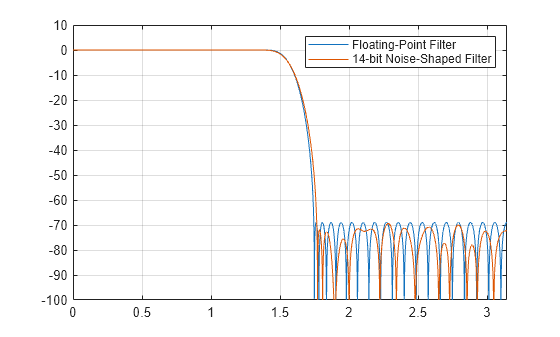

- HDL Filter Architectures

HDL code generation parameters to control speed and area tradeoffs in filter architectures.

- Subsystem Optimizations for Filters

Select resource sharing and pipeline optimization options.

- Visualize Multiple Signals Using Logic Analyzer

Visualize multiple signals of a programmable FIR filter by using the Logic Analyzer app.

- Generate HDL Code for IIR Filter (DSP HDL Toolbox)

Design and generate HDL code for a DC blocking filter in MATLAB.