このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

イーサネットベースの AXI マネージャーを使用して FPGA 外部 DDR メモリ上で大規模な行列乗算を実行する

この例では、イーサネットベースの AXI マネージャーを使用して、FPGA に接続された外部メモリにアクセスする方法を示します。この例では、次の方法も示します。

インターフェースを備えた HDL IP コアを生成します。

イーサネットベースの AXI マネージャー インターフェイスを使用して、Xilinx® Kintex®-7 KC705 ボード上の外部 DDR3 メモリから大規模なマトリックスにアクセスします。

HDL IP コアで行列ベクトル乗算を実行し、イーサネットベースの AXI マネージャー インターフェイスを使用して出力結果を DDR3 メモリに書き戻します。

要件

この例を実行するには、このソフトウェアとハードウェアをインストールしてセットアップする必要があります。

Xilinx Vivado® Design Suite(サポートされているバージョンはに記載されています)

Xilinx Kintex-7 KC705 評価キット

KC705 FPGAに接続するためのJTAGケーブルとイーサネットケーブル

HDL Coder™ Support Package for Xilinx FPGA and SoC Devices

HDL Verifier™ Support Package for Xilinx FPGA Boards

はじめに

この例では、行列ベクトル乗算アルゴリズムをモデル化し、そのアルゴリズムを Xilinx Kintex-7 KC705 ボードに実装します。大きなマトリックスは、FPGA ファブリック上のブロック RAM に効率的にマップされない可能性があります。代わりに、FPGA ボード上の外部 DDR3 メモリにマトリックスを保存します。イーサネットベースの AXI マネージャー インターフェイスは、DDR3 メモリとインターフェイスするベンダー提供のメモリ インターフェイス IP コアと通信することでデータにアクセスできます。この機能により、行列演算やコンピューター ビジョン アルゴリズムなど、大規模なデータ処理を伴い、高スループットの DDR アクセスを必要とするアルゴリズムをモデル化できます。

行列ベクトル乗算モジュールは、2 ~ 4000 の範囲で構成可能な行列サイズを持つ固定小数点行列ベクトル乗算をサポートします。マトリックスのサイズは、AXI4 アクセス可能なレジスタを通じて実行時に構成可能です。

MATLAB® コマンド プロンプトでこのコマンドを入力してモデルを開きます。

modelname = 'hdlcoder_external_memory_axi_master';

open_system(modelname);

モデルアルゴリズム

このサンプル モデルには、FPGA 実装可能なテスト対象設計 (DUT) ブロック、DDR 機能動作ブロック、および入力を駆動して期待される出力を検証するためのテスト環境が含まれています。

DUT サブシステムには、AXI4 マスター読み取りおよび書き込みコントローラーと、行列ベクトル乗算モジュールが含まれています。DUT サブシステムは、AXI4 マスター インターフェイスを使用して外部 DDR3 メモリからデータを読み取り、そのデータを Matrix_Vector_Multiplication モジュールに送り込み、次にイーサネット ベースの AXI マネージャー インターフェイスを使用して出力データを外部 DDR3 メモリに書き込みます。DUT モジュールにはいくつかのパラメータ ポートがあります。これらのポートは AXI4 アクセス可能なレジスタにマップされるため、FPGA にデザインを実装した後でも、MATLAB からこれらのパラメータを調整できます。

matrix_mul_on ポートは、Matrix_Vector_Multiplication モジュールを実行するかどうかを制御します。matrix_mul_on への入力が true の場合、DUT サブシステムは、この例で前述したように、行列ベクトル乗算を実行します。matrix_mul_on への入力が false の場合、DUT サブシステムはデータ ループバック モードを実行します。このモードでは、DUT サブシステムは外部 DDR3 メモリからデータを読み取り、それを Internal_Memory モジュールに書き込み、同じデータを外部 DDR3 メモリに書き戻します。データ ループバック モードは、AXI4 マスターの外部 DDR3 メモリ アクセスの機能を検証する方法です。

また、DUT サブシステム内では、Matrix_Vector_Multiplication モジュールが乗算加算ブロックを使用して、行列ベクトル乗算の内積に対するストリーミング ドット積計算を実装します。

A が N 行 N 列の行列で、B が N 行 1 列のベクトルである場合、行列ベクトル乗算出力は Z = A x B となり、サイズは N 行 1 列になります。

DDR の最初の N 個の値は N 行 1 列のサイズのベクトルとして扱われ、その後に N 行 N 列のサイズの行列データが続きます。最初の N 個の値 (ベクトル データ) は RAM に保存されます。N+1 値以降は、データはマトリックス データとして直接ストリーミングされます。ベクトル データは Vector_RAM から並列に読み取られます。行列入力とベクトル入力の両方が Matrix_mul_top サブシステムに送られます。最初のマトリックス出力は N クロック サイクル後に利用可能になり、出力 RAM に格納されます。再び、ベクトル RAM 読み取りアドレスが 0 に再初期化され、新しいマトリックス ストリームに対応する同じベクトル データの読み取りが開始されます。この操作は行列のすべての行に対して繰り返されます。

この図は、Matrix_Vector_Multiplication モジュールのアーキテクチャを示しています。

イーサネットベースのAXIマネージャーを使用してHDL IPコアを生成する

HDL ワークフロー アドバイザーを起動し、IP コア生成ワークフローを使用してこの設計を Xilinx Kintex-7 ハードウェアに展開します。

1. MATLAB コマンド プロンプトでこのコマンドを入力して、Xilinx Vivado 合成ツール パスを設定します。コマンドを実行するときに独自の Vivado インストール パスを使用します。

hdlsetuptoolpath('ToolName','Xilinx Vivado', ... 'ToolPath','C:\Xilinx\Vivado\2020.2\bin\vivado.bat')

2. DUT サブシステム hdlcoder_external_memory_axi_master/DUT から HDL ワークフロー アドバイザーを起動します。ターゲットインターフェースの設定はモデルに保存されます。ステップ 1.1 では、ターゲット ワークフローは IP コア生成ワークフローであり、ターゲット プラットフォームは Xilinx Kintex-7 KC705 開発ボードです。

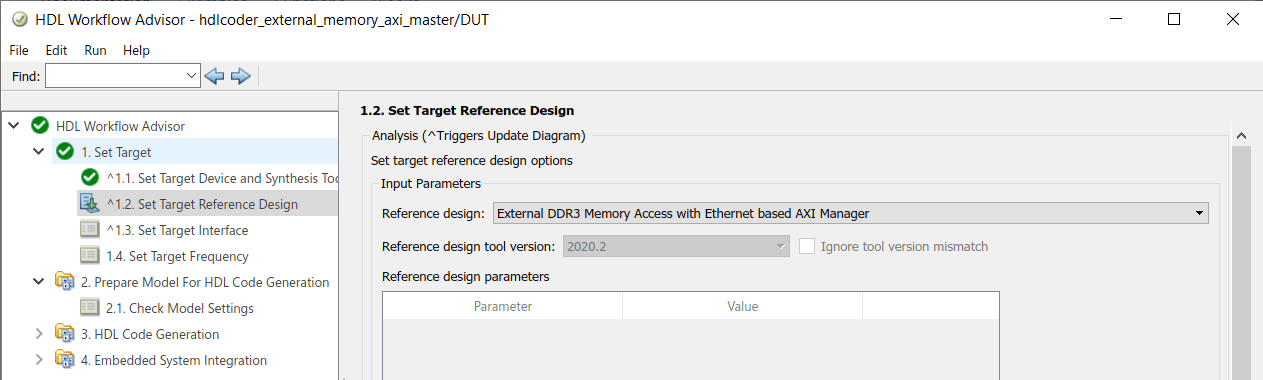

3. ステップ 1.2 で、リファレンス デザイン として External DDR3 Memory Access with Ethernet based AXI Manager を選択します。

4. ターゲット プラットフォームのインターフェイス テーブル設定を確認します。

この例では、matrix_mul_on、matrix_size、burst_len、burst_from_ddr、burst start などの入力パラメータ ポートが AXI4 インターフェイスにマップされます。HDL Coder 製品は、これらのポートに対して AXI4 インターフェイス アクセス可能なレジスタを生成します。FPGA ボード上でデザインが実行されているときに、MATLAB を使用して実行時にこれらのパラメータを調整できます。

イーサネットベースの AXI マネージャー インターフェイスには、読み取りチャネルと書き込みチャネルが別々にあります。axim_rd_data、axim_rd_s2m、axim_rd_m2s などの読み取りチャネル ポートは、AXI4 Master Read インターフェイスにマップされます。axim_wr_data、axim_wr_s2m、axim_wr_m2s などの書き込みチャネル ポートは、AXI4 Master Write インターフェイスにマップされます。

5. ステップ 3.2 の RTL コードと IP コアの生成 を右クリックし、 選択したタスクまで実行 を選択して IP コアを生成します。生成された IP コア レポート内の IP コアについては、レジスタ アドレス マッピングおよびその他のドキュメントを参照してください。

6. ステップ 4.1 の プロジェクトの作成 を右クリックし、このタスクを実行 を選択して Vivado プロジェクトを生成します。プロジェクトの作成中に、生成された DUT IP コアは、イーサネットベースの AXI マネージャー リファレンス デザインを備えた外部 DDR3 メモリ アクセスに統合されます。このリファレンス デザインは、KC705 プラットフォーム上のオンボード外部 DDR3 メモリと通信するための Xilinx メモリ インターフェイス ジェネレーター (MIG) IP で構成されています。AXI Manager IP も追加され、MATLAB が DUT IP を制御し、DDR メモリの内容を初期化および検証できるようになります。

結果ウィンドウのプロジェクト リンクをクリックして、生成された Vivado プロジェクトを表示し、デザインを検査できます。

イーサネットベースの AXI マネージャー IP のデフォルトのターゲット IP アドレスは 192.168.0.2 で、デフォルトの UDP ポート値は 50101 です。これらの値は、Vivado ブロック デザインで ethernet_mac_hub IP をダブルクリックすることで変更できます。

7. ステップ 4.3 の ターゲット デバイスのプログラム を右クリックし、選択したタスクまで実行 を選択してビットストリームを生成し、デバイスをプログラムします。

Kintex-7ハードウェア上でFPGA実装を実行する

FPGA 実装を実行し、MATLAB でこのスクリプトを実行してハードウェアの結果を確認します。

hdlcoder_external_memory_axi_master_hw_run

このスクリプトは、まず Matrix_Size を 500 に初期化します。これは、500 x 500 の行列を意味します。Matrix_Size は最大 4000 まで調整できます。

次に、スクリプトは AXI4 マスターの読み取りおよび書き込みチャネルのベース アドレスを構成します。これらのアドレスは、DUT が外部 DDR メモリから読み取り、外部 DDR メモリに書き込むベース アドレスを定義します。このスクリプトでは、DUT はベース アドレス「40000000」から読み取り、ベース アドレス「50000000」に書き込みます。

AXI マネージャー機能は、入力ベクトルおよびマトリックス データを使用して外部 DDR3 メモリを初期化し、出力 DDR メモリの場所をクリアするために使用されます。

DUT の計算は、AXI4 アクセス可能なレジスタを制御することによって開始されます。DUT IP コアは、DDR メモリから入力データを読み取り、行列ベクトル乗算を実行し、結果を DDR メモリに書き戻します。

最後に、出力結果は MATLAB に読み戻され、期待値と比較されます。このようにして、MATLAB でハードウェアの結果が検証されます。