このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

MATLAB を使用して DPI コンポーネントを生成する

MATLAB 関数とテストベンチを作成する

MATLAB 関数を作成する

SystemVerilog 環境にエクスポートする MATLAB® 関数をコーディングします。MATLAB 関数のコーディングの詳細については、MATLAB ドキュメントの「関数の基本」を参照してください。

関数にコンパイル ディレクティブ %#codegen を追加することを検討してください。このディレクティブは、コード生成中にエラーを引き起こす違反を診断して修正するのに役立ちます。コンパイル命令 %#codegen (MATLAB Coder)を参照してください。

関数をコーディングする際には、知っておく必要のある DPI コンポーネント生成のさまざまな側面を説明する 制限 に留意してください。これらの側面には、有効なデータ型、生成されるファイル、共有ライブラリのコンパイル方法などが含まれます。

この例では、MATLAB 関数 fun.m は単一の入力を受け取り、それを 2 倍にします。この関数にはコンパイル ディレクティブ %#codegen が含まれています。

function y = fun(x) %#codegen y = x * 2;

MATLAB を作成するプロセスには、コードの記述、テストベンチの作成、反復プロセスでのテストベンチの実行が含まれます。関数が意図したとおりに動作することを確認したら、SystemVerilog DPIコンポーネントを生成する に進みます。

テストベンチの作成

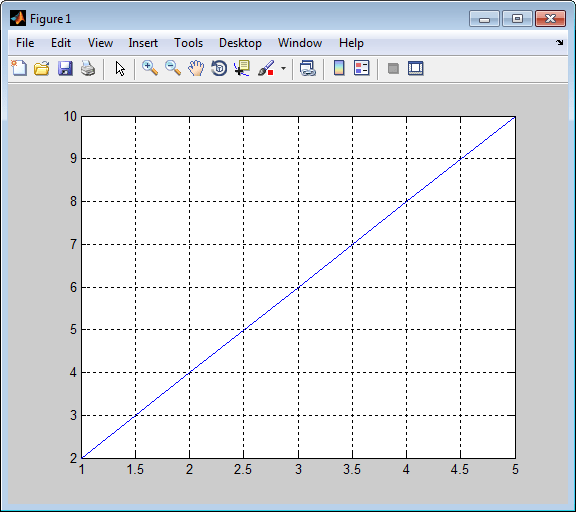

機能を実行するためのテストベンチを作成します。この例では、テストベンチは fun.m に対してテスト ベクトルを適用し、出力をプロットします。

function sample=fun_tb % Testbench should not require input, however you can give an output. % Define a test vector tVecIn = [1,2,3,4,5]; % Exercise fun.m and plot results to make sure function is working correctly tVecOut = arrayfun(@(in) fun(in),tVecIn); plot(tVecIn,tVecOut); grid on; % Get my sample input to use it with function dpigen. sample = tVecIn(1);

テストベンチには入力がないことに注意します。テストベンチは、MAT ファイルまたはその他のデータ ファイルを使用してテスト ベクトルをロードできるため、入力は必要ありません。

fun_tb の出力である sample は、dpigen の呼び出し中に fun.m の関数入力引数として使用されるので、単一の要素になります。SystemVerilog DPIコンポーネントを生成するを参照してください。

テストベンチを実行する

fun_tb

ans =

1

次に、SystemVerilog DPI コンポーネントを生成します。SystemVerilog DPIコンポーネントを生成するを参照してください。

SystemVerilog DPIコンポーネントを生成する

dpigen 関数を使用して DPI コンポーネントを生成する

DPI コンポーネントを生成するには、関数 dpigen を使用します。この関数にはいくつかのオプションの入力引数があります。少なくとも、コンポーネントを生成する MATLAB 関数と関数入力を指定します。生成されたコンポーネントを実行するためのテストベンチも生成する場合は、-testbench オプションを使用します。

dpigen func -args input_arg -testbench test_bench_name

関数の要件に応じて入力を定義します。この例では、

sampleは double 型のスカラー値です。sample = 1;

DPI コンポーネント ジェネレーター関数を呼び出します。

dpigen fun -args sample -testbench fun_tb

示されているように発行されたコマンドは、次のタスクを実行します。

関数

fun.mの SystemVerilog コンポーネントであるfun_dpi.svを生成します。fun.mの関数入力は sample で指定されます。SystemVerilog パッケージ ファイルである

fun_dpi_pkg.svを生成します。このファイルには、インポートされたすべての関数宣言が含まれています。生成されたコンポーネントのテストベンチを作成します。

この

dpigenの呼び出しに対して、MATLAB は次のメッセージを出力します。### Generating DPI Wrapper fun_dpi.c ### Generating DPI Wrapper header file fun_dpi.h ### Generating SystemVerilog module package fun_dpi_pkg.sv ### Generating SystemVerilog module fun_dpi.sv ### Generating makefiles for: fun_dpi ### Compiling the DPI Component ### Generating SystemVerilog test bench fun_tb.sv ### Generating test bench simulation script for Mentor Graphics QuestaSim/Modelsim run_tb_mq.do ### Generating test bench simulation script for Cadence Incisive run_tb_incisive.sh ### Generating test bench simulation script for Cadence Xcelium run_tb_xcelium.sh ### Generating test bench simulation script for Synopsys VCS run_tb_vcs.sh ### Generating test bench simulation script for Vivado Simulator run_tb_vivado.bat

前の例に示した関数は、次のフォルダーとファイルを生成します。

生成されたパッケージファイルを調べる

生成されたパッケージ ファイルを調べます。initialize、reset、terminate、fun 関数の宣言に注意してください。

この例では、fun_dpi_pkg.sv 用に生成されたコードを示します。

// File: C:\fun_example\codegen\dll\fun\fun_dpi_pkg.sv // Created: 2017-12-19 09:18:00 // Generated by MATLAB 9.5 and HDL Verifier 5.4 `timescale 1ns / 1ns package fun_dpi_pkg; // Declare imported C functions import "DPI" function chandle DPI_fun_initialize(input chandle existhandle); import "DPI" function chandle DPI_fun_reset(input chandle objhandle,input real x,output real y); import "DPI" function void DPI_fun(input chandle objhandle,input real x,output real y); import "DPI" function void DPI_fun_terminate(input chandle existhandle); endpackage : fun_dpi_pkg

生成されたコンポーネントを調べる

生成されたコンポーネントを調べて、dpigen 関数が MATLAB コードを SystemVerilog コードに変換する方法を理解します。関数に含まれる内容の詳細については、生成された SystemVerilog ラッパー を参照してください。

この例では、fun_dpi.sv 用に生成されたコードを示します。

// File: C:\fun_example\codegen\dll\fun\fun_dpi.sv

// Created: 2017-12-19 09:18:00

// Generated by MATLAB 9.5 and HDL Verifier 5.4

`timescale 1ns / 1ns

import fun_dpi_pkg::*;

module fun_dpi(

input bit clk,

input bit clk_enable,

input bit reset,

input real x,

output real y

);

chandle objhandle=null;

real y_temp;

initial begin

objhandle=DPI_fun_initialize(objhandle);

end

final begin

DPI_fun_terminate(objhandle);

end

always @(posedge clk or posedge reset) begin

if(reset== 1'b1) begin

objhandle=DPI_fun_reset(objhandle,x,y_temp);

y<=y_temp;

end

else if(clk_enable) begin

DPI_fun(objhandle,x,y_temp);

y<=y_temp;

end

end

endmodule生成されたテストベンチを調べる

生成されたテスト ベンチを調べて、関数 dpigen が MATLAB コードからこのテスト ベンチをどのように作成したかを確認します。生成されたテストベンチの詳細については、生成されたテストベンチ を参照してください。

この例では、fun_tb.sv 用に生成されたコードを示します。

// File: C:\fun_example\codegen\dll\fun\dpi_tb\fun_tb.sv

// Created: 2017-12-19 09:18:13

// Generated by MATLAB 9.5 and HDL Verifier 5.4

`timescale 1ns / 1ns

module fun_tb;

real x;

real y_ref;

real y_read;

real y;

// File Handles

integer fid_x;

integer fid_y;

// Other test bench variables

bit clk;

bit clk_enable;

bit reset;

integer fscanf_status;

reg testFailure;

reg tbDone;

bit[63:0] real_bit64;

bit[31:0] shortreal_bit64;

parameter CLOCK_PERIOD= 10;

parameter CLOCK_HOLD= 2;

parameter RESET_LEN= 2*CLOCK_PERIOD+CLOCK_HOLD;

// Initialize variables

initial begin

clk = 1;

clk_enable = 0;

testFailure = 0;

tbDone = 0;

reset = 1;

fid_x = $fopen("dpig_in1.dat","r");

fid_y = $fopen("dpig_out1.dat","r");

// Initialize multirate counters

#RESET_LEN reset = 0;

end

// Clock

always #(CLOCK_PERIOD/2) clk = ~ clk;

always@(posedge clk) begin

if (reset == 0) begin

#CLOCK_HOLD

clk_enable <= 1;

fscanf_status = $fscanf(fid_x, "%h", real_bit64);

x = $bitstoreal(real_bit64);

if ($feof(fid_x))

tbDone = 1;

fscanf_status = $fscanf(fid_y, "%h", real_bit64);

y_read = $bitstoreal(real_bit64);

if ($feof(fid_y))

tbDone = 1;

y_ref <= y_read;

if (clk_enable == 1) begin

assert ( ((y_ref - y) < 2.22045e-16) && ((y_ref - y) > -2.22045e-16) ) else begin

testFailure = 1;

$display("ERROR in output y_ref at time %0t :", $time);

$display("Expected %e; Actual %e; Difference %e", y_ref, y, y_ref-y);

end

if (tbDone == 1) begin

if (testFailure == 0)

$display("**************TEST COMPLETED (PASSED)**************");

else

$display("**************TEST COMPLETED (FAILED)**************");

$finish;

end

end

end

end

// Instantiate DUT

fun_dpi u_fun_dpi(

.clk(clk),

.clk_enable(clk_enable),

.reset(reset),

.x(x),

.y(y)

);

endmodule

次に、生成されたテストベンチを HDL シミュレーターで実行します。生成されたテストベンチをHDLシミュレータで実行するを参照してください。コンポーネントとオプションのテストベンチを Windows® から Linux® に移植する予定の場合は、生成されたコンポーネントとテストベンチをLinuxに移植する を参照してください。

生成されたテストベンチをHDLシミュレータで実行する

このセクションには、サポートされている HDL シミュレーター (Mentor Graphics® ModelSim®、Questa®、Cadence® Xcelium™、Synopsys® VCS®) のいずれかで生成されたテストベンチを実行する手順が記載されています。このコードは他の (サポートされていない) HDL シミュレータでも動作する可能性がありますが、保証されません。

HDL シミュレータのワークフローを選択します。

ModelSim および Questa シミュレータでテストベンチを実行する

GUI モードで ModelSim または Questa を起動します。

現在のディレクトリを、MATLAB のコード生成ディレクトリの下の

dpi_tbフォルダーに変更します。シミュレーションを開始するには、シェルに次のコマンドを入力します。

do run_tb_mq.do

この生成されたスクリプトには、コンポーネントとテストベンチの名前、およびテストベンチを実行するための HDL シミュレータへの指示が含まれています。

シミュレーションが終了すると、コンソールに次のテキストが表示されます。

**************TEST COMPLETED (PASSED)**************

このメッセージは、生成されたコンポーネントに対してテストベンチが正常に実行されたことを示します。

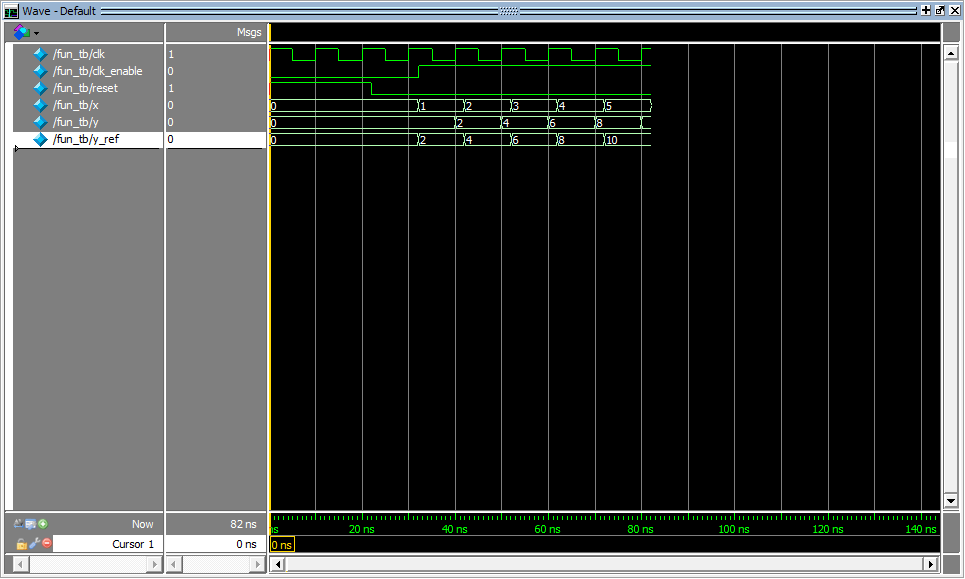

この例の次の波形イメージは、生成されたテストベンチが HDL シミュレータで正常に実行されたことを示しています。

次に、コンポーネントをインポートします。SystemVerilog で生成された DPI 関数を使用するを参照してください。

Xcelium シミュレータでテストベンチを実行する

Xcelium を起動します。

ターミナル シェルを起動します。

現在のディレクトリを、MATLAB のコード生成ディレクトリの下の

dpi_tbに変更します。シミュレーションを開始するには、シェルに次のコマンドを入力します。

sh run_tb_ncsim.sh

この生成されたスクリプトには、コンポーネントとテストベンチの名前、およびテストベンチを実行するための HDL シミュレータへの指示が含まれています。

シミュレーションが終了すると、コンソールに次のテキストが表示されます。

**************TEST COMPLETED (PASSED)**************

このメッセージは、生成されたコンポーネントに対してテストベンチが正常に実行されたことを示します。

VCS シミュレータでテストベンチを実行する

VCS を起動します。

ターミナル シェルを起動します。

現在のディレクトリを、MATLAB のコード生成ディレクトリの下の

dpi_tbに変更します。シミュレーションを開始するには、シェルに次のコマンドを入力します。

sh run_tb_vcs.sh

この生成されたスクリプトには、コンポーネントとテストベンチの名前、およびテストベンチを実行するための HDL シミュレータへの指示が含まれています。

シミュレーションが終了すると、コンソールに次のテキストが表示されます。

**************TEST COMPLETED (PASSED)**************

このメッセージは、生成されたコンポーネントに対してテストベンチが正常に実行されたことを示します。

SystemVerilog で生成された DPI 関数を使用する

生成された DPI コンポーネントを SystemVerilog テストベンチで使用するには、まずパッケージ ファイルを SystemVerilog 環境に含める必要があります。これにより、SystemVerilog モジュールの範囲内で DPI 関数が使用できるようになります。次に、生成された関数を呼び出す必要があります。インポートされた生成関数を含む SystemVerilog コードをコンパイルするときは、DPI 対応の SystemVerilog コンパイラを使用し、SystemVerilog コードとともにコンポーネントおよびパッケージ ファイル名を指定します。

次の例は、fun.m 用に生成された DPI コンポーネントを SystemVerilog モジュールに追加する方法を示しています。

関数

Initializeを呼び出します。DPI_fun_initialize();

fun.mから生成された関数を呼び出します。DPI_fun(x,y);

生成されたコードを必要に応じて変更できます。

例

module test_twofun_tb; initial begin DPI_fun_initialize(); end always@(posedge clk) begin #1 DPI_fun(x,y); end

生成されたコンポーネントとテストベンチをLinuxに移植する

コンポーネントとオプションのテストベンチを Windows オペレーティング システムから Linux オペレーティング システムに移植するには、HDL シミュレータに基づいて次のいずれかのワークフローに従います。

メモ

コンポーネントを Windows から Linux に移植するには、Embedded Coder® ライセンスが必要です。

汎用 DPI コンポーネントを生成する

サポートされているすべての HDL シミュレーターに対してこのワークフローに従ってください。このソフトウェアは、Mentor Graphics ModelSim、Mentor Graphics Questa、Cadence Xcelium、および Synopsys VCS シミュレータをサポートしています。サポートされているすべての HDL シミュレータに汎用的な DPI コンポーネントを生成します。

Windows ホストマシン上のタスク

coder.config(MATLAB Coder) オブジェクトを作成します。Linux オペレーティング システムのターゲット HW デバイス タイプをLP64に変更します。cfg=coder.config('dll');cfg.HardwareImplementation.TargetHWDeviceType='Generic->64-bit Embedded Processor (LP64)';

手順 1 で作成した

configオブジェクトを使用するには、オプション-configを使用してdpigen関数を実行します。dpigen関数がコードのみを生成するように、オプション-cを使用します。dpigen -config cfg DataTypes.m -args InputSample -c

Linux に移植する zip アーカイブを生成し、

buildInfoファイルを含むソース フォルダーに移動して、MATLAB コマンド プロンプトで次のコマンドを実行します。load buildInfo packNGo(buildInfo)

最上位のフォルダに移動します。手順 3 で生成した、MATLAB 関数と同じ名前の ZIP アーカイブを見つけます。ZIP アーカイブを Linux マシンにコピーします。

Linux ターゲット マシン上のタスク

-jオプションを使用してファイルを解凍し、フラット化されたフォルダー構造を持つすべてのファイルを抽出します。内容を任意のフォルダに解凍できます。unzip -j DataTypes.zip

この汎用 makefile スクリプトを空のファイルにコピーします。

SRC=$(wildcard *.c) OBJ=$(SRC:.c=.o) SHARE_LIB_NAME=DPI_Component.so all: $(SRC) $(SHARE_LIB_NAME) @echo "### Successfully generated all binary outputs." $(SHARE_LIB_NAME): $(OBJ) gcc -shared -lm $(OBJ) -o $@ .c.o: gcc -c -fPIC -Wall -pedantic -Wno-long-long -fwrapv -O0 $< -o $@

DPI_Component.soを、作成する共有ライブラリの名前に置き換えます。スクリプトを、zip ファイルが格納されているフォルダーに

Porting_DPIC.mkとして保存します。

共有ライブラリを構築します。

make -f Porting_DPIC.mk all

生成されたコンポーネントを SystemVerilog で使用するには、SystemVerilog で生成された DPI 関数を使用する を参照してください。

(オプション) Windows でソフトウェアによって生成されたテストベンチを実行します。

dpi_tbフォルダの内容を Windows ホスト マシンから Linux ターゲット マシンにコピーします。テストベンチを実行します。

HDL シミュレーターでテストベンチを実行するには、生成されたテストベンチをHDLシミュレータで実行する を参照してください。

シミュレータ固有のDPIコンポーネントを生成する

Mentor Graphics ModelSim、Mentor Graphics Questa、Cadence Xcelium、Synopsys VCS、Xilinx® Vivado® HDL シミュレータの場合は、このワークフローに従ってください。選択したシミュレータの DPI コンポーネントを生成します。

移植手順を簡単にするには、このワークフローを使用します。このワークフローを使用する場合、生成されたコンポーネントを使用するために、汎用の makefile スクリプトを作成し、Linux ターゲット マシン上で共有ライブラリをビルドする必要はありません。生成されたコンポーネントを実行するためにテストベンチを生成する場合、Windows ホスト マシンから Linux ターゲット マシンにテストベンチ フォルダーを個別にコピーする必要はありません。

Windows ホストマシン上のタスク

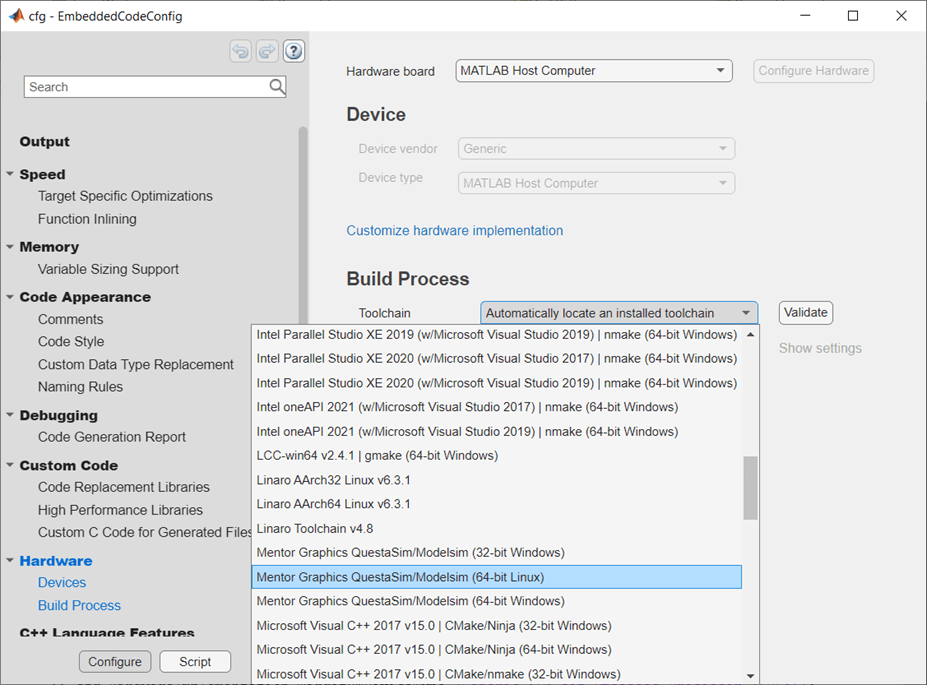

coder.config(MATLAB Coder) オブジェクトを作成します。cfg=coder.config('dll');手順 1 で作成した

coder.configオブジェクトを構成して、ターゲット シミュレーターとオペレーティング システムを選択します。MATLAB ワークスペースで、cfgをダブルクリックして、cfgの EmbeddedCodeConfig ダイアログを開きます。Hardware ペインの Build Process の下で、ターゲット Toolchain を選択します。このオプションは、シミュレーションを実行するターゲット シミュレーターとオペレーティング システムを指定します。サポートされているクロスプロダクト ツールチェーンは次のとおりです。Cadence Xcelium (64-bit Linux)Mentor Graphics ModelSim/QuestaSim (64-bit Linux)Synopsys VCS (64-bit Linux)Xilinx Vivado Simulator (64-bit Linux)

configオブジェクトを使用するには、-configオプションを使用してdpigen関数を実行します。生成されたコンポーネントを実行するためのテストベンチも生成する場合は、-testbenchオプションを使用します。dpigen関数がコードのみを生成するように、-cオプションを使用します。dpigen -config cfg DataTypes.m -args InputSample -testbench DataTypes_tb.m -c

Linux に移植するための ZIP アーカイブを生成し、

buildInfoファイルが含まれているソース フォルダーに移動します。load buildInfo

packNGo(MATLAB Coder) 関数を使用して、生成されたファイルと必要な依存関係をパッケージ化してから、ターゲット マシンにコピーします。引数'minimalHeaders',falseを指定して、ZIP アーカイブのインクルード パスにあるすべてのヘッダー ファイルを含めます。packNGo(buildInfo,'minimalHeaders',false)

最上位のフォルダに移動します。手順 3 で生成した、MATLAB 関数と同じ名前の ZIP アーカイブを見つけます。ZIP アーカイブを Linux マシンにコピーします。ZIP アーカイブには、拡張子が

.doの ModelSim ファイル、または拡張子が.shの Xcelium、VCS、または Vivado ファイルが含まれています。

Linux ターゲット マシン上のタスク

ファイルを任意のフォルダに解凍します。

unzip DataTypes.zip

HDL シミュレータを起動します。

手順 1 で解凍した生成されたファイルが含まれているフォルダーに移動します。

VCS シミュレータのみ:シミュレータ環境パスを設定します。コマンドを実行するときは、独自の Synopsys VCS インストール パスを使用してください。

ここで、set VCS_HOME = C:/Synopsys/temp/vcs/S-2021.09-1

VCS_HOMEは環境変数の名前です。プロジェクトをビルドし、HDL シミュレーターでテストベンチを実行します。

ModelSim および Questa シミュレータの場合は、次のコマンドを実行します。

do DataTypes.do do run_tb_mq.do

Xcelium、VCS、および Vivado シミュレータの場合は、次のコマンドを実行します。コマンドを実行するときは、

simulatorsh DataTypes.sh sh run_tb_simulator.sh %Replace

simulator

制限

VCS および Vivado シミュレータの場合、クロスプラットフォーム DPI 生成は可変サイズのベクトルをサポートしません。

Vivado シミュレータの場合、DPI コンポーネント生成では

singleおよびdoubleデータ型はサポートされません。