このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

MATLAB による DPI コンポーネント生成に関する考慮事項

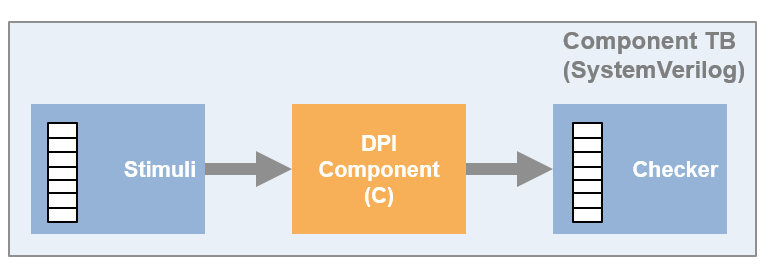

MATLAB® 関数を、SystemVerilog シミュレーションで使用するために、ダイレクト プログラミング インターフェイス (DPI) を持つコンポーネントとしてエクスポートできます。HDL Verifier™ は、生成された C コードを、SystemVerilog シミュレーションで SystemVerilog シン インターフェイス関数と通信する DPI ラッパーでラップします。

MATLAB の場合、dpigen 関数を使用してコンポーネントを生成します。

メモ

この機能にはMATLAB Coder™ライセンスとASIC Testbench for HDL Verifierアドオンが必要です

サポートされているMATLABデータ型

サポートされている MATLAB データ型は、この表に示すように SystemVerilog データ型に変換されます。dpigen 関数を使用する場合は、PortsDataType プロパティを使用して Compatible C type、Logic vector、または Bit vector データ型を選択します。

生成された SystemVerilog 型

| MATLAB | SystemVerilog | ||

|---|---|---|---|

| 互換Cタイプ | ロジックベクトル | ビットベクター | |

uint8 | byte unsigned | logic [7:0] | bit [7:0] |

uint16 | shortint unsigned | logic [15:0] | bit [15:0] |

uint32 | int unsigned | logic [31:0] | bit [31:0] |

uint64 | longint unsigned | logic [63:0] | bit [63:0] |

int8 | byte | logic signed [7:0] | bit signed [7:0] |

int16 | shortint | logic signed [15:0] | bit signed [15:0] |

int32 | int | logic signed [31:0] | bit signed [31:0] |

int64 | longint | logic signed [63:0] | bit signed [63:0] |

logical | byte unsigned | logic [0:0] | bit [0:0] |

fi (固定小数点データ型) | 固定小数点ワード長に依存します。固定小数点ワード長がホスト ワード サイズより大きい場合 (たとえば、64 ビット対 32 ビット)、このデータ型は MATLAB Coder によって SystemVerilog データ型に変換できず、エラーが発生します。固定小数点ワード長がホストワードサイズ以下の場合、MATLAB Coder は固定小数点データ型を組み込み C 型に変換します。 |

論理ベクトルの長さ ( |

ビットベクトルの長さ ( |

single | shortreal | ||

double | real | ||

complex | コーダは、SystemVerilog コンポーネント内の複素信号を実数部と虚数部に平坦化します。 | ||

| ベクトル、行列 | 配列 たとえば、MATLAB の 4 行 2 列の行列は、SystemVerilog では 8 要素の 1 次元配列に変換されます。デフォルトでは、コーダは列優先の順序で行列をフラット化します。行優先順序に変更するには、 | ||

structure | コーダは、構造要素を SystemVerilog コンポーネント内の個別のポートにフラット化します。 | ||

| 列挙データ型 | enum | ||

生成された共有ライブラリ

関数 dpigen は、エクスポートされた DPI コンポーネントを SystemVerilog 環境で実行するために必要な共有ライブラリを自動的にコンパイルします。共有ライブラリを構築する makefile の拡張子は _rtw.mk です。たとえば、fun.m の場合、メイクファイル名は fun_rtw.mk になります。

コンパイル中に、関数 dpigen によってライブラリ ファイルが生成されます。

Windows® 64:

function_win64.dllLinux®:

function.so

function は、DPI コンポーネントを生成した MATLAB 関数の名前です。

メモ

Windows で 64 ビットの MATLAB を使用すると、64 ビットの DLL が生成されますが、これは 64 ビット HDL シミュレーターでのみ使用できます。

MATLAB のバージョンが HDL シミュレータのバージョンと一致していることを確認してください。

生成されたテストベンチ

関数 dpigen もテストベンチを作成します。このテスト ベンチを使用すると、生成された SystemVerilog コンポーネントが元の MATLAB 関数と機能的に同等であることを確認できます。ジェネレーターは MATLAB コードを実行して、テスト ベンチで使用するための入力および出力データ ベクトルを保存します。このテスト ベンチは、独自のアプリケーション用のシステム テスト ベンチの代わりとして使用することを意図したものではありません。ただし、独自のシステム テスト ベンチを作成するときは、生成されたテスト ベンチを開始例として使用できます。

生成された出力

MATLAB Coder によって生成されたアルゴリズムの C およびヘッダー ファイル

HDL Verifier によって生成された DPI ラッパーの C およびヘッダー ファイル

コンポーネントを公開し、制御信号を追加するSystemVerilogファイル

DPIコンポーネントのすべての関数宣言を含むSystemVerilogパッケージファイル

SystemVerilog テストベンチ (

-testbenchオプション付き)HDL シミュレータで使用されるデータ ファイル (

-testbenchオプションを使用)*.doや*.sh(-testbenchオプション付き) などの HDL シミュレータ スクリプトメイクファイル

*.mk

生成された SystemVerilog ラッパー

生成された制御信号

関数 dpigen によってシーケンシャル関数用に生成された SystemVerilog コードには、一連の制御信号が含まれています。

clk: 同期クロックclk_enable: クロック有効化reset: 非同期リセット

組み合わせ設計用の SystemVerilog を生成する場合、生成されたコードには上記の制御信号が含まれません。dpigen 関数の ComponentTemplateType 引数を使用して、順次または組み合わせを指定します。

生成された初期化関数

dpigen 関数によって生成されるすべての SystemVerilog コードには、Initialize 関数が含まれます。Initialize 関数はシミュレーションの開始時に呼び出されます。

次に例を示します。

import "DPI" function void DPI_Subsystem_initialize();

非同期リセット信号がハイ(0 から 1 になる)の場合、Initialize が再度呼び出されます。

シミュレーションの考慮事項

HDL 環境で DPI コンポーネントをシミュレートする場合、reset、clock、および clk_enable は次のように動作します。

制限

システムのワード長を超える大きな固定小数点数はサポートされていません。

定数の折りたたみなどの一部の最適化は、生成された C 関数のインターフェースを変更するため、サポートされていません。詳細については、生成コードの MATLAB Coder の最適化 (MATLAB Coder)を参照してください。

HDL Verifier は、SystemVerilog で行列とベクトルを 1 次元配列に制限します。たとえば、MATLAB の 4 行 2 列の行列は、SystemVerilog では 8 要素の 1 次元配列に変換されます。

構成オブジェクト内の

PostCodegenコールバックはサポートされていません。