このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

FPGA 用のプログラム可能な FIR フィルター

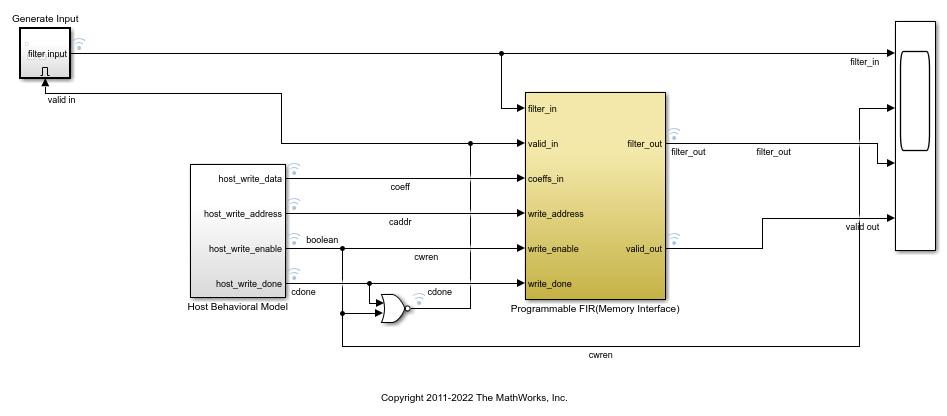

この例では、ハードウェア用のプログラム可能な FIR フィルターを実装する方法を示します。メモリ形式のインターフェイスを使用して内部レジスタに係数を読み込むことで、必要な応答に対するフィルターをプログラムできます。

この例では、それぞれが異なる応答をもつ 2 つのフィルターのバンクを実装します。係数の長さと対称性は両方のフィルターで同じです。この係数のパターンにより、どちらのフィルターでも同じ方法で対称係数の乗算器をブロックで共有できます。同じフィルター ハードウェアを新しい係数でプログラムすることで別のフィルター応答を取得できます。

プログラム可能な FIR フィルターのモデル化

この例では、一方はローパス応答をもち、もう一方はハイパス応答をもつ、2 つの FIR フィルターを実装します。係数は、[モデル プロパティ]、[コールバック]、[InitFcn] 関数で指定されます。

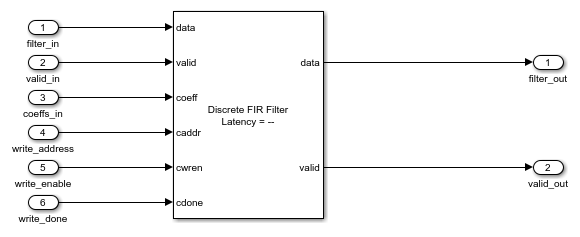

Programmable FIR(Memory Interface) サブシステムにある Discrete FIR Filter ブロックで、[Coefficients source] パラメーターが Input port (Memory interface) に設定されています。この構成により、メモリ形式の端子セットによるフィルターへの係数の書き込みが可能になります。最初に、Host Behavioral Model サブシステムはローパス係数を FIR フィルターに読み込みます。モデルは、最初の係数の書き込みが完了するまで入力チャープ サンプルを遅延させます。その後、Host Behavioral Model サブシステムはハイパス係数を読み込みます。

フィルターに係数を書き込んでいる間は、すべての入力データ サンプルがフィルターで無視されます。このモデルは、係数の変更中は入力データの送信を停止します。出力 Valid 信号を使用して出力データが有効になるタイミングを決定することもできます。

このモデルの Discrete FIR Filter ブロックは、完全なパラレルの直接型シストリック アーキテクチャを使用するように構成されています。ブロックでパラレルの転置アーキテクチャやシリアル アーキテクチャを使用する場合は、メモリ形式のプログラム可能な係数の使用もブロックでサポートされます。[Coefficient prototype] パラメーターは係数ベクトルのいずれかに設定されます。この設定により、ブロックでゼロ値の係数の対称性と位置に基づいてハードウェア リソースを最適化できます。プロトタイプを指定する場合は、ゼロ値の係数の対称性と位置について、すべての入力係数のセットがプロトタイプと一致しなければなりません。プロトタイプを使用してフィルター リソースを最適化する方法の詳細については、Optimize Programmable FIR Filter Resources (DSP HDL Toolbox)を参照してください。

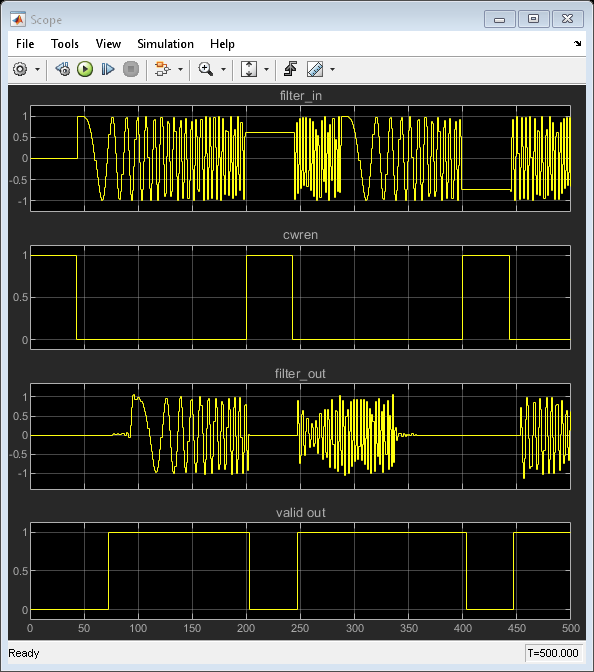

Simulink のシミュレーション結果

係数インターフェイスの入出力データと信号を表示するには、スコープを開いてモデル例を実行します。

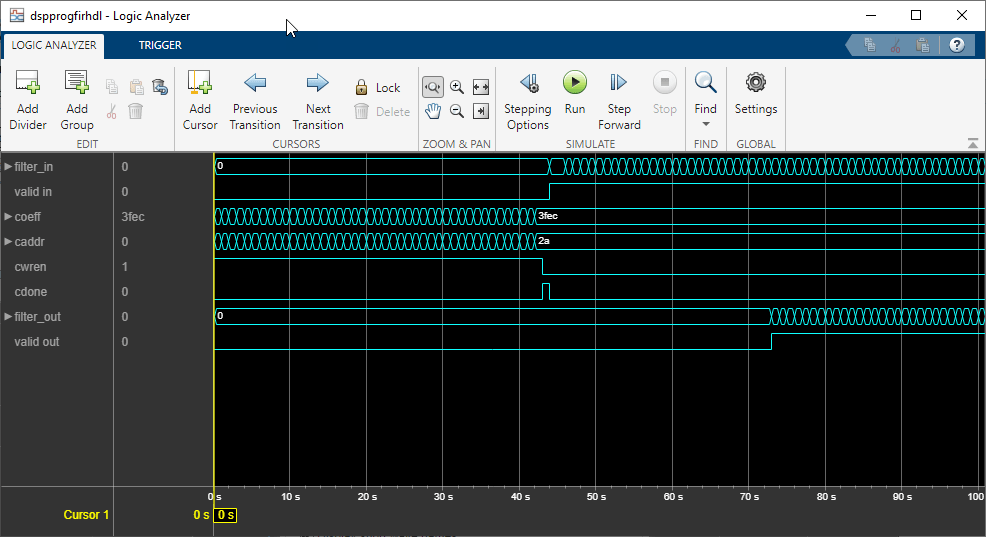

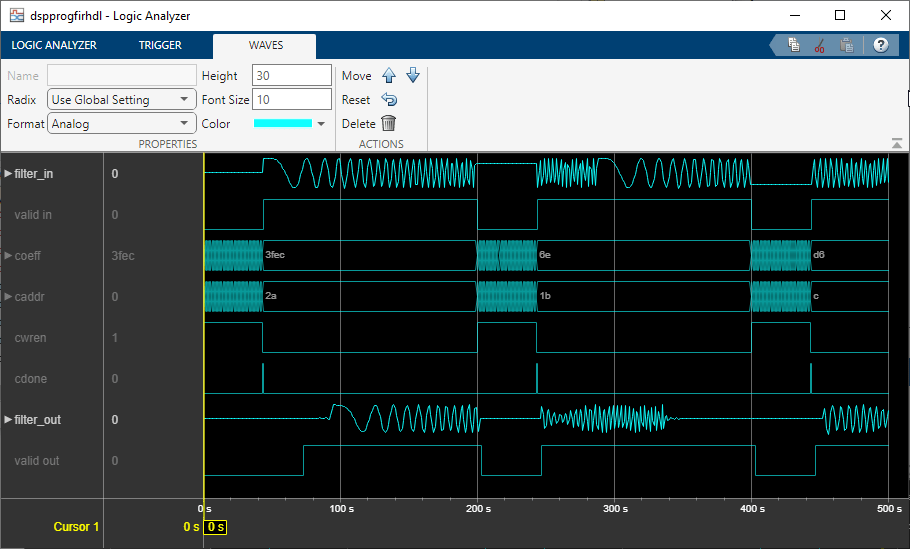

ロジック アナライザーの使用

ロジック アナライザーでモデルから信号を表示することもできます。ロジック アナライザーでは、複数の信号を 1 つのウィンドウで表示して、信号の遷移を見つけたり、信号間のレイテンシを測定したりできます。

モデルのツールストリップからロジック アナライザーを起動します。

モデルのいくつかの対象の信号 (入力係数、書き込みアドレス、書き込みイネーブル、書き込み完了、フィルター入力、フィルター出力、および Valid 信号) が観測用にロジック アナライザーに既に追加されています。

ロジック アナライザーの表示を波形単位またはデバイダー単位で制御することもできます。個々の波形またはデバイダーを変更するには、波形またはデバイダーを選択し、[波形] タブをクリックします。ロジック アナライザーの可視化モードの Analog 形式が便利です。

詳細については、ロジック アナライザー (DSP System Toolbox)を参照してください。

HDL コードとテスト ベンチの生成

このモデル例の HDL コードを生成するには、HDL Coder™ のライセンスが必要です。HDL コードを生成するには、次のコマンドを使用します。

systemname = [modelname '/Programmable FIR(Memory Interface)'];

makehdl(systemname);

HDL シミュレーションの結果を Simulink のシミュレーション動作に対して比較するテスト ベンチを生成するには、次のコマンドを使用します。

makehdltb(systemname);