既存テスト ケースの定義および拡張

この例では、Simulink® Design Verifier™ でタイム ステップを追加してテスト ケースを拡張し、完全なテスト スイートを効率的に生成する方法を説明します。

この例では、テストの生成が難しい、時間遅延の特性をもつモデルを使用します。既定のテスト ハーネス モデルを作成し、1 つのテストを手動で作成することで、効率的なテスト生成に対するクリティカルな障害は取り除かれます。Simulink Design Verifier は、ハーネス モデルからログを取った値を入力として使用し、このテストを効率的に拡張して完全なテスト スイートを作成します。

テスト ケースの拡張が必要になるモデルの特性

sldvdemo_sbr_extend_design モデルは、Stateflow® チャート SBR を含み、これは KEY_OFF ステートから KEY_ON ステートへの遷移に非常に長いテスト ケースを必要とする時相論理を使用します。この種の時間遅延特性は、不要波の動作の排除や物理システムまたはユーザーの応答の待機に遅延が使用されている設計では一般的です。この設計では、この遷移で時相論理を満たすことが、KEY_ON ステートにおける任意のステートと遷移をテストするための共通の障害になります。

この種の時間遅延特性は、多くの場合、手動で作成されたテスト ケースで簡単に特定して満たすことができます。

open_system('sldvdemo_sbr_extend_design'); sf('Open',sldvdemo_ssid_to_sfid('sldvdemo_sbr_extend_design/SBR',11));

ハーネス モデルの作成および開始テストの定義

Simulink Design Verifier 関数sldvmakeharnessは、テスト モデルへの入力値を生成するブロックをもつハーネス モデルを作成します。このテスト モデルは、Model ブロックを経由して含まれます。

この例では、システムを 5 秒間、KEY_OFF ステートにするテスト ケースを指定します。

[~, harnessModelFilePath] = sldvmakeharness('sldvdemo_sbr_extend_design',[],[],true); [~, harnessModel] = fileparts(harnessModelFilePath); sigEditorBlk = [harnessModel '/Inputs']; fileName = get_param(sigEditorBlk, 'FileName'); tcData = load(fileName); % Prepare a test case of length 5 seconds TemporalTestCase = tcData.TestCase_1; TemporalTestCase{1}.Values.Speed = timeseries(fi(zeros(2,1), 0, 16, 2), [0;5], 'Name', 'Speed'); TemporalTestCase{1}.Values.SeatBeltFasten = timeseries(false(2,1), [0;5], 'Name', 'SeatBeltFasten'); TemporalTestCase{1}.Values.KEY = timeseries(zeros(2,1,'int8'), [0;5], 'Name', 'SeatBeltFasten'); save(fileName, 'TemporalTestCase'); % Set TemporalTestCase as active scenario set_param(sigEditorBlk, 'ActiveScenario', 'TemporalTestCase');

開始テストのログ

上記で定義された開始テスト ケースを活用するために、関数sldvlogsignalsを使用して必要なログ データ形式で入力値をキャプチャします。

sldvlogsignals の最初の入力は、Model ブロックのパスです。2 番目の入力は、ハーネス モデル内の信号グループのインデックスです。sldvlogsignals を呼び出すと、Model ブロックを含む親モデルのシミュレーションが実行されます。

親モデルは Simulink Design Verifier ハーネス モデルに限定されません。別の方法として、コントローラーのテスト ケースが閉ループ システムで想定される連続時間の動作をより現実的に反映することができるように、Model ブロックを使用してコントローラーを含める閉ループ シミュレーション モデルからデータのログを作成することもできます。

[~, modelBlock] = find_mdlrefs(harnessModel, false);

loggeddata = sldvlogsignals(modelBlock{1});

テスト生成時の既存のテストの拡張

テストの生成で既存のテスト データを使用する場合は、まずデータを MAT ファイルに保存しなければなりません。Simulink Design Verifier のコンフィギュレーション パラメーターの [テスト生成] ペインでテスト ケースの拡張を有効にします。[既存テスト ケースの拡張] を選択し、[データ ファイル] フィールドで MAT ファイルを指定します。

生成されたテストでは、いずれかの開始テスト ケースを 1 つ以上の新しいタイム ステップで拡張するか、初期または既定の構成から開始する 1 つ以上のタイム ステップを指定します。

save('existingtestcase.mat', 'loggeddata'); opts = sldvoptions; opts.ExtendExistingTests = 'on'; opts.ExistingTestFile = 'existingtestcase.mat'; opts.SaveHarnessModel = 'off'; opts.SaveReport = 'off'; [~, fileNames] = sldvrun('sldvdemo_sbr_extend_design', opts, true);

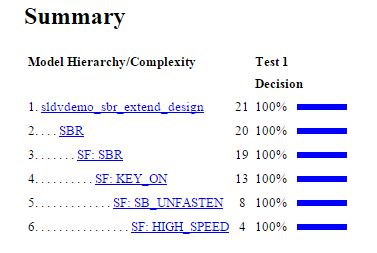

完全なカバレッジの検証

関数sldvruntestは、新しいテスト スイートがすべてのモデル カバレッジを達成することを検証します。関数cvhtml (Simulink Coverage)は、生成されたテスト ベクトルで 100% の判定カバレッジが達成されることを示すカバレッジ レポートを生成します。

[~, finalCov] = sldvruntest('sldvdemo_sbr_extend_design', fileNames.DataFile, [], true); cvhtml('Final Coverage', finalCov);

クリーン アップ

デモを完了するには、すべてのモデルを閉じて保存されたログ データ ファイルを削除します。

close_system(harnessModel,0); close_system('sldvdemo_sbr_extend_design'); delete('existingtestcase.mat');