外乱補償

線形システムの外乱と未知のダイナミクスを推定して補償する

入力と出力に基づいてプラントの状態と外乱を推定できる推定手法を使用します。

ブロック

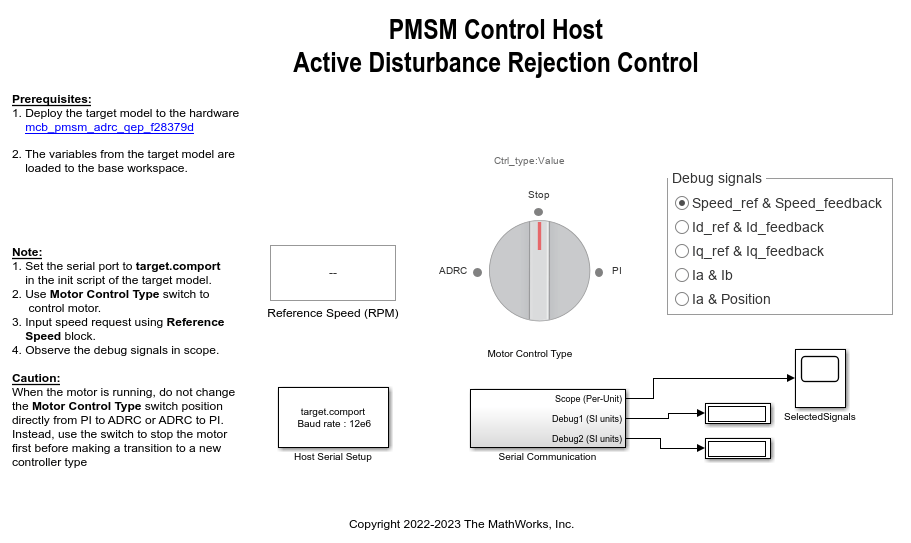

| Active Disturbance Rejection Control | 不明なダイナミクスおよび外乱があるプラント用のコントローラーを設計する (R2022b 以降) |

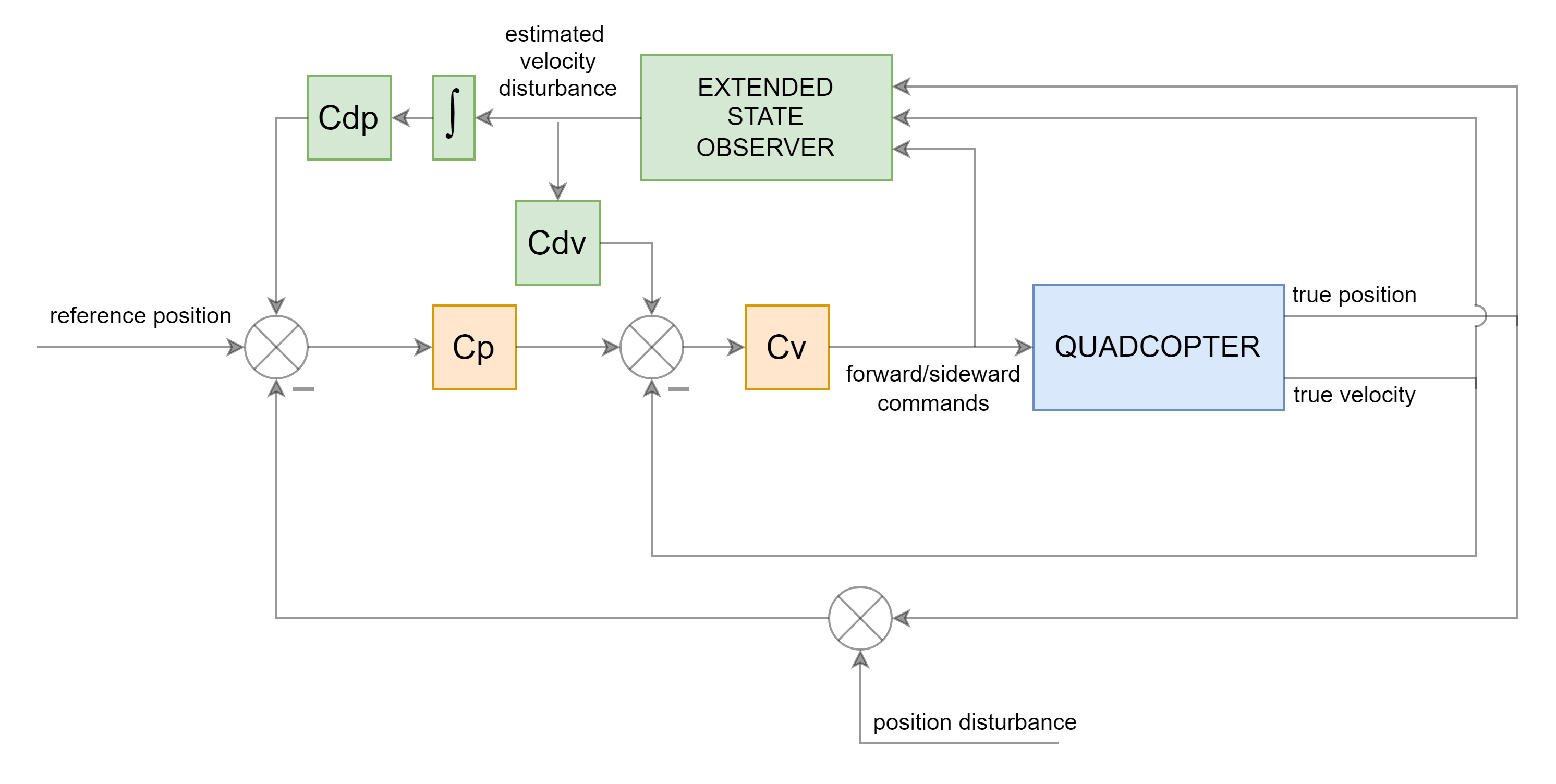

| Extended State Observer | Estimate states and disturbances of a system (R2024a 以降) |

| Disturbance Compensator | Modify control actions to compensate for unknown dynamics and disturbances (R2024a 以降) |

| Ultra Local Model | Estimate nonlinear plant as single or double integrator systems with an affine term that captures unknown dynamics and disturbances (R2025a 以降) |

トピック

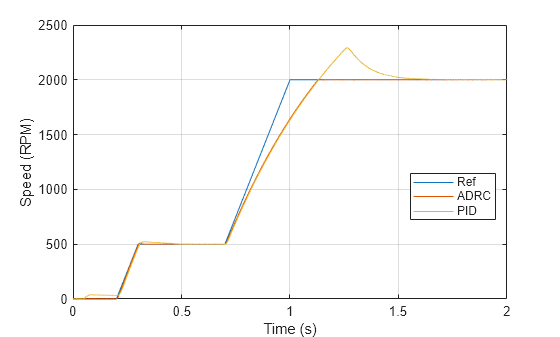

アクティブな外乱の抑制の制御

- アクティブな外乱の抑制の制御

ダイナミクスおよび外乱が不明なプラント用の外乱の抑制コントローラーを設計する。 - Design Active Disturbance Rejection Control for Water-Tank System

Design ADRC for a water-tank model and compare performance against a gain-scheduled PID controller. - Design ADRC for Multi-Input Multi-Output Plant

Design ADRC for a pilot-scale distillation column MIMO model and compare performance against a model predictive controller. (R2023b 以降)

外乱補償

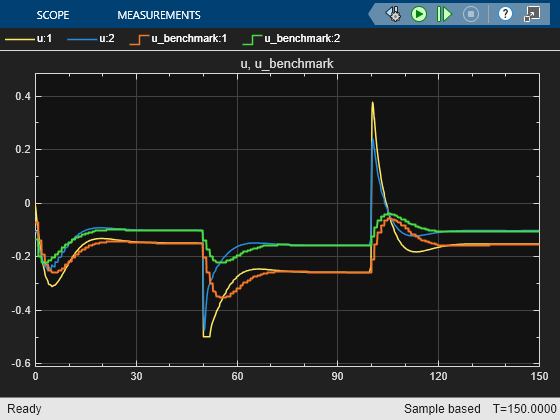

- Control Design and Disturbance Compensation Using Extended State Observers

Estimate and compensate for disturbances and unknown dynamics in linear time-invariant or linear time-varying systems. (R2024a 以降) - Apply Extended State Observer for Reference Tracking of DC Motor

Improve the disturbance rejection performance of a PID controller using the Extended State Observer block. (R2024a 以降) - Compensate for Disturbances in Spring-Mass-Damper System

Compensate for disturbances in a spring-mass-damper system using the Disturbance Compensator block. (R2024a 以降)

Ultra-Local Model

- Ultra-Local Model for Disturbance Estimation and Compensation

Estimate disturbances and unmodeled dynamics using ultra-local model. - Ultra-Local Model for System Identification and Output Prediction

Use the Ultra-Local Model block for system identification and output prediction. - Intelligent PID Using Ultra Local Model for Ball on Beam Balance

Implement model-free intelligent PID control technique using ultra-local model.

コード生成

- Deploy Controller for SEPIC Converter for PIL Testing

Set up processor in the loop (PIL) testing and profiling of an active disturbance rejection controller for a SEPIC converter. (R2024b 以降)