Zynq でのベクトル制御のマルチコア プログラミング

この例では、Zynq® 上の複数のレートを含む制御アルゴリズムの実装方法を示します。コアと FPGA ハードウェアの両方を活用するために、この例ではグラフィカルな分割方法を使用して、さまざまな分割からのコードがコアおよびハードウェア全体に配布されるようにします。

はじめに

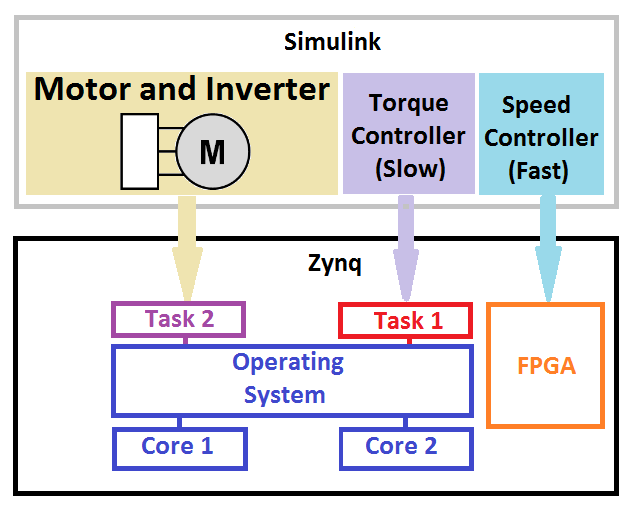

この例では、モーター制御アルゴリズム向けにコードを生成して、生成されたコードを Xilinx® Zynq-7000 SoC ZC702 評価ボード上でテストするワークフローを示します。この例のモーター制御アルゴリズムは、速度コントローラー (高速成分) およびトルク コントローラー (低速成分) から構成されるベクトル制御アルゴリズムです。ある典型的なワークフローとして、コントローラーのこれらの 2 つのコンポーネントのコードを生成し、生成されたコードを評価ボードにアップロードしてから、評価ボードを実際のモーターに接続します。ブロック線図でこのワークフローを示します。

この例を自己完結型にするため、また、ターゲット プロセッサのコンピューター能力に余裕があるため、この例では、評価ボードの CPU のタスクのいずれかを使用してモーターをモデル化します。

この例では、Xilinx Zynq-7000 SoC ZC702 評価ボードがコンピューターに接続されていると仮定します。接続およびインストールの詳細については、AMD SoC ボード用のサポートのインストール (Embedded Coder)を参照してください。

この例では、マルチスレッド コードの生成のために Embedded Coder® が必要であり、HDL コードの生成のために HDL Coder™ が必要です。また、この例で永久磁石同期機をモデル化するには Simscape™ Power Systems™ が必要です。HDL コードは Macintosh システムでは生成できません。

モデル例

モデル例は、2 つの Simulink® 領域から構成されます。永久磁石同期機の領域には、次の 2 つのブロックがあります。"Speed and Torque Inputs" ブロックはフィードバック システムへの参照入力を提供し、"Invertor and Motor" ブロックはこの例での制御を目的とするプラントです。"Invertor and Motor" ブロックには周辺装置も含まれます。これは、シミュレーション結果と UDP 送信側の調査に使用されるスコープです。UDP 送信側の生成されたコードは、Zynq ZC702 評価ボードからホストマシンへのシミュレーション データの送信を行います。ベクトル制御には、コントローラー ブロック "Speed controller" および "Torque controller" が含まれます。モデルを読み込むには、次を入力します。

slexFocZynqExample

アーキテクチャの定義

例の中のターゲット アーキテクチャは、Xilinx Zynq ZC702 評価キットです。[同時実行] ダイアログ ボックスにアクセスして、検証することができます。

[モデル化] タブで [モデル設定] を選択します。[モデル コンフィギュレーション パラメーター] ダイアログ ボックスの [ソルバー] タブで、[ターゲット上でタスクの同時実行を許可] を選択してから [タスクの構成] をクリックします。

評価ボードには ARM® Cortex®-A9 CPU とフィールド プログラマブル ゲート アレイ (FPGA) があります。ARM CPU を実行するタスクは 2 つあります。"Torque controller" は最初のタスクにマッピングされ、プラントを構成するブロック ("Speed and Torque Inputs" ブロックと "Invertor and Motor" ブロック) は 2 番目のタスクにマッピングされます。制御ループ内で高周波数で動作する "Speed controller" は FPGA にマッピングされます。これらの設定は [同時実行] ダイアログ ボックスの [タスクとマッピング] セクションで変更できます。

マルチスレッド コードと HDL コードの生成

Ctrl + B キーを入力するか、[ハードウェアに展開] を選択してマルチスレッドおよび HDL コードを生成します。生成された実行可能ファイルおよび FPGA ビットストリームは Zynq ボードに自動的にアップロードされます。この手順では、Zynq ボードがコンピューターに接続されていて、環境が適切に設定されている必要があります。詳細については、AMD SoC ボード用のサポートのインストール (Embedded Coder)を参照してください。

Zynq からのデータの受信

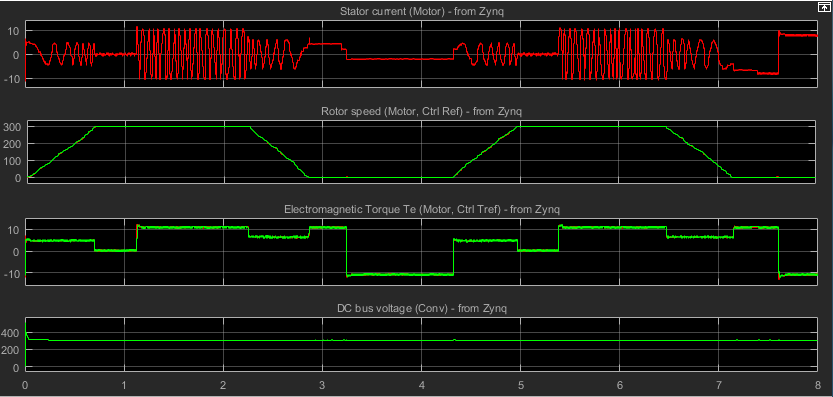

[View Simulation Results] を選択してスコープを開き、シミュレーションを実行して次の出力を取得します。

このシミュレーション出力と、Zynq ZC702 ボード上で実行する実行可能ファイルの出力を比較します。この比較を行うために、[View Deployment Results] を選択して UDP 受信機モデルにアクセスします。UDP 受信機モデルが選択されたら、シミュレーションを実行します。実行コマンドによって信号が Zynq ZC702 ボードに送信され、ボード上で実行可能ファイルの実行を開始します。シミュレーション データは UDP で Zynq ZC702 ボードからホスト マシンに送信されます。取得された UDP 信号は UDP 受信機モデルのスコープに表示されます。

モデルを閉じる

close_system('slexFocZynqExample', 0);