FPGA HDL コード生成

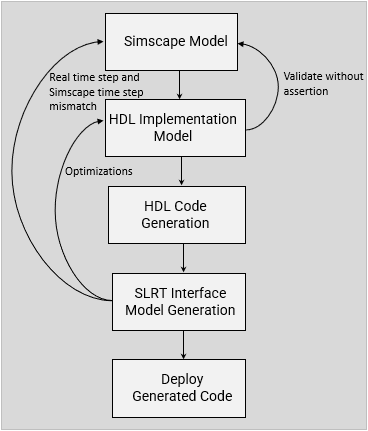

高速サンプル時間の要件があるモデルやサブシステムの場合、FPGA シミュレーションによって利点が得られることがあります。HDL Coder™ があれば、Simscape プラント モデルを HDL 実装モデルに変換し、そのモデルを使用して FPGA に展開する HDL コードを生成できます。Simscape モデルまたはサブシステムを FPGA に展開するには、次のようにします。

sschdladvisor関数を使用して Simscape HDL ワークフロー アドバイザーを起動します。このアドバイザーに従って、HDL 実装モデルを作成するプロセスを進めることができます。HDL ワークフロー アドバイザー ツールを使用して実装モデルを HDL コードに変換します。

Simulink® Real-Time™ を使用して HDL コードを FPGA に展開します。

モデルの合成を使用して、達成可能なハードウェア タイム ステップを予測できます。

関数

sschdladvisor | Simscape HDL ワークフロー アドバイザーを開く |

simscape.findNonlinearBlocks | Check model for blocks with nonlinear equations |

sschdl.updateRuntimeParameters | Generate updated tunable parameter data file for Simscape model (R2024a 以降) |

sschdl.generateOptimizedModel | Replace Simscape switches and converter blocks with dynamic switches optimized for FPGA deployment (R2024a 以降) |

トピック

- Simscape ハードウェアインザループ ワークフロー入門 (HDL Coder)

Simscape™ ハードウェアインザループ ワークフローのモデル化のガイドラインと制限。

- Linearize a Simscape Model to Prepare for HDL Code Generation

Learn how to linearize a model that uses the Backward Euler solver for HDL deployment.

- Simscape モデルからの FPGA プラットフォーム用の HDL コードの生成

Simscape モデルを FPGA 展開用の HDL コードに変換する方法について説明する。

- Simscape からの最適化された HDL 実装モデルの生成 (HDL Coder)

Simscape から生成された HDL 実装モデルの面積とタイミングを、HDL Coder 最適化を使用して最適化する。

- Simscape モデルの HDL コードの生成 (HDL Coder)

Simscape の線形スイッチド モデルから HDL コードを生成する。

- 複数のネットワークを含む Simscape モデルの HDL コードの生成 (HDL Coder)

大規模な Simscape ネットワークを複数のネットワークに分割し、HDL 実装モデルを生成する。

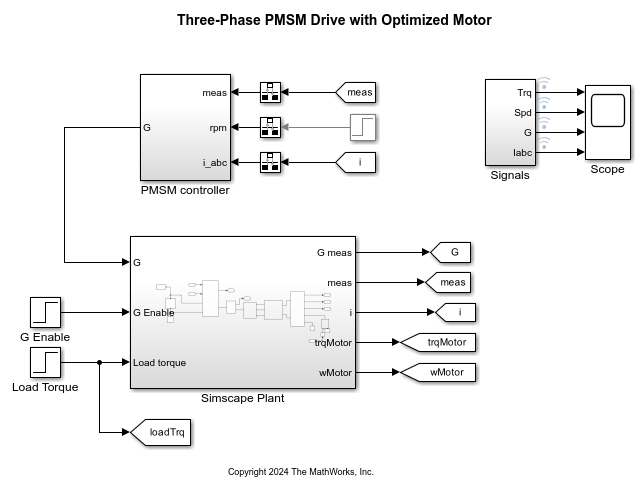

- 平均化スイッチを含む Simscape 三相 PMSM 駆動用の HDL コードの生成 (HDL Coder)

平均化スイッチをもつコンバーター ブロックを使用して三相 PMSM Simscape モデル用の HDL コードを生成して結果を合成し、FPGA に展開する。

- Simulate Large Time Steps Using Trapezoidal Rule Solver for Real-Time FPGA Deployment (HDL Coder)

Generate HDL code for a Simscape model by using the Trapezoidal Rule solver and deploy it onto a Speedgoat® FPGA I/O module.

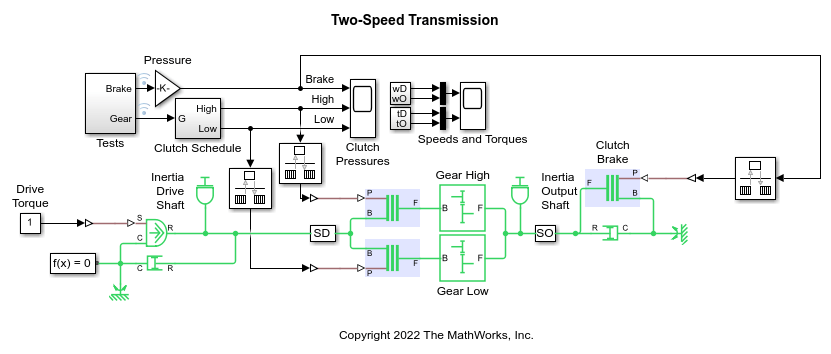

- Generate HDL Code for Simscape Models by Using Dynamic Switch Approximation (HDL Coder)

Generate HDL code and synthesize the results for a three-phase PMSM drive using Dynamic Switch Approximation method.

- Simscape アルゴリズムから生成された HDL 実装モデルの FPGA サンプリング周波数の改善 (HDL Coder)

生成された HDL 実装モデルにおけるオーバーサンプリングと、モデルのサンプル時間と元の Simscape アルゴリズムのサンプル時間との関係。

- HDL 実装モデルの Simscape アルゴリズムに対する検証 (HDL Coder)

Simscape アルゴリズムと HDL 実装モデルの間のシミュレーションの不一致を検証して解決する。

- Synthesis Results for Simscape Hardware-in-the-Loop Workflow (HDL Coder)

Access synthesis results for Simscape hardware-in-the-loop workflow example models.

トラブルシューティング

Resolving Issues with Nonlinearities

Troubleshoot simulation and code generation issues associated with nonlinearities.

Troubleshooting Real-Time Hardware Deployment Issues in Simscape Hardware-in-the-Loop Workflow (HDL Coder)

Troubleshoot real-time hardware deployment issues in Simscape Hardware-in-the-Loop workflow.

Troubleshoot Validation Errors in Simscape Hardware-in-the-Loop Workflow (HDL Coder)

Troubleshoot validation mismatches in Simscape Hardware-in-the-Loop workflow.