このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

Computer Vision Toolbox による Sobel エッジ検出アルゴリズム

この例では、Sobel エッジ検出アルゴリズムに適用される 「トップダウン」 設計方法を示して説明します。Sobel エッジ検出アルゴリズムは、一般的でありながらシンプルなエッジ検出アルゴリズムであり、この例ではこれに焦点を当てています。この例では、次のことを学びます。

Simulink® を使用して、システム レベルでデジタル信号処理 (DSP) アルゴリズムを設計する方法を説明します。

ハードウェアで実現できるように設計を詳細化する方法。

Simulink 環境で、手書きの HDL コード (Simulink モデルに対応) を ModelSim® または Cadence® Xcelium® と共同シミュレーションする方法。

このアプローチは、モデルベース設計の例です。モデルベース設計の詳細については、https://www.mathworks.com/solutions/model-based-design.html を参照してください。

例のすべてのモデルを実行するには、次の製品が必要です。

MATLAB®

Simulink

Fixed-Point Designer™

HDL Verifier™

Computer Vision Toolbox™

DSP System Toolbox™

ModelSim SE または PE。または Cadence Xcelium

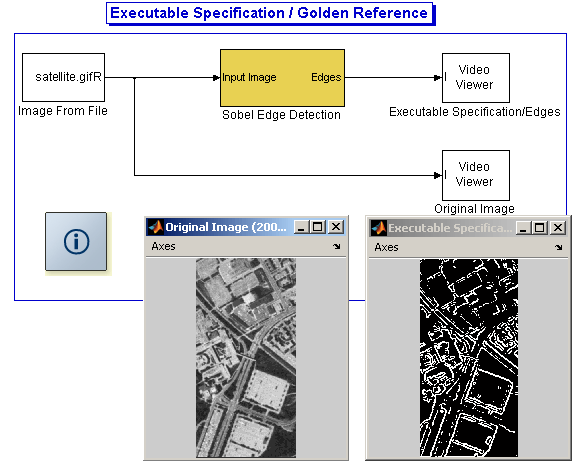

Sobelエッジ検出アルゴリズムの実行仕様

デザインが大規模かつ複雑になるにつれて、デザインを高レベルで記述する必要が生じてきました。この高レベルの記述により、設計者はシミュレーションをより速く実行できるだけでなく、開発プロセス全体で検証に使用することもできます。このプロセスにより、開発者は早い段階でバグを特定し、開発の終盤でのコストのかかるバグの発見を回避できます。この高レベルの設計は通常、システム エンジニアによって行われます。

ASIC や FPGA などのハードウェアに DSP アルゴリズムを実装するには、システム レベル エンジニアが最初にアルゴリズムを設計し、そのアルゴリズムがプロジェクト要件を満たしていることを確認します。この設計は、後にアルゴリズムをハードウェアに移植する責任を負うエンジニアにとって貴重な参考資料となります。

この例では、Sobel エッジ検出アルゴリズムが Simulink に実装されています。実行可能モデルを開き、「Sobel Edge Detection」ブロックをダブルクリックして、Simulink でアルゴリズムがどのように実装されているかを確認します。Sobel Edge Detection ブロックをダブルクリックすると、アルゴリズムが 2 つの 2D フィルターで構成されていることがわかります。1 つは列方向の勾配を計算するフィルター (上のフィルター)、もう 1 つは行方向の勾配を計算するフィルター (下のフィルター) です。どちらのフィルターも 3x3 カーネルを使用します。

この Simulink モデルは、開発パスの残りの部分の仕様として機能します。これは 実行可能な仕様 であるため、このモデルを Simulink 環境で簡単に実行できます。

この例では、エッジ検出アルゴリズムへの入力として衛星画像を使用します。この画像は入力テスト ベクトルとして機能し、例全体で使用されます。アルゴリズムのハードウェア実装を担当するエンジニアが Simulink 環境でも作業する場合、テスト ベクトルを別のアプリケーションに移植したり、人為的エラーが発生しやすいテスト ハーネスを作成したりするための余分なオーバーヘッドは必要ありません。実行可能仕様で使用されるテスト ハーネスは、例全体で使用されます。

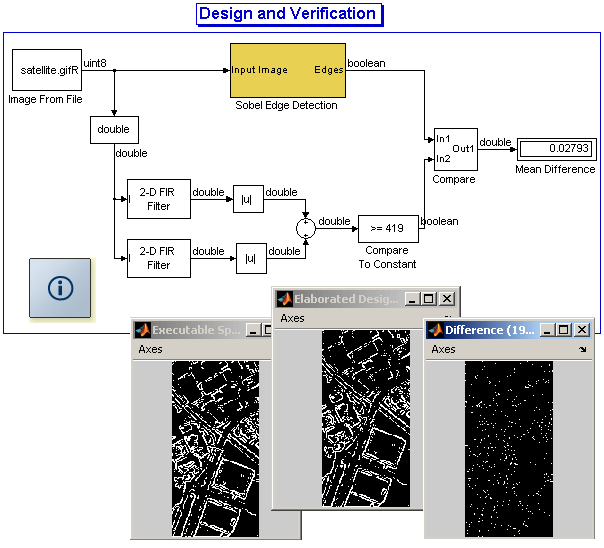

実装アルゴリズムの設計と検証

実行可能モデルを設計する際、システム エンジニアは通常、実装の詳細を念頭に置くのではなく、動作要件に一致するようにアルゴリズムを実装します。システム エンジニアが実行可能仕様を開発チームに提出すると、開発チームは、メモリや処理能力などのリソースが限られている可能性のあるリアルタイム システムに設計を適合させるために、実行可能仕様に変更を加える必要がある場合があります。

この例では、開発者は、より効率的なハードウェア実装のために、二乗演算を削除し、絶対値演算に置き換えることを決定する場合があります。これにより、コシミュレーション結果とゴールデンリファレンスの間に差異が生じますが、この例では、その差異は許容できるものと想定します。エッジ検出設計 モデルを開きます。以前のモデルと同じテスト ベクトルが引き続き使用されていることがわかります。結果はゴールデンリファレンスと照らし合わせて簡単に検証できます。数値表示には、ゴールデンリファレンスと新しいデザインの平均差が表示されます。

固定小数点設計

最終的な目標はアルゴリズムを FPGA または ASIC に実装することなので、倍精度設計を固定小数点設計に変換する必要があります。これは Simulink を使用すると簡単に実行できます。前のセクションで開発した倍精度モデルを使用して、新しいブロックを導入せずに固定小数点モデルを直接開発します。Simulink を使用すると、データのビット数とスケーリング、および数学演算を決定でき、システムの固定小数点演算を分析するための優れた環境が提供されます。

この固定小数点設計では、フィルターへの入力は符号付き 9 ビット整数であり、フィルターの出力は符号付き 11 ビット整数です。フィルターや合計ブロックなどの各計算ブロックをダブルクリックすると、開発者がそのブロックの内部計算に関連するビット幅とスケーリングを簡単に調整できることがわかります。これにより、設計者は、デバイスの領域を節約するために必要な最小限のビット数を使用しながら、ゴールデン リファレンスの出力を一致させるという妥協点を見つける大きな力を得ることができます。

固定小数点モデルを開き、2D フィルターや加算ブロックなどの計算ブロックをダブルクリックして対応する固定小数点パネルを確認し、固定小数点がどのように実装されているかを調べます。

デザインの精緻化

この例では、エッジ検出アルゴリズムへの入力は、サイズが 200 x 100 の 2 次元画像です。リアルタイム システムでは、入力はマトリックスではなくシリアル データ ストリームになる可能性が高くなります。たとえば、このシリアル データ ストリームは、電荷結合素子 (CCD) によって生成できます。したがって、エッジ検出アルゴリズムがシリアル データ ストリームを受け入れて 2D フィルタリングを実行できるように、設計の構造を変更する必要があります。

この範囲では、まず入力画像をシリアル化します。次に、このシリアル データに対して 2D フィルタリングを実行します。その後、データ ストリームをデシリアル化して、出力をゴールデン リファレンスと比較できるようにします。これがどのように行われるかについては、エッジ検出の詳細化 モデルを参照してください。

この操作は下部フィルターに対してのみ実行されます。予想通り、新しいデザインでも以前とまったく同じ結果が得られています。シリアライザ ブロックのバッファリングを補正するために 2 つの遅延要素が追加されました。この設計は、Simulink のマルチレート機能も示しています。シリアライザ ブロックの出力は、そのブロックへの入力に比べてサンプリング レートが 20000 倍高くなります。

Simulink® コシミュレーション

前のセクションのモデルは HDL 設計者に渡すことができ、HDL 設計者は最後のセクションで設計された 2D フィルターを使用して、対応する VHDL または Verilog コードを記述できます。コードが記述されると、HDL 設計者は HDL Verifier™ を使用して ModelSim または Xcelium を使用した Simulink 環境で HDL 設計をシミュレートし、HDL 設計の出力を実行可能仕様の出力と比較できます。このプロセスでは、HDL テストベンチを生成する必要がないことに注意してください。Simulink モデルは、入力テスト ベクトルを HDL Verifier を介して ModelSim または Xcelium に送り、ModelSim または Xcelium からデータを抽出して Simulink 環境に返します。HDL 設計者は、HDL コードが仕様に従って実行されるかどうかを簡単に検証できます。

モデルシム/クエスタシム

HDL Verifier を使用して Simulink と ModelSim を協調シミュレーションする方法については、VHDL モデル または Verilog モデル を参照してください。最後の図は、ModelSim に表示される信号のスナップショットを示しています。

Xcelium HDL Verifier ソフトウェアを使用して Simulink と Xcelium プラットフォームを共同シミュレーションする方法については、Verilog モデル を参照してください。