このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

FPGA 用マルチチャネル FIR フィルター

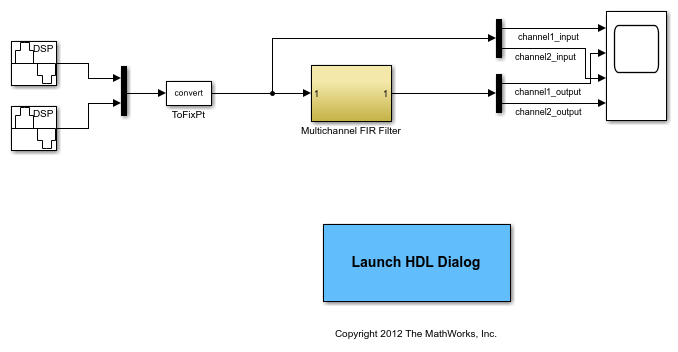

この例では、ハードウェア用の複数の入力データ ストリームをもつ離散 FIR フィルターを実装する方法を示します。

多くの DSP アプリケーションでは、複数のデータ ストリームが同じフィルターによってフィルター処理されます。簡単なソリューションは、各チャネルに対して別々のフィルターを実装することです。複数のチャネルで 1 つのフィルターの実装を共有することで、より面積効率の高い構造を作成できます。結果として得られるハードウェアでは、単一チャネル フィルターに使用されるクロック レートと比較して、より高速なクロック レートが必要になります。

マルチチャネル FIR フィルターのモデル化

modelname = 'dspmultichannelhdl';

open_system(modelname);

モデルには、2 チャネルの FIR フィルターが含まれています。入力データ ベクトルには、異なる周波数をもつ正弦波信号の 2 つのストリームが含まれています。入力データ ストリームはローパス フィルターで処理されます。このフィルターの係数は [モデル プロパティ] のコールバック関数 InitFcn で指定されています。

完全なパラレル アーキテクチャを Discrete FIR Filter ブロックに選択し、複数チャネルでのリソース共有を有効にします。

systemname = [modelname '/Multichannel FIR Filter']; blockname = [systemname '/Discrete FIR Filter']; set_param(blockname,'FilterStructure','Direct form symmetric'); hdlset_param(blockname,'Architecture','Fully Parallel'); hdlset_param(blockname,'ChannelSharing','On');

あるいは、これらの設定を [HDL ブロック プロパティ] メニューで指定できます。これには、ブロックを右クリックして [HDL コード]、[HDL ブロック プロパティ] を選択してアクセスします。

シミュレーション結果

モデル例を実行し、スコープを開いて 2 つのデータ ストリームを比較します。

sim(modelname);

open_system([modelname '/Scope']);

HDL コードとテスト ベンチの生成

このモデル例の HDL コードを生成するには、HDL Coder™ のライセンスが必要です。次のコマンドを使用して、Multichannel FIR Filter サブシステムの HDL コードを生成します。リソース利用レポートを有効にします。

makehdl(systemname,'resource','on');

次のコマンドを使用して、HDL シミュレーションの結果と Simulink モデルの結果を比較するテスト ベンチを生成します。

makehdltb(systemname);

リソースの利用状況の比較

共有ありの場合と共有なしの場合のリソース使用を比較するには、チャネル間でのリソースの共有を無効にし、HDL コードを再度生成してから、リソース利用レポートを比較します。

hdlset_param(blockname,'ChannelSharing','Off'); makehdl(systemname,'resource','on');