このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

イネーブルベースのマルチサイクル パス制約を使用してタイミング要件を満たす

Simulink® モデルに複数のサンプルレートが含まれている場合またはパイプライン レジスタを挿入する速度と面積の最適化を使用している場合、設計にマルチサイクル パスが含まれる可能性があります。マルチサイクル パスは FPGA クロック レートよりも遅いサンプルレートで動作する 2 つのレジスタ間のデータ パスです。実行を完了するために複数のクロック サイクルを用います。クロック レートを設計内のさまざまなパスのサンプルレートに同期するために、単一クロック モードまたは複数クロック モードを使用できます。既定では、HDL Coder™ は最速のサンプル レートの単一の基本クロックを生成する単一クロック モードを使用し、マルチサイクル パスのクロック レートを制御するタイミング コントローラー エンティティを作成します。タイミング コントローラーは必要なレートと位相情報をもつ一連のクロック イネーブルを生成し、異なるサンプルレートで動作する Delay ブロックなどのシーケンシャル要素を制御します。

生成された HDL コードを合成する場合、合成ツールはマルチサイクル パスのタイミング要件を満たせない場合があります。タイミングの問題は、設計内のさまざまなサンプルレートを合成ツールが生成された HDL コードから推測できないために発生します。合成ツールは、設計内のレジスタは基本クロック レートで実行されるものと想定し、データが 1 クロック サイクル以内にレジスタ間を移動するよう要求します。しかし、マルチサイクル パスは 1 クロック サイクル以内に実行を完了する必要はないため、タイミング要件を満たすことができません。タイミング要件を満たすには、イネーブルベースのマルチサイクル パス制約の生成を指定します。

イネーブルベースのマルチサイクル パス制約の動作の仕組み

合成ツールは、転送元レジスタから転送先レジスタにデータが 1 クロック サイクル以内に伝播することを要求します。マルチサイクル パス制約は、レジスタ間のデータの伝播に複数クロック サイクルを許容することでこのタイミング要件を緩和します。コード ジェネレーターはタイミング コントローラー イネーブル信号を使用してイネーブルベースのレジスタ グループを作成します。各グループのレジスタは同じクロック イネーブルによって駆動されます。イネーブルベースの制約を適用して HDL コードを生成すると、コード ジェネレーターは命名規則 dutname_constraints に従って制約ファイルを出力します。このファイルはマルチサイクル パスのタイミング要件を定義し、満たす必要があるセットアップ制約とホールド制約に関する情報を含んでいます。

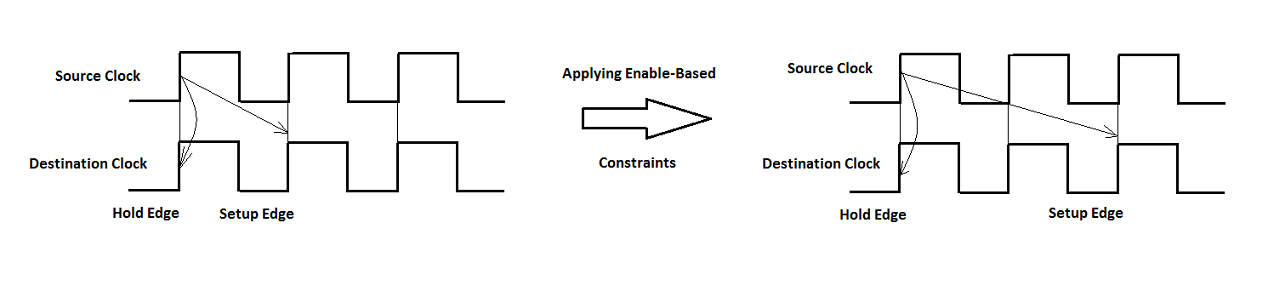

この図は REGA から REGB へのデータの伝播に一定数のクロック サイクル (N とします) がかかるマルチサイクル パスを示しています。既定では、合成ツールはセットアップ エッジを次のアクティブ クロック エッジに、ホールド エッジを転送先のクロック信号と同じアクティブ クロック エッジに定義します。N クロック サイクルかかるマルチサイクル パスの場合、より長いデータ伝播時間を許容するようにセットアップ エッジとホールド エッジがこの制約によって再定義されます。

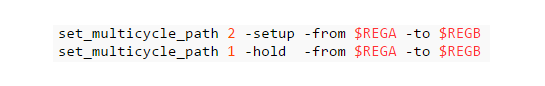

例として、転送元レジスタから転送先レジスタへのデータの伝播に 2 クロック サイクルかかるマルチサイクル パスについて検討します。この波形は、イネーブルベースの制約を適用することによって、セットアップ エッジとホールド エッジが再定義される様子を示しています。次のコードの抜粋は、マルチサイクル パス制約を有効にしたときに生成される制約ファイル内のセットアップ要件とホールド要件を示しています。

イネーブルベースの制約の指定

イネーブルベースの制約を生成する前に、以下を行わなければなりません。

設計内のマルチサイクル パスを保持します。マルチサイクル パス制約の生成を有効にする前に、マルチサイクル パス制約を適用する領域でクロック レート パイプラインや適応パイプラインなどの最適化が無効になっていることを確認します。

低速のクロック レートで動作する領域が、ゼロ位相で動作するタイミング コントローラー ベースのクロック イネーブル信号によって制限されていることを確認します。

合成ツールを指定します。生成されるマルチサイクル パス制約ファイルの形式は、指定する [合成ツール] に依存します。合成ツールを指定せず、[EDA スクリプトを生成] チェック ボックスをオンにした場合、HDL Coder ではマルチサイクル パス制約は生成されません。

単一クロック モードを使用します。[HDL コード生成] 、 [グローバル設定] ペインで、[クロックの入力] を

Singleに設定します。

マルチサイクルの制約の生成は、[コンフィギュレーション パラメーター] ダイアログ ボックス、HDL ワークフロー アドバイザー UI またはコマンド ラインで指定できます。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [ターゲットおよび最適化] ペインで、[イネーブルベースの制約] チェック ボックスをオンにします。

HDL ワークフロー アドバイザーの [HDL コード生成] 、 [コード生成オプションを設定] 、 [最適化オプションを設定] タスクで、[イネーブルベースの制約] チェック ボックスをオンにします。

コマンド ラインで

MulticyclePathConstraintsプロパティをhdlset_paramまたはmakehdlと共に使用します。

イネーブルベースの制約を使用するメリット

合成ツールがマルチサイクル パス制約を特定した場合、次を行うことができます。

より高いクロック レートを実現して設計のタイミングを改善できます。

マルチサイクル パス制約はパイプライン レジスタを導入しないため、ターゲット FPGA デバイス上の面積のフットプリントを削減できます。

コード ジェネレーターが多くの最適化設定を実行する必要がないため、HDL コードの生成時間を短縮できます。

マルチサイクル パス制約が合成ツールのタイミング要件を緩和するため、合成時間を短縮できます。

制約をもつ生成されたモデルは元のモデルと同一であるため、HDL コードの生成後に設計の検証を省略できます。

イネーブルベースの制約の設定を使用すると次のようになります。

生成された制約は合成ツール内の名前の変更に対してより強くなります。

HDL コード生成が高速になります。

[ターゲット ワークフロー] を

Generic ASIC/FPGA、IP Core Generation、およびSimulink Real-Time FPGA I/Oにできます。制約ファイルの形式は、次の合成ツールでサポートされます。Xilinx® ISE、Xilinx Vivado®、Altera® Quartus® II、Cadence® Genus。

モデリング ガイドライン

イネーブルベースの制約の生成を指定する場合、設計で以下のモデリング パターンを使用します。レジスタによって囲まれていない遅いレートの領域がモデルに含まれている場合、遅いレートの領域の入力と出力に同じ遅いレートの遅延を追加します。たとえば、MATLAB® のコマンド ウィンドウで次のコマンドを入力すると、単一クロック モードで実装されたマルチレート CIC 内挿フィルターが表示されます。

openExample('hdlcoder_clockdemo');次の図は、遅いサンプル時間 D2 の注釈が付けられたモデル内の遅いレートの領域の入力と出力を Unit Delay ブロックで囲うことによって、イネーブルベースの制約が遅いレートのパスを特定できるようにする方法を示しています。

メモ

Rate Transition ブロックを使用して入力レジスタと出力レジスタを導入することもできますが、この場合はレジスタが遅いレートでゼロ位相をもつようにしてください。

さまざまな合成ツール用のマルチサイクル パス制約

イネーブルベースのマルチサイクル パス制約には、指定する [合成ツール] に依存したさまざまなファイル形式があります。

Altera Quartus II

HDL Coder は SDC ファイルの形式で制約を生成します。次のコードの抜粋は、Altera Quartus II 用に生成された SDC ファイルを示しています。

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0 set enbreg [get_registers *u_DUT_tc|phase_0] set_multicycle_path 4 -to [get_fanouts $enbreg -through [get_pins -hier *|ena]] -end -setup set_multicycle_path 3 -to [get_fanouts $enbreg -through [get_pins -hier *|ena]] -end -hold

Cadence Genus

HDL Coder は SDC ファイルの形式で制約を生成します。次のコードの抜粋は、Cadence Genus 用に生成された SDC ファイルを示しています。

# Multicycle constraints for clock enable: MCP_Subsystem_tc.u1_d5_o0 set MCPnet0 [get_db hnets .name *u_MCP_Subsystem_tc/phase_0] set MCPreg0 [get_cells -of [all_fanout -flat -endpoints_only -from $MCPnet0]] set_multicycle_path 5 -setup -from $MCPreg0 -to $MCPreg0 set_multicycle_path 4 -hold -from $MCPreg0 -to $MCPreg0

Xilinx Vivado

HDL Coder は XDC ファイルの形式で制約を生成します。次のコードの抜粋は、Xilinx Vivado 用に生成された XDC ファイルを示しています。

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0

set enbregcell [get_cells -hier -filter {mcp_info=="DUT_tc.u1_d4_o0"}]

set enbregnet [get_nets -of_objects [get_pins -of_objects $enbregcell -filter {DIRECTION == OUT}]]

set reglist [get_cells -of [filter [all_fanout -flat -endpoints_only $enbregnet] IS_ENABLE]]

set_multicycle_path 4 -setup -from $reglist -to $reglist -quiet

set_multicycle_path 3 -hold -from $reglist -to $reglist -quietマルチサイクル パス制約は、ATTRIBUTE キーワードで合成ネットリストをクエリすることによってイネーブルベースのレジスタ グループを形成します。次のコードの抜粋は、サポートされているいずれかのターゲット ワークフローを実行するときの、合成ネットリスト内のこのキーワードを示しています。

... ATTRIBUTE mcp_info: string ATTRIBUTE mcp_info OF phase_0 : SIGNAL IS "DUT_tc.u1_d4_o0"; ...

Xilinx ISE

HDL Coder は UCF ファイルの形式で制約を生成します。次のコードの抜粋は、クロック イネーブル信号によって制御され、ターゲット周波数が 300MHz である 1 つの遅いレートの領域をもつモデル用に生成された UCF ファイルを示しています。マルチサイクル パス制約は、指定する [ターゲット周波数] に依存します。

# Multicycle constraints for clock enable: DUT_tc.u1_d4_o0 NET "*u_DUT_tc/phase_0" TNM_NET = FFS "TN_u_DUT_tc_phase_0"; TIMESPEC "TS_u_DUT_tc_phase_0" = FROM "TN_u_DUT_tc_phase_0" TO "TN_u_DUT_tc_phase_0" TS_FPGA_CLK/4;

Generic ASIC/FPGA または Simulink Real-Time FPGA I/O ワークフローを Xilinx ISE と共に実行したときに生成されるクロック制約を次のコードに示します。

# Timing Specification Constraints NET "clk" TNM_NET = "TN_clk"; TIMESPEC "TS_FPGA_CLK" = PERIOD "TN_clk" 300 MHz;

関数 makehdl を使用して HDL コードを生成するときにマルチサイクル パス制約を使用する場合は、UCF ファイルに TS_FPGA_CLK 制約が追加されていることを確認してください。

タイミング制御ロジックでのイネーブル信号の保持

イネーブルベースのマルチサイクル パス (MCP) 制約を適用してマルチサイクル データ パスのタイミング制約を緩和すると、HDL Coder によってタイミング コントローラー ロジックをもつ MCP が生成されます。イネーブルベースの制約を合成ツールに指定すると、合成ツールによってこのタイミング コントローラー ロジックが最適化され、単一クロック領域設計に変換されます。MCP 制約は生成された HDL コードには適用されません。合成ツールでこのタイミング制御ロジックを保持するために、HDL Coder では、生成されたタイミング コントローラー HDL コード内のすべてのイネーブル信号に属性 direct_enable が追加されます。

次の生成された VHDL® コードは、タイミング コントローラー ロジック内のイネーブル信号に direct_enable 属性が追加されることを示しています。

... ATTRIBUTE direct_enable OF enb_1_1_1: SIGNAL IS "yes"; ...

次の生成された Verilog® コードは、タイミング コントローラー ロジック内のイネーブル信号に direct_enable 属性が追加されることを示しています。

... (* direct_enable = "yes" *) output enb_1_1_1; ...

direct_enable 属性があるため、合成ツールで MCP 制約を指定した際に MCP 制約が設計に適用されます。

制限

マルチサイクル パス制約ファイルは

FPGA-in-the-Loopワークフローではサポートされません。遅いレートの領域がレジスタで囲まれていない場合、マルチサイクル パス制約では遅いレートの 2 つの Delay ブロックを追加する必要があり、これによって設計のレイテンシが増加します。

コード ジェネレーターが、タイミング コントローラーベースのイネーブル信号の非ゼロ位相値をもつレジスタの間のパスに対する制約を追加することはありません。コード ジェネレーターが制約を追加する場合、Delay ブロックなどの位相

0のクロック イネーブル信号から派生するレジスタを使用します。クロック レート パイプラインや適応パイプラインなどの最適化を有効にした領域にマルチサイクル パス制約を適用した場合、生成される制約の効果が低減する場合があります。クロック レート パイプラインを使用すると、レジスタはより速いクロック レートで動作するため、設計内の遅いレートのレジスタを維持できない場合があります。

HDL Coder はシングルレート モデルに対してマルチサイクル パス制約を生成しません。

複数クロック モードを使用する場合、コード ジェネレーターはマルチサイクル パス制約ファイルを出力しません。