HDL FIFO

入力サンプルのシーケンスを先入れ先出しレジスタに格納する

ライブラリ:

HDL Coder /

HDL RAMs

説明

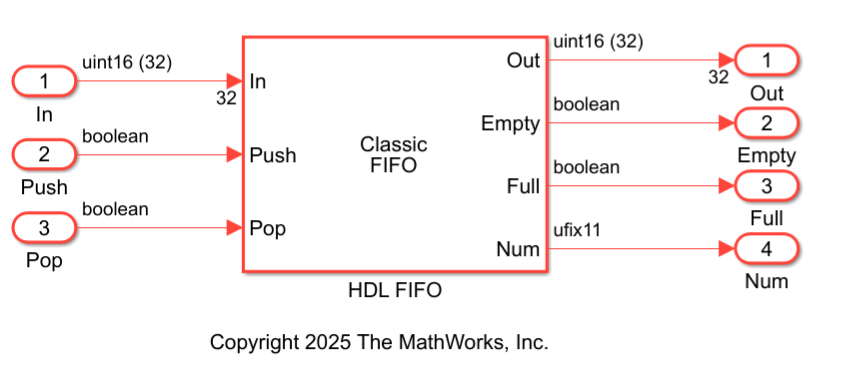

HDL FIFO ブロックは、入力サンプルのシーケンスを先入れ先出し (FIFO) レジスタに格納します。ブロックは書き込まれた順序と同じ順序でデータを出力します。[Push] および [Pop] 入力端子を使用して、FIFO 操作を制御できます。両方の制御信号が同じタイム ステップでアサートされると、ブロックはプッシュ操作の前にポップ操作を実行します。

HDL FIFO ブロックは、機能的にも動作的にもハードウェア プラットフォーム上の FIFO ユニットに似ています。内部的には、このブロックは Simple Dual Port RAM System ブロックを使用します。このブロックを使用して、ほとんどの FPGA デバイス上の RAM リソースにマッピングする HDL コードを生成できます。

例

Map HDL FIFO Blocks to UltraRAM Resources on FPGA

Generate HDL code with synthesis attributes that enable UltraRAM inference for an HDL FIFO block on an FPGA.

- R2026a 以降

- ライブ スクリプトを開く

制限

HDL FIFO ブロックの FPGA ビットストリームを作成した場合、ブロック内の FIFO レジスタはグローバルなリセット ロジックでリセットされません。FIFO レジスタをリセットするには、リセット ロジックを実装する必要があります。

HDL FIFO ブロックでは連続サンプル時間はサポートされません。HDL FIFO ブロックへの入力には離散サンプル時間を指定する必要があります。

端子

入力

データ入力信号。スカラーまたはベクトルとして指定します。FIFO にデータを書き込むと、ブロックは最新のデータを FIFO レジスタの末尾にプッシュします。ブロックは、このエントリの後に後続のデータ エントリを配置します。

メモ

[In] 端子に接続した信号がベクトルの場合、データ型は [データ入力の次元] パラメーターで指定された値と一致する必要があります。

データ型: single | double | half | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

複素数のサポート: あり

書き込み制御信号。Boolean 型のスカラーとして指定します。この端子が値 1 を受信すると、ブロックは [In] 端子の現在の入力を FIFO レジスタの末尾にプッシュします。

データ型: Boolean

読み取り制御信号。Boolean 型のスカラーとして指定します。この端子が値 1 を受信すると、ブロックは FIFO レジスタから最初の要素をポップし、その値を [Out] 端子で出力します。

データ型: Boolean

リセット制御信号。Boolean 型のスカラーとして指定します。この端子が値 1 を受信すると、ブロックは [Empty]、[Full]、および [Num] 出力端子を初期状態にリセットします。

依存関係

この端子を有効にするには、[ローカル リセット端子] ブロック パラメーターを選択します。

データ型: Boolean

出力

データ出力信号。スカラーまたはベクトルとして返されます。この端子は、FIFO レジスタから先に書き込まれたデータを出力し、次の有効な読み取り操作までその値を保持します。

データ型: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

複素数のサポート: あり

空ステータス信号。スカラーとして返されます。FIFO レジスタが空でデータ エントリが含まれていない場合、ブロックはこの信号を 1 に設定します。

依存関係

この端子を有効にするには、[空のレジスタのインジケーター端子 (Empty) を表示] ブロック パラメーターを選択します。

データ型: Boolean

フル ステータス信号。スカラーとして返されます。FIFO レジスタがフルで追加のデータ エントリを受け入れることができない場合、ブロックはこの信号を 1 に設定します。

依存関係

この端子を有効にするには、[フル レジスタのインジケーター端子 (Full) を表示] ブロック パラメーターを選択します。

データ型: Boolean

データ エントリ数。スカラーとして返されます。この信号は、FIFO レジスタに現在格納されているデータ エントリの数を示します。ブロックは、FIFO にデータを書き込むたびにこの値を 1 ずつインクリメントし、FIFO から読み取るたびにこの値を 1 ずつデクリメントします。

依存関係

この端子を有効にするには、[レジスタ エントリ数の端子 (Num) を表示] ブロック パラメーターを選択します。

データ型: uint8 | uint16 | uint32 | uint64 | fixed point

パラメーター

FIFO レジスタで保持できるエントリの数を指定します。最小値は 4 です。

プログラムでの使用

ブロック パラメーター: fifo_size |

| 型: 文字ベクトル |

| 値: 4 以上の整数 |

既定の設定: 10 |

ブロックの演算モードを指定します。既定では、[モード] パラメーターは [クラシック] に設定されており、ブロック アイコンで Classic FIFO と表示されます。このパラメーターを [FWFT] に設定すると、ブロック アイコンで FWFT FIFO と表示されます。[FWFT] モードでは、読み取り要求を行わずに、FIFO レジスタに書き込まれた最初の語を先読みして表示できます。[FWFT] モードは、AXI4-Stream インターフェイスを使用してバックプレッシャーを適用する場合に役立ちます。

プログラムでの使用

ブロック パラメーター: mode |

| 型: 文字ベクトル |

値: 'Classic' | 'FWFT' |

既定の設定: 'Classic' |

出力サンプル時間と入力サンプル時間の比率を指定します。既定の比率値は 1 です。これは、[In] および [Push] 入力端子と [Out] および [Pop] 出力端子が同じサンプル レートで実行されることを意味します。正の整数または 1/N 形式の値 (N は正の整数) を入力することにより、入力と出力が異なるサンプル時間で実行されるように構成できます。たとえば、「1/2」と入力すると、出力サンプル時間が入力サンプル時間の半分になるため、出力の方が実行が速くなります。[Full]、[Empty]、および [Num] 出力端子はより速いレートで実行されます。

プログラムでの使用

ブロック パラメーター: ratio |

| 型: 文字ベクトル |

| 値: 1 以上の整数 |

既定の設定: 1 |

R2026a 以降

入力データの次元を指定します。

メモ

[データ入力の次元] パラメーターは、[In] 端子の入力信号のベクトル長と一致する必要があります。

プログラムでの使用

ブロック パラメーター: dataDim |

| 型: 文字ベクトル |

| 値: 1 以上の整数 |

既定の設定: 1 |

フルの FIFO に書き込もうとしたときにブロックがどのように応答するかを指定します。

プログラムでの使用

ブロック パラメーター: push_msg |

| 型: 文字ベクトル |

値: 'Warning' | 'Ignore' | 'Error' |

既定の設定: 'Warning' |

空の FIFO から読み取ろうとしたときにブロックがどのように応答するかを指定します。

プログラムでの使用

ブロック パラメーター: pop_msg |

| 型: 文字ベクトル |

値: 'Warning' | 'Ignore' | 'Error' |

既定の設定: 'Warning' |

[Empty] 出力端子を有効にするかどうかを指定します。この端子は、FIFO レジスタが空である場合に 1 を出力し、FIFO に 1 つ以上のデータ エントリが格納されていれば 0 を出力します。

プログラムでの使用

ブロック パラメーター: show_empty |

| 型: 文字ベクトル |

値: 'on' | 'off' |

既定の設定: 'on' |

[Full] 出力端子を有効にするかどうかを指定します。この端子は、FIFO レジスタがフルの場合に 1 を出力します。

プログラムでの使用

ブロック パラメーター: show_full |

| 型: 文字ベクトル |

値: 'on' | 'off' |

既定の設定: 'on' |

[Num] 出力端子を有効にするかどうかを指定します。この端子は、FIFO キューに現在格納されている使用可能なデータ エントリの数を出力します。

プログラムでの使用

ブロック パラメーター: show_num |

| 型: 文字ベクトル |

値: 'on' | 'off' |

既定の設定: 'on' |

[rst] 入力端子を有効にするかどうかを指定します。この端子が値 1 を受信すると、ブロックは [Empty]、[Full]、および [Num] 出力端子を初期状態にリセットします。

プログラムでの使用

ブロック パラメーター: rst_port |

| 型: 文字ベクトル |

値: 'on' | 'off' |

既定の設定: 'off' |

アルゴリズム

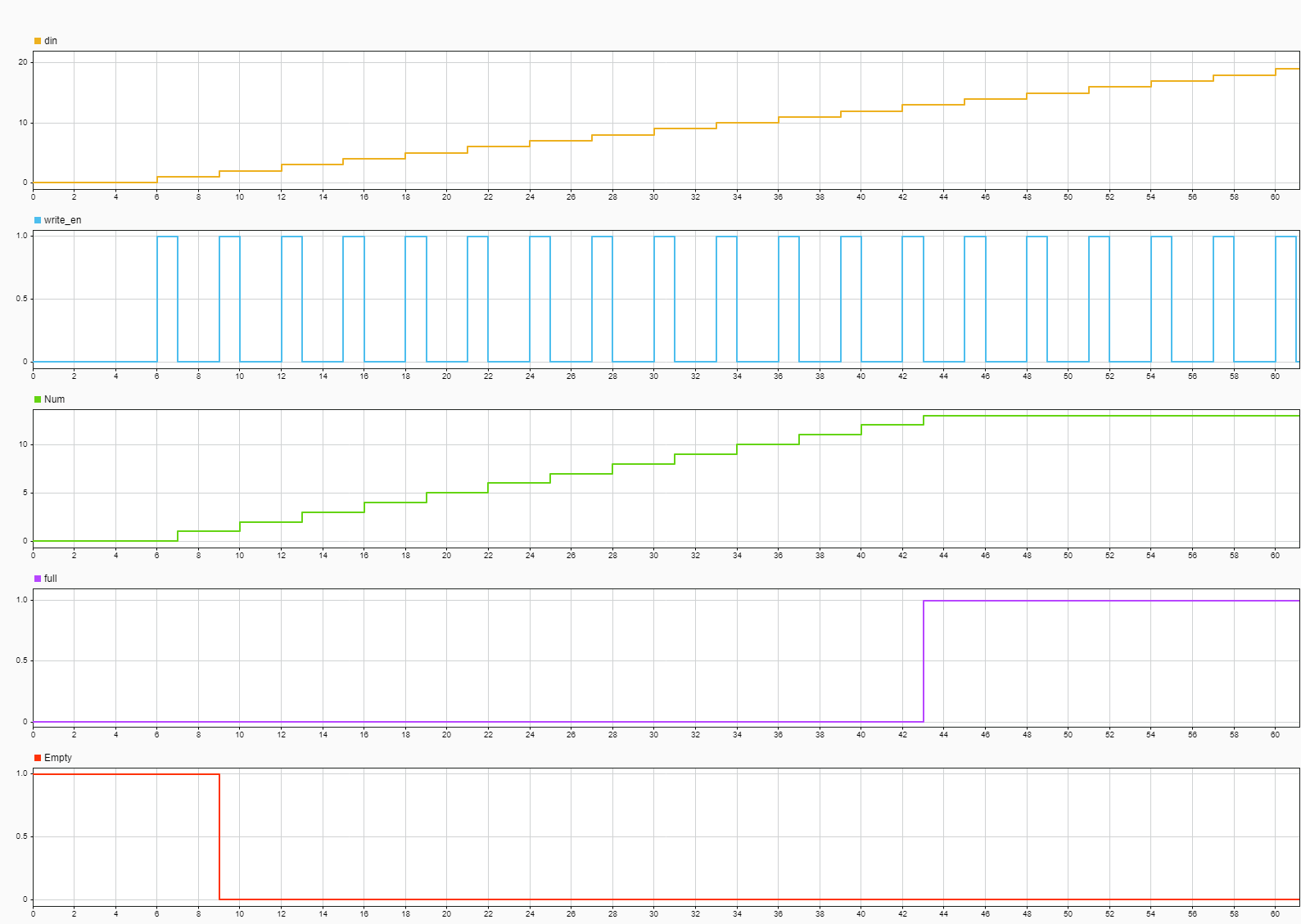

次の図は、書き込み操作を示しています。書き込み操作では、[Push] 入力端子がイネーブル信号として機能します。図では、[write_en] がこの信号を示しています。

[write_en] 信号が 0 のときは、ブロックは FIFO にデータを書き込まず、[Empty] フラグをアサートします。

[write_en] が 1 になると、ブロックは次のタイム ステップで入力端子 [In] の [din] 信号を FIFO レジスタの末尾にプッシュします。[Num] 信号は、FIFO レジスタ内のデータ エントリの数を示します。FIFO にデータを書き込むたびに、[Num] 信号が 1 ずつインクリメントされます。タイム ステップ 6 で [write_en] が 1 になっています。次のタイム ステップ 7 でデータが FIFO に書き込まれます。[Num] 信号が 1 だけインクリメントされ、[Empty] フラグがデアサートされます。

この FIFO は、[レジスタ サイズ] パラメーターで指定されたレジスタ サイズを使用します。既定では、レジスタ サイズは 10 です。図では、[Num] 信号がタイム ステップ 34 で 10 になると、[Full] 信号がアサートされます。[Full] 信号が 1 になった後、FIFO にエントリをさらに書き込むと、ブロックから警告が生成されます。

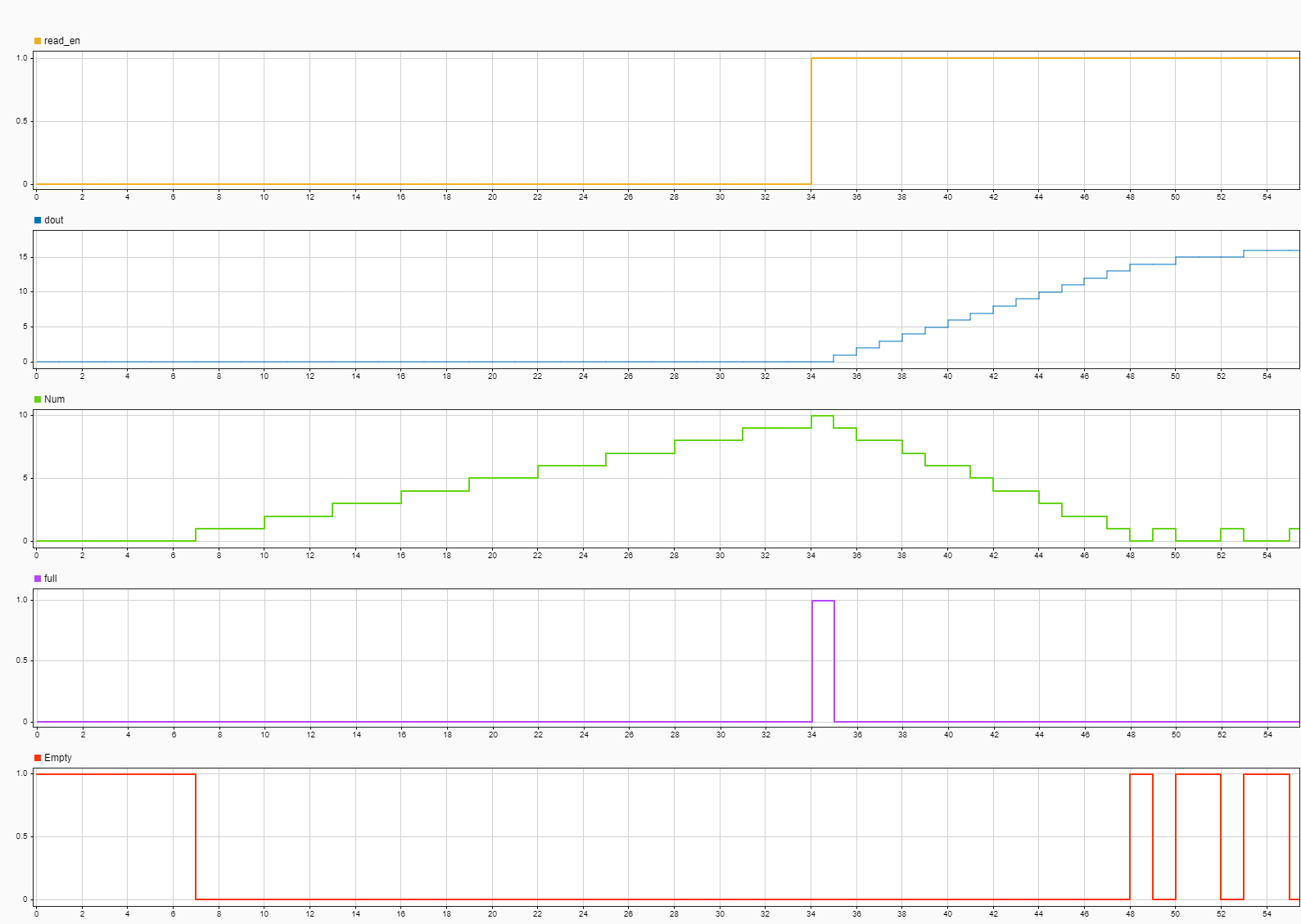

次の図は、読み取り操作を示しています。読み取り操作では、[Pop] 入力端子がイネーブル信号として機能します。図では、[read_en] がこの信号を示しています。

図では、[read_en] 信号がタイム ステップ 34 で 1 になると、[dout] 信号は次のタイム ステップ 35 で FIFO の最も古いエントリを出力します。タイム ステップ 35 で FIFO からデータを読み取った時点で、[Full] フラグがデアサートされ、[Num] 信号が 1 だけデクリメントされます。

[Num] 信号が 0 になると、[Empty] 信号がアサートされます。[Empty] 信号が 0 になった後、FIFO からエントリをさらに読み取ると、ブロックから警告が生成されます。

次の図は、[モード] パラメーターを FWFT に設定した場合の書き込み操作を示しています。書き込み操作では、[Push] 入力端子がイネーブル信号として機能します。図では、[write_en] がこの信号を示しています。

[write_en] 信号が 0 のときは、ブロックは FIFO にデータを書き込まず、[Empty] フラグをアサートします。

[write_en] が 1 になると、ブロックは次のタイム ステップで入力端子 [In] の [din] 信号を FIFO レジスタの末尾にプッシュします。[Num] 信号は、FIFO レジスタ内のデータ エントリの数を示します。FIFO にデータを書き込むたびに、[Num] 信号が 1 ずつインクリメントされます。タイム ステップ 6 で [write_en] が 1 になっています。次のタイム ステップ 7 でデータが FIFO に書き込まれます。[Num] 信号が 1 だけインクリメントされ、[Empty] フラグがデアサートされます。

FIFO は、[レジスタ サイズ] パラメーターで指定されたレジスタ サイズを使用します。既定では、レジスタ サイズは 10 です。図では、[Num] 信号がタイム ステップ 43 で 13 になると、[Full] 信号がアサートされます。FWFT モードでは、FIFO は指定されたサイズを超えてさらに 3 つの値を格納できます。[Full] 信号が 1 になった後、FIFO にエントリをさらに書き込むと、ブロックから警告が生成されます。

次の図は、[モード] パラメーターを FWFT に設定した場合の読み取り操作を示しています。読み取り操作では、[Pop] 入力端子がイネーブル信号として機能します。図では、[read_en] がこの信号を示しています。

FWFT モードでは、FIFO に書き込んだ最初の語が出力信号 [Out] に送られます。

この図では、[read-en] はタイム ステップ 42 で 1 になり、FIFO はタイム ステップ 9 で最初の語の [dout] を読み取っています。この機能を使用すると、FIFO に書き込まれた最初の語を先読みして確認できます。

[Num] 信号が 0 になると、[Empty] 信号がアサートされます。[Empty] 信号が 0 になった後、FIFO からエントリをさらに読み取ると、ブロックから警告が生成されます。

拡張機能

C/C++ コード生成

Simulink® Coder™ を使用して C および C++ コードを生成します。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加の構成オプションがあります。

このブロックには 1 つの既定の HDL アーキテクチャがあります。

| 一般 | |

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| SynthesisAttributes | モデル内のブロックとブロック出力信号の合成属性を指定します。生成された HDL コードには以下の属性が含まれます。詳細については、SynthesisAttributesを参照してください。 |

バージョン履歴

R2014a で導入[RAMDirective] HDL ブロック プロパティは削除されました。設計内の RAM ブロックをターゲット FPGA 上の RAM ブロックにマッピングするには、代わりに [SynthesisAttributes] HDL ブロック プロパティを使用します。

[SynthesisAttributes] HDL ブロック プロパティを使用して、ブロックとその出力信号の合成属性を指定します。HDL Coder により、生成された HDL コードにこれらの属性が含められます。

HDL FIFO ブロックの [In] 端子でベクトル データ型がサポートされるようになりました。ベクトル入力の次元を指定するには、[データ入力の次元] パラメーターを使用します。

このブロックで、Half 型または Boolean 型の入力データによる HDL コード生成がサポートされるようになりました。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)