Phase-Locked Loops

Design a PLL system starting from basic foundation blocks or from a family of reference architectures. Simulate and analyze the PLL system to verify key performance metrics until you meet the system specifications.

You can start by providing the specifications and impairments of each foundation block and connect the blocks to model different PLL architectural models (bottom-up approach). Alternatively, you can start from complete system-level models of typical PLL architectures and customize those models to meet your system specifications (top-down approach).

Use Measurements and Testbenches throughout the design process to verify the specifications of the blocks and of the entire system in presence of imperfections.

You can also analyze your models from the MATLAB® command line interface. For more information, see Analysis and Optimization.

Blocks

Topics

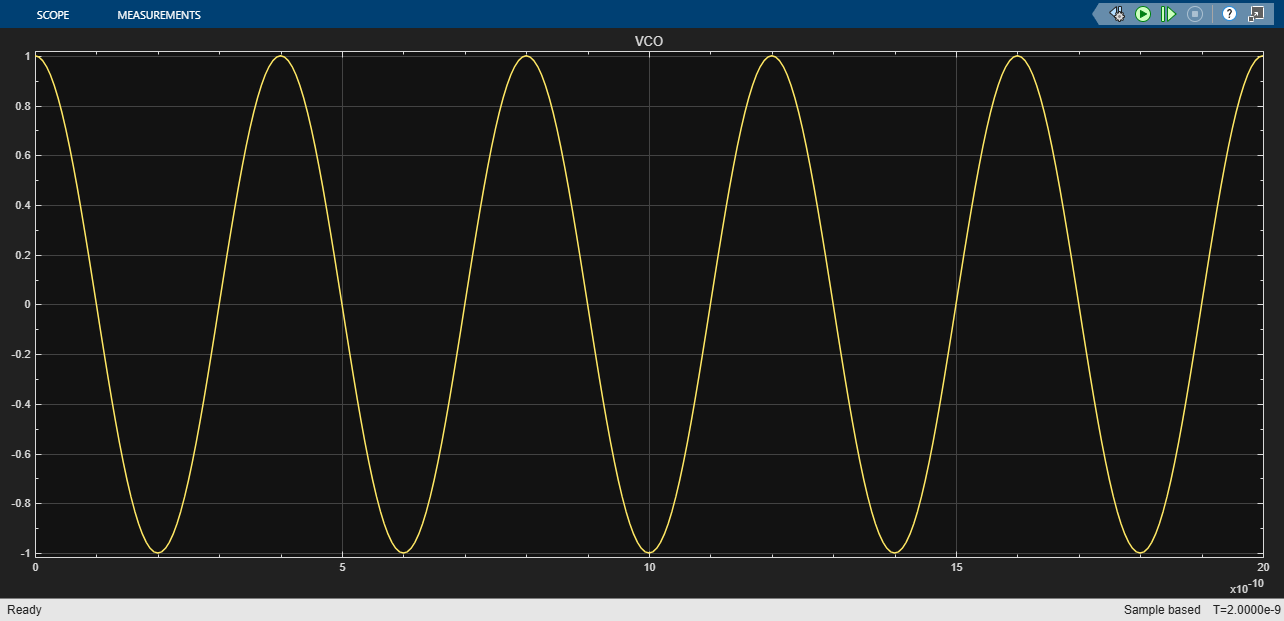

- Phase Noise in Oscillators

Learn how to obtain reliable phase noise data from an oscillator data sheet.