Dual Modulus Prescaler

Integer clock divider with two divider ratios

Libraries:

Mixed-Signal Blockset /

PLL /

Building Blocks

Description

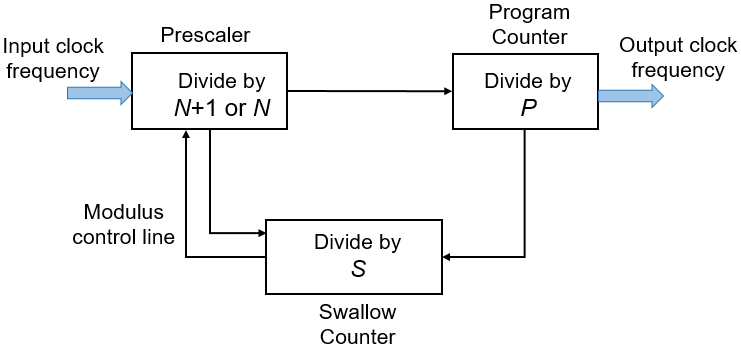

The Dual Modulus Prescaler subsystem block consists of a program counter, a swallow counter and a prescaler.

When the block first receives an input signal, the pulse swallow function is activated. The prescaler divides the input signal frequency by (N+1), where N is defined by the Prescaler divider value (N) parameter. Both the program and swallow counters start counting. The swallow counter resets after counting to S pulses, or (N+1)S cycles, where S is defined by the Swallow counter value (S) parameter. Then, the pulse swallow function is deactivated, and the prescaler divides the input frequency by N.

Since the program counter has already sensed S pulses, it requires (P-S) more pulses, or (P-S)N cycles to reach overflow, where P is defined by the Program counter value (P) parameter. The cycle repeats after both counters are reset.

The effective divider value of the dual modulus prescaler is the ratio of the input frequency to the output frequency:

Note

To prevent the program counter and prescaler from resetting prematurely before the swallow counter finishes counting, the condition must be met.

The dual modulus prescaler is also known as pulse swallow divider.

Examples

Ports

Input

Output

Parameters

More About

References

[1] Razavi, Behzad. RF Microelectronics. Upper Saddle River, NJ: Prentice Hall PTR, 1998.

Version History

Introduced in R2019a