このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

SystemVerilog と UVM テンプレート エンジン

MATLAB® 関数から統合検証方法論 (UVM) コンポーネントまたは SystemVerilog DPI コンポーネントを生成します。新しい svdpiConfiguration オブジェクトを使用して、コード生成に使用するテンプレートを指定します。オブジェクトのプロパティを設定して、テンプレート変数のデフォルト値を上書きすることもできます。次に、dpigen 関数を使用してコンポーネントを生成します。

一般的なコンポーネントの種類用の組み込みテンプレートを選択するか、独自のカスタム テンプレートを作成します。このテンプレート エンジンを使用する例については、テンプレートを使用して SystemVerilog DPI および UVM コンポーネントを作成する を参照してください。

メモ

この機能には ASIC Testbench for HDL Verifier アドオンが必要です。

汎用テンプレート

HDL Verifier™ は次の組み込みテンプレートを提供します。

Combinational module — このテンプレートは、MATLAB 関数の入力と出力をキャプチャします。これを使用して、クロック ポートやリセット ポートのない組み合わせ SystemVerilog モジュールを作成します。

これには次の変数が含まれます。

svdpiConfigurationオブジェクトのプロパティを設定して上書きします。ComponentTypeNameTestBenchTypeName

TemplateDictionaryプロパティを設定して上書きします。ComponentPackageTypeName

Sequential module — このテンプレートは、MATLAB 関数の入力と出力をキャプチャします。また、クロック、クロックイネーブル、リセット信号用のポートも追加されます。関数内に状態 (永続変数など) がある場合に、順次登録された SystemVerilog モジュールを作成するために使用します。永続変数の詳細については、永続変数 を参照してください。

シーケンシャル モジュール テンプレートには次の変数が含まれます。

svdpiConfigurationオブジェクトのプロパティを設定して上書きします。ComponentTypeNameTestBenchTypeName

TemplateDictionaryプロパティを設定して上書きします。ComponentPackageTypeName

Sequential module with variable-size outputs — このテンプレートは機能的にはシーケンシャル モジュール テンプレートと同じですが、可変サイズのポートに対応しています。関数への入力または出力の 1 つ以上が可変サイズのベクトルとして定義されている場合は、このテンプレートを使用します。このテンプレートは、それぞれのポートを SystemVerilog オープン配列 ([ ]) として持つ SystemVerilog モジュールを作成します。このコードは、

fooという名前の関数に対して生成されたインターフェースを示しており、in1とyを可変サイズのポートとして宣言しています。module foo_dpi( input bit clk, input bit clk_enable, input bit reset, input real in1 [], output shortint y [] );

このテンプレートには次の変数が含まれています。

svdpiConfigurationオブジェクトのプロパティを設定して上書きします。ComponentTypeNameTestBenchTypeName

TemplateDictionaryプロパティを設定して上書きします。ComponentPackageTypeName

UVM テンプレート

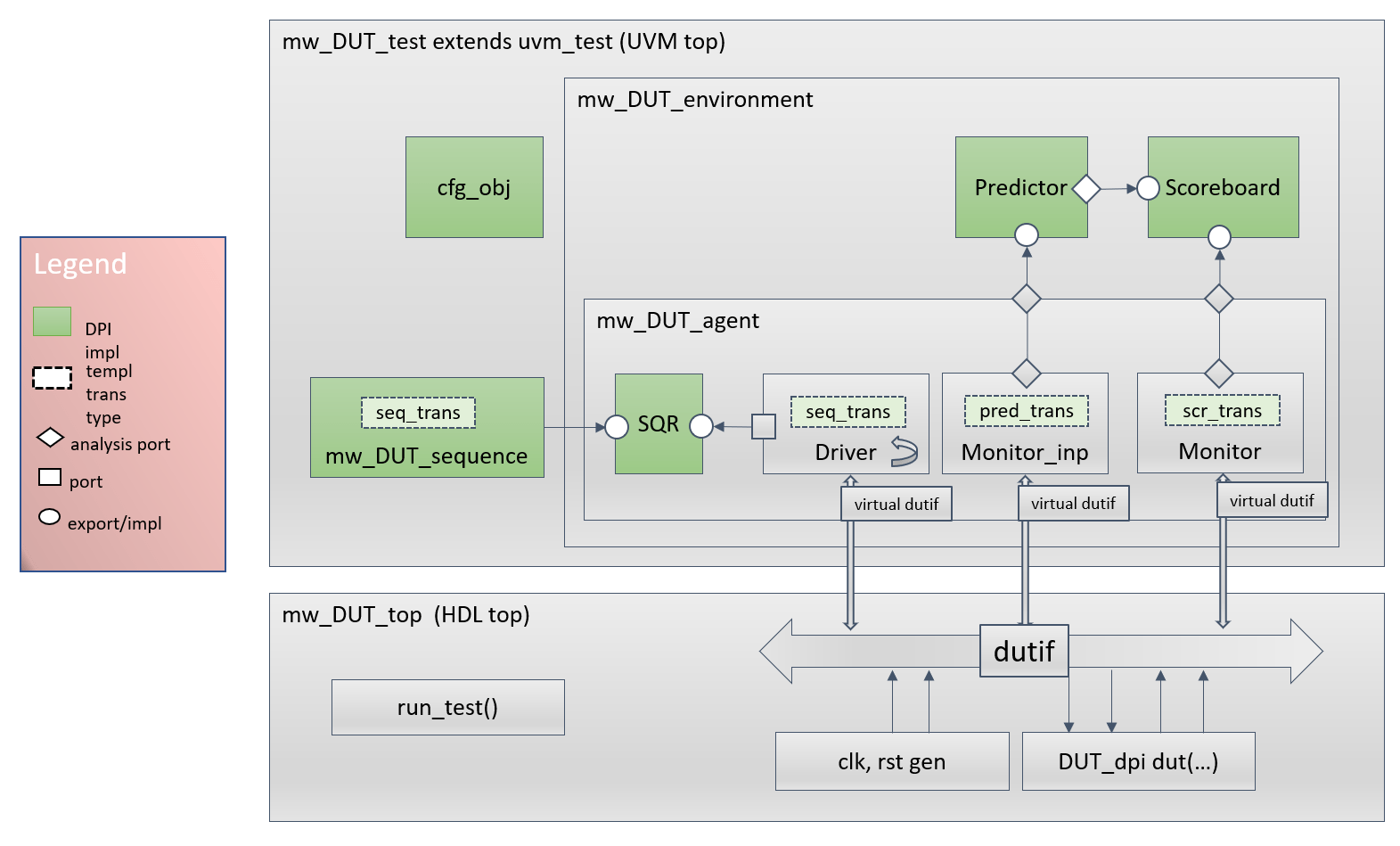

これらのテンプレートは、MATLAB 関数から UVM コンポーネントを生成し、完全な UVM テスト ベンチに統合できます。この画像は UVM テストベンチの構造を示しています。UVM テンプレートを使用すると、緑色で強調表示された部分を生成できます。

Predictor component — このテンプレートは UVM 予測モジュールを生成します。このモジュールには、予測トランザクションを入力するエクスポートと、スコアボード トランザクションを出力する分析ポートがあります。

予測テンプレートには次の変数が含まれます。

svdpiConfigurationオブジェクトのプロパティを設定して上書きします。ComponentTypeNameTestBenchTypeName

TemplateDictionaryプロパティを設定して上書きします。ComponentPackageTypeNameInputTransTypeNameOutputTransTypeName

オプションで、

addPortGroupオブジェクト関数を使用してポートをポート グループにマップできます。PREDICTOR_INPUTSCONFIG_OBJECT_INPUTS

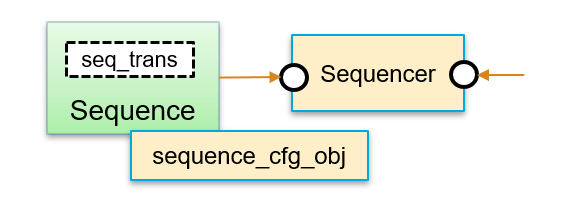

Sequence component — このテンプレートは UVM シーケンス モジュールを生成します。このモジュールには、予測トランザクションを入力するエクスポートと、スコアボード トランザクションを出力する分析ポートがあります。

シーケンス テンプレートには次の変数が含まれます。

svdpiConfigurationオブジェクトのプロパティを設定して上書きします。ComponentTypeNameTestBenchTypeName

TemplateDictionaryプロパティを設定して上書きします。ComponentPackageTypeNameSequenceTransTypeNameSequencerTypeNameSequenceCountSequenceFlushCount

オプションで、

addPortGroupオブジェクト関数を使用してポートをポート グループにマップできます。SEQUENCE_INPUTSCONFIG_OBJECT_INPUTS

Scoreboard component — このテンプレートは、UVM スコアボード モジュールとスコアボード構成オブジェクトを生成します。モジュールには、スコアボード トランザクションを入力する 2 つのエクスポートがあります。

スコアボード テンプレートには次の変数が含まれます。

svdpiConfigurationオブジェクトのプロパティを設定して上書きします。ComponentTypeNameTestBenchTypeName

TemplateDictionaryプロパティを設定して上書きします。ComponentPackageTypeNameInputTransTypeNameOutputTransTypeNameConfigObjTypeName

addPortGroupオブジェクト関数を使用して、ポートをポート グループにマップします。PREDICTOR_INPUTSMONITOR_INPUTSCONFIG_OBJECT_INPUTS

テストベンチテンプレート

dpigen 関数は、-testbench 引数を指定して呼び出されると、テストベンチ テンプレートを使用します。dpigen 関数は MATLAB 関数をシミュレートし、入力と出力を記録します。次に、dpigen 関数は、生成された SystemVerilog コンポーネント (DUT) をインスタンス化し、ログに記録された入力を DUT に駆動し、DUT 出力を MATLAB シミュレーションからのログに記録された出力と比較する SystemVerilog テスト ベンチ モジュールを生成します。このオプションは、生成された SystemVerilog モジュールが元の MATLAB 関数と同等であることを保証します。

次の組み込みテストベンチ テンプレートが利用可能です。

組み合わせテストベンチ

シーケンシャルテストベンチ

可変サイズ出力を備えたシーケンシャルテストベンチ

予測テストベンチ

シーケンステストベンチ

スコアボードテストベンチ