このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

SystemVerilog DPI テストベンチ

HDL Verifier™ は、C 言語コンポーネントを生成し、それをダイレクト プログラミング インターフェイス (DPI) を使用して SystemVerilog テスト ベンチに統合する 2 種類のテスト ベンチを提供します。1 つのテスト ベンチは、生成された C コンポーネントを Simulink® サブシステムから保存されたデータ ベクトルに対して検証します。もう一方のテスト ベンチは、生成された HDL コードを、Simulink モデル全体から生成された C コンポーネントに対して検証します。

コンポーネント テスト ベンチ — DPI コンポーネントとして使用するために Simulink サブシステムから C コンポーネントを生成する場合、オプションで SystemVerilog テスト ベンチを生成できます。テスト ベンチは、生成された DPI コンポーネントを Simulink モデルのデータ ベクトルに対して検証します。この機能は、[モデル構成パラメータ] ダイアログ ボックスの [Code Generation] で使用できます。SystemVerilog DPIコンポーネントを生成するを参照してください。

HDL コード テスト ベンチ — HDL Coder™ を使用してサブシステムから HDL コードを生成する場合、オプションで SystemVerilog テスト ベンチを生成できます。このテスト ベンチは、HDL 実装の出力を Simulink モデルの結果と比較します。この機能には、HDL ワークフロー アドバイザーの [HDL コード生成] 、 [テスト ベンチ オプションを設定]、または [モデル コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [テスト ベンチ] からアクセスできます。あるいは、コマンドライン アクセスの場合は、

makehdltb(HDL Coder) のGenerateSVDPITestBenchプロパティを設定します。Verify HDL Design Using SystemVerilog DPI Test Bench (HDL Coder)を参照してください。

どちらのタイプのテストベンチにも、Simulink Coder™ ライセンスと ASIC Testbench for HDL Verifier アドオンが必要です。

制限

HDL Verifier は、SystemVerilog で行列とベクトルを 1 次元配列に変換します。たとえば、Simulink の 4 行 2 列の行列は、SystemVerilog では 8 要素の 1 次元配列に変換されます。

以下のサブシステムは DPI テストベンチの生成をサポートしていません。

トリガーサブシステム

有効なサブシステム

アクションポート付きサブシステム

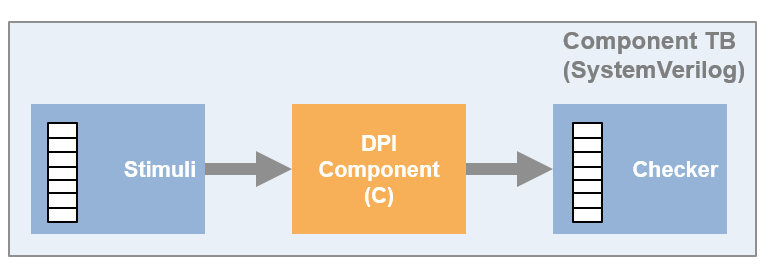

コンポーネントテストベンチ

SystemVerilog DPI コンポーネント ジェネレーターはテスト ベンチも作成します。このテスト ベンチを使用すると、生成された SystemVerilog コンポーネントが元の Simulink サブシステムと機能的に同等であることを確認できます。テスト ベンチは、Simulink シミュレーションからのデータ ベクトルを保存し、刺激として適用し、コンポーネントの出力と照合します。このテスト ベンチは、独自のアプリケーション用のシステム テスト ベンチの代わりとして使用することを意図したものではありません。ただし、生成されたテスト ベンチを独自のシステム テスト ベンチの開始例として使用できます。

モデル内のテスト ポイントでログ記録を有効にすると、生成されたテスト ベンチは、SystemVerilog コンポーネント内の信号値を Simulink から記録された値と比較します。

メモ

HDL Verifier は、カスタム生成された SystemVerilog コードのテストベンチ生成をサポートしていません。カスタマイズを参照してください。

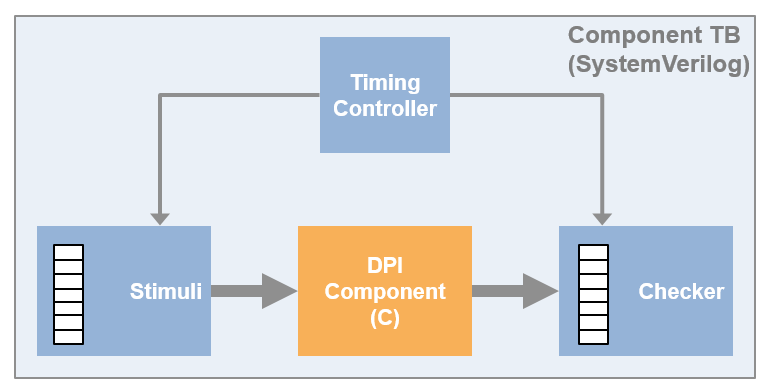

マルチレートコンポーネントテストベンチ

サブシステムに複数のサンプル レートを持つ信号が含まれている場合、生成されたテスト ベンチにはタイミング コントローラー モジュールが含まれます。タイミング コントローラは適切なレートで入力クロック信号を生成します。入力刺激と予想されるデータ出力は、サンプル レートに応じて適用され、チェックされます。

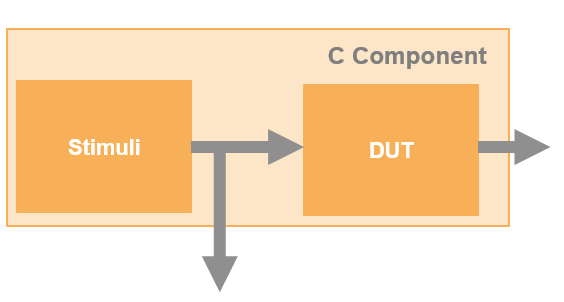

HDL コード テストベンチ

HDL Coder を使用してサブシステムから HDL コードを生成すると、SystemVerilog DPI テストベンチも生成できます。このテスト ベンチは、HDL 実装の出力を Simulink モデルの結果と比較します。コーダは、DUT サブシステムの C コードに加えて、入力刺激を生成するモデルの部分の C コードも生成します。このテストベンチの生成は、大規模なデータ セットのデフォルトの HDL テストベンチよりも高速です。この利点は、コーダが入力データ ベクトルと出力データ ベクトルを取得するために Simulink モデルを実行しないためです。生成された C コンポーネントは、入力刺激と出力結果を計算して、HDL 実装と比較します。

生成された SystemVerilog テストベンチには以下が含まれます。

サブシステム用に生成された Verilog® または VHDL® コード

生成されたCコンポーネント

HDL コードの出力と C コンポーネントの出力を比較するコード。

このテストベンチを実行して、生成された HDL コードが Simulink モデルと同じアルゴリズムを実装していることを確認します。