このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

クロスプラットフォームUVMコンポーネントを生成する

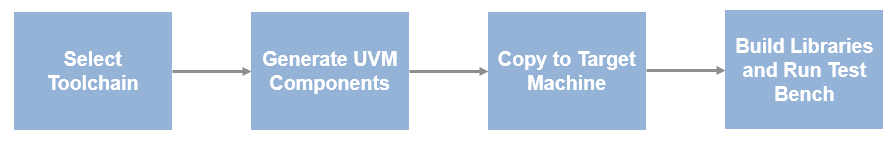

Simulink® 環境から UVM フレームワークに直接移行するための Universal Verification Methodology (UVM) コンポーネントを生成します。HDL Verifier™ は、ダイレクト プログラミング インターフェイス (DPI) を使用して、UVM コンポーネント内に生成された C コードとして Simulink サブシステムをエクスポートします。生成されたこれらのコンポーネントを既存の UVM 環境に統合できます。生成された動作 DUT を詳細な HDL 設計に置き換えることにより、生成された UVM テスト ベンチを使用して HDL DUT をテストすることもできます。

Windows® 64 ホスト マシンから UVM コンポーネントを生成する場合は、コンポーネント ライブラリを構築し、Linux® オペレーティング システムでシミュレーションを実行することもできます。ターゲットとホストが同じでない場合は、共有ライブラリまたは HDL シミュレータ プロジェクトを手動で移植してビルドする必要があります。Linux マシンで生成された UVM コンポーネントを他のオペレーティング システムに移植することはできません。

このワークフローは、Cadence® Xcelium™、Mentor Graphics® ModelSim®、Mentor Graphics Questa®、および Synopsys® VCS® HDL シミュレータをサポートします。

メモ

この機能には ASIC Testbench for HDL Verifier アドオンが必要です。

ターゲットツールチェーンを選択

ターゲット マシンがホストと同じオペレーティング システムを使用している場合は、インストールされているコンパイラを選択するか、ツールがコンパイラを自動的に検出するように要求できます。シミュレータ プロジェクトを生成する場合、または他のコンパイラがインストールされていない場合は、ホストと同じオペレーティング システムの HDL シミュレータを選択します。ただし、ターゲット オペレーティング システムがホストと異なる場合は、ターゲット シミュレーターとオペレーティング システムを選択する必要があります。

UVM 生成では SystemVerilog DPI を生成するテクノロジが利用されるため、まずサポートするシステム ターゲット ファイルを選択する必要があります。モデルを開き、Apps タブで HDL Verifier をクリックします。左側のペインで DPI Component Generation を選択し、HDL Verifier タブで C Code Settings をクリックします。Configuration Parameters ダイアログが Code Generation ペインに開きます。Target selection の システム ターゲット ファイル で、Browse をクリックし、リストから systemverilog_dpi_grt.tlc を選択します。

あるいは、Embedded Coder® 製品をお持ちの場合は、ターゲット systemverilog_dpi_ert.tlc を選択できます。このターゲットを使用すると、Configuration Parameters ダイアログ ボックスの左ペインから Code Generation を選択したときに、追加のコード生成オプションにアクセスできます。UVM 生成の例については、Simulink からパラメータ化された UVM テストベンチを生成する を参照してください。

次に、Build process の下でターゲット Toolchain を選択します。このオプションは、シミュレーションを実行するターゲット シミュレーターとオペレーティング システムを指定します。サポートされているクロスプロダクト ツールチェーンは次のとおりです。

Cadence Xcelium (64-bit Linux)Mentor Graphics ModelSim/QuestaSim (64-bit Linux)Synopsys VCS (64-bit Linux)

別のオペレーティング システム用の共有ライブラリを構築するには、シミュレータ オプションのいずれかを選択する必要があります。その後、ターゲット マシン上でライブラリをビルドできます。

コンポーネントの生成

uvmbuild 関数を使用して、UVM コンポーネントの構造を生成します。この関数は、DUT、シーケンス、スコアボード サブシステムから SystemVerilog DPI (SV-DPI) コンポーネントを生成します。また、モデルに含まれている場合は、ドライバー、モニター、または予測サブシステムのオプションの SV-DPI コンポーネントも生成します。この関数は、Simulink モデルから UVM テスト ベンチも生成します。この関数は、作業ディレクトリ内の uvm_build.zip という名前のディレクトリに DPI 生成の成果物をパッケージ化します。このディレクトリには次の 2 つのディレクトリが含まれます。

top_model_dpi_componentstop_model_uvm_testbench

ここで、top_model

uvmcodegen.uvmconfig 構成オブジェクトの buildDirectory プロパティを設定することで、デフォルトのディレクトリを変更できます。

ターゲットマシンにコピー

生成されたコンポーネントを別のオペレーティング システムで使用するには、生成されたパッケージ ファイルをターゲット マシンにコピーし、解凍して、そこでコンポーネント ライブラリを構築する必要があります。

生成された

uvm_build.zipファイルをホスト マシンからターゲット マシンにコピーします。.zipファイルはモデルと同じフォルダーにあります。.zipファイルには、.do拡張子を持つ ModelSim ファイル、または.sh拡張子を持つ VCS または Xcelium ファイルが含まれます。ファイルを任意のフォルダに解凍します。

ライブラリを構築してテストベンチを実行する

ホスト マシン上でコンポーネントを生成すると、そのオペレーティング システム用のライブラリが構築されます。コンポーネントを別のオペレーティング システムに移植するには、ターゲット マシン上でコンポーネントを手動でビルドする必要があります。プロジェクトをビルドし、HDL シミュレーターでテストベンチを実行するには、表で HDL シミュレーターを見つけて、指示に従います。

| HDL シミュレーター | 手順 |

|---|---|

| ModelSim または Questa |

|

| VCS |

|

| Xcelium |

|

制限

Simulink モデルの参照サブシステムに Test Assessment (Simulink Test) ブロックがある場合、クロスプラットフォーム UVM 生成ではモデル参照がサポートされません。