このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

Xilinx Zynq SoC デバイス向け Ethernet AXI マネージャー

メモ

Ethernet AXI マスターは Ethernet AXI マネージャーに名前が変更されました。ソフトウェアとドキュメントでは、「マスター」と「スレーブ」という用語がそれぞれ「マネージャー」と「従属」に置き換えられます。

Xilinx® FPGA ボード用の HDL Verifier™ サポート パッケージ 機能を実装するには、ホスト コンピュータとハードウェアを適切に通信できるように構成する必要があります。サポート パッケージをインストールした後、次の手順に従ってハードウェアを手動でセットアップします。

完全なハードウェアチェックリスト

ハードウェアのセットアップを完了するために必要なハードウェアとアクセサリがすべて揃っていることを確認します。

ギガビット イーサネット接続 – この接続は、多くの場合、ネットワーク接続と呼ばれます。ギガビット イーサネット ケーブルを備えた統合ネットワーク インターフェイス カード (NIC) またはユニバーサル シリアル バス (USB) 3.0 ギガビット イーサネット アダプタ ドングルのいずれかを使用できます。この接続は、プログラミング ファイルなどのデータをホスト コンピューターからハードウェアに送信するために必要です。ハードウェアとの間で信号を送受信するためにも必要です。

SD カード リーダーと書き込み可能な SD カード - ホスト マシンにカード リーダーが内蔵されていない場合は、外付け USB SD カード リーダーを使用します。

サポートされているハードウェア – この機能は、Xilinx Zynq®-7000 ZC706 および Xilinx Zynq ZedBoard™ ボードをサポートします。後の手順でプロンプトが表示されるまで、デバイスを接続したり電源を入れたりしないでください。

イーサネット ケーブル - このケーブルはハードウェアをホストに接続します。

ホストコンピュータを構成する

ハードウェアをホストに接続するには、ホスト上のハードウェアに対して使用可能なネットワーク接続を構成する必要があります。特定のオペレーティング システムに応じた手順に従ってください。

Windows を設定する

Windows® 7 以降の場合は、次の手順に従ってください。

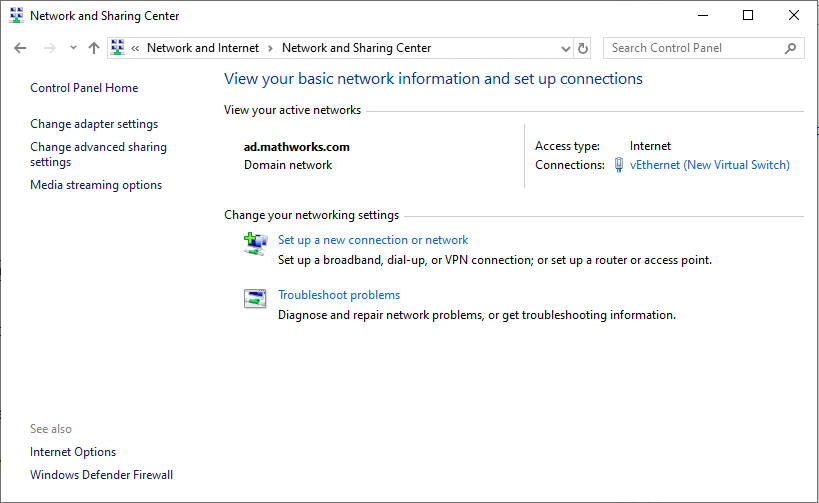

Start メニューから、Control Panel をクリックします。

View by を

Categoryに設定します。Network and Internetをクリックします。

Network and Sharing Centerをクリックします。

左側のペインで、Change adapter settings をクリックします。

ハードウェアに接続されているローカル エリア ネットワーク接続を右クリックし、Properties を選択します。

未使用のネットワーク接続が利用可能な場合、ローカル エリア接続は

Unidentified networkとして表示されます。ネットワーク接続を再利用する予定の場合は、ハードウェアに使用する予定のローカル エリア接続を選択します。

ネットワーク接続が 1 つしかない場合は、既存のローカル エリア ネットワークにワイヤレスで接続できるかどうかを確認します。ハードウェアのネットワーク接続を使用できます。

NIC の代わりに、プラグ可能な USB からギガビット イーサネット LAN アダプターを使用できます。

[プロパティ] ダイアログ ボックスの [Networking] タブで、[Internet Protocol Version 4 (TCP/IPv4)] 以外のすべてのオプションをオフにします。その他のサービス、特にウイルス対策ソフトウェアは、ハードウェアとの接続に断続的な問題を引き起こす可能性があります。

Internet Protocol Version 4 (TCP/IPv4)をダブルクリックします。

General タブで、Use the following IP address を選択します。

ハードウェアのデフォルトの IP アドレスは

192.168.0.2です。ホスト ネットワーク接続は、ハードウェアと同じサブネット上にある必要があります。この要件を満たすには、互換性のある IP アドレスをホスト ネットワーク接続に割り当てる必要があります。ホスト ネットワーク IP アドレスを 192.168.0.xに設定します。ここで、xは 1 または [3, 255] の範囲の整数です。

IP アドレス フィールドの最初の 3 オクテットが 192.168.0 でない場合、ハードウェアは別のサブネット上にあります。IP アドレスに同じサブネット番号を入力します。

サブネット マスクはデフォルト値の

255.255.255.0のままにしておきます。[OK] をクリックします。

Linux を設定する

ホスト イーサネット インターフェイスに静的 IP アドレスを設定します。この構成により、ハードウェアとの通信が可能になります。ハードウェアのデフォルトの IP アドレスは 192.168.0.2 です。ホスト ネットワーク接続は、ハードウェアと同じサブネット上にある必要があります。この要件を満たすには、ホスト ネットワーク接続に互換性のある IP アドレスを割り当てる必要があります。

ホスト ネットワーク IP アドレスを 192.168.0.

xに設定します。ここで、xは 1 または [3, 255] の範囲の整数です。この値は、ifconfigコマンドを使用して設定します。たとえば、シェルにこのコマンドを入力します。% sudo ifconfig ethZ 192.168.0.4 netmask 255.255.255.0

この構文では、

ethはホスト イーサネット ポートの名前です (通常は eth0、eth1 など)。Zsudoコマンドを使用するには、パスワードを入力する必要がある場合があります。シェルにこのコマンドを入力して変更を確認します。

% ifconfig ethZ

ethは、前の手順で設定したホスト イーサネット ポートの名前です。Z

ホストシステムのSDカードにイメージをコピーする

このサポート パッケージのファームウェアが構成された SD メモリ カードが必要です。ファームウェアには、ハードウェアを I/O 周辺機器として使用するために必要な組み込みソフトウェアと FPGA プログラミング ファイルが含まれています。必要なイメージが入った SD カードをすでにコピーしている場合は、この手順をスキップしてください。

4 GB 以上の SD メモリ カードをホスト コンピューターのメモリ カード リーダーに挿入します。

copyImageToHostSDCardPath関数を使用して、ボード固有の SD カード イメージ ファイルをホスト システム内の指定された SD カード ドライブの場所にコピーします。SD カードのイメージ ファイルには、ブートローダーとサポートされているオペレーティング システムの情報が含まれています。この関数は、ターゲット SoC デバイス上で AXI マネージャー ホスト コマンドを処理するためのサーバー デーモンもコピーします。デフォルトの SD カード イメージは、Xilinx FPGA ボード用の HDL Verifier サポート パッケージ に付属する SD カード ファイルです。カスタム SD カード イメージは、ユーザーが作成した SD カード ファイルです。

例

デフォルトの IP アドレスを持つ Xilinx Zynq-7000 ZC706 ボードの Windows プラットフォーム上のホスト コンピューター上の指定された場所にデフォルトの SD カード イメージをコピーするには、MATLAB コマンド プロンプトでこのコードを入力します。

copyImageToHostSDCardPath('ZC706','G:');

カスタム IP アドレスを持つ Xilinx Zynq-7000 ZC706 ボードのデフォルトの SD カード イメージをホスト コンピューターの指定された場所にコピーし、Linux プラットフォームでゲートウェイを指定するには、MATLAB コマンド プロンプトでこのコードを入力します。ホスト NIC アドレスを

192.168.10.xに設定します。ここで、x は [1, 3] または [5, 255] の範囲の整数である必要があります。copyImageToHostSDCardPath('ZC706','/media/username/261D-2F2B', ... 'DeviceAddress','192.168.10.4','Gateway','192.168.10.1');

Windows プラットフォームでデフォルトの IP アドレスを持つ Xilinx Zynq-7000 ZC706 ボードのカスタム SD カード イメージをホスト コンピューターの指定された場所にコピーするには、MATLAB コマンド プロンプトでこのコードを入力します。

このコマンドを実行する前に、カスタム SD イメージが

.zip、.tgz、.gzなどの zip 形式である場合は、zip 形式のファイルをホスト システム内の特定のフォルダーまたはディレクトリに抽出します。copyImageToHostSDCardPath('ZC706','G:','SDCardImage', ... 'C:\mywork\hdlv_prj\sdcard_image\zc706_sdcard_zynq7000');

SoC デバイスで SD カード イメージを更新する (オプション)

ホストシステムのSDカードにイメージをコピーする のプロセスを使用して SD カードのイメージ ファイルをすでにコピーしている場合は、この手順をスキップしてください。

loadImageToTargetSDCardPath 関数を使用して、SoC デバイス内の SD カード イメージを更新します。この手順を続行する前に、SD カードがターゲット SoC デバイスの SD カードの場所に挿入されていること、およびホスト システムとターゲット SoC デバイスの間にイーサネット接続が確立されていることを確認してください。

この関数は、SoC デバイス内の既存のボード固有の SD カード イメージ ファイルを更新します。SD カードが更新されるまで、少なくとも 20 秒待つ必要がある場合があります。

例

デフォルトの SD カード イメージをターゲット SoC デバイスの SD カードの場所にコピーするには、MATLAB コマンド プロンプトでこのコードを入力します。

loadImageToTargetSDCardPath('ZC706');Windows プラットフォームでデフォルトの IP アドレスを持つ Xilinx Zynq-7000 ZC706 ボードのカスタム SD カード イメージをターゲット SoC デバイスの SD カードの場所にコピーするには、MATLAB コマンド プロンプトでこのコードを入力します。

このコマンドを実行する前に、カスタム SD イメージが .zip、.tgz、.gz などの zip 形式である場合は、zip 形式のファイルをホスト システム内の特定のフォルダーまたはディレクトリに抽出します。

loadImageToTargetSDCardPath('ZC706','SDCardImage', ... 'C:\mywork\hdlv_prj\sdcard_image\zc706_sdcard_zynq7000');

デフォルト値とは異なる IP アドレスを持つ Xilinx Zynq-7000 ZC706 ボードのデフォルトの SD カード イメージをホスト コンピューター上の指定された場所にコピーするには、MATLAB コマンド プロンプトでこのコードを入力します。

loadImageToTargetSDCardPath('ZC706', ... 'DeviceAddress','192.168.10.2','Gateway','192.168.10.1');

DTB ファイルの生成

次の手順に従って、SoC デバイスのデバイス ツリー BLOB (DTB) ファイルを生成します。

ターゲット SoC デバイスで実行されている Linux® オペレーティング システムにログインします。

/mntパスに移動します。ターミナルでこのコマンドを入力して、既存の DTB ファイルを対応する人間が判読可能なデバイス ツリー ソース (DTS) ファイルに変換します。

dtc -I dtb -O dts dtb_file.dtb -o devicetree.dts

ここで、

dtb_filedevicetree.dtb)。DTB ファイルを生成するには、Linux オペレーティング システム上にデバイス ツリー コンパイラ (DTC) が必要です。DTC がインストールされていない場合は、DTC ソース コードを取得して ARM® にクロスコンパイルします。

ターミナルでこのコマンドを入力して、変換された DTS ファイルを開きます。

vi devicetree.dts

DTS ファイルを編集して FPGA メモリ情報を提供します。

例

これらの例の設計アドレス マッピングは、次の個別のメモリ マップ領域で構成されます。

メモリマップ領域 ベースアドレス 範囲 PS DDR — mw_psddr_mem0 0x14000000 0x4000000 (64 MB) ブラム — mw_axi_bram_ip0 0x40000000 0x80000 (512 KB) PL DDR — mw_plddr_mem0 0x60000000 0x1000000 (16MB)  32 ビット ARM Cortex-A9 ベースの Zynq SoC デバイスのデバイス ツリー ノード

32 ビット ARM Cortex-A9 ベースの Zynq SoC デバイスのデバイス ツリー ノード 64 ビット ARM Cortex-A53 ベースの MPSoC デバイスのデバイス ツリー ノード

64 ビット ARM Cortex-A53 ベースの MPSoC デバイスのデバイス ツリー ノードホスト Linux マシン上で DTB ファイルをコンパイルし、DTS ファイルを編集することもできますが、コンパイル中にいくつかの警告が表示されます。このような警告は無視できます。

DTS ファイルを編集した後、DTB ファイルを生成するには、ターミナルにこのコマンドを入力します。

dtc -I dts -O dtb devicetree.dts -o devicetree_sharedmem_iio.dtb

DTB の生成が正常に完了したら、

devicetree_sharedmem_iio.dtbファイルをターゲット SoC デバイスの/mntファイル システム パスからホスト マシンのホーム ディレクトリ パスに転送します。

これで、変更された DTB ファイルをターゲット SoC デバイスにロードできます。loadBitstream 関数を使用して、カスタム FPGA ビットストリームと DTB ファイルをロードします。

ビットストリームファイルをSoCデバイスにロードする

loadBitstream 関数は、ターゲット SoC デバイスにロードする新しい FPGA デザインがある場合にのみ使用してください。それ以外の場合は、この手順をスキップしてください。

この関数は、カスタム FPGA ビットストリーム ファイルとそれに対応する DTB ファイルをターゲット SoC デバイスにロードします。変更がターゲット SoC デバイスに更新されるまで、少なくとも 20 秒待つ必要がある場合があります。

例

デフォルトの IP アドレスを持つ Xilinx Zynq-7000 ZC706 ボードのターゲット SoC デバイスにカスタム FPGA ビットストリームとそれに対応する DTB ファイルをロードするには、MATLAB コマンド プロンプトでこのコードを入力します。

loadBitstream('ZC706','C:\mywork\hdlv_bitstreams\system.bit', ... 'C:\mywork\hdlv_bitstreams\devicetree.dtb');

デフォルト値とは異なる IP アドレスを持つ Xilinx Zynq-7000 ZC706 ボードのターゲット SoC デバイスにカスタム FPGA ビットストリームとそれに対応する DTB ファイルをロードするには、MATLAB コマンド プロンプトでこのコードを入力します。

loadBitstream('ZC706','C:\mywork\hdlv_bitstreams\system.bit', ... 'C:\mywork\hdlv_bitstreams\devicetree.dtb', ... 'DeviceAddress','192.168.10.2');

プログラムが FPGA ボード上で実行されると、aximanager オブジェクトを使用して AXI マネージャー オブジェクトを作成できます。ボード上の下位メモリ位置にアクセスするには、このオブジェクトの readmemory および writememory オブジェクト関数を使用します。

参考

copyImageToHostSDCardPath | loadImageToTargetSDCardPath | loadBitstream | aximanager