AMD FPGA ボード向けの IP コアの生成ワークフロー

サポートされている任意の AMD® FPGA デバイス向けに再利用可能な HDL IP コアを生成できます。このワークフローでは、ターゲット インターフェイス構成および指定するコード生成設定が表示される IP コア レポートが生成されます。カスタム IP コアの生成を参照してください。

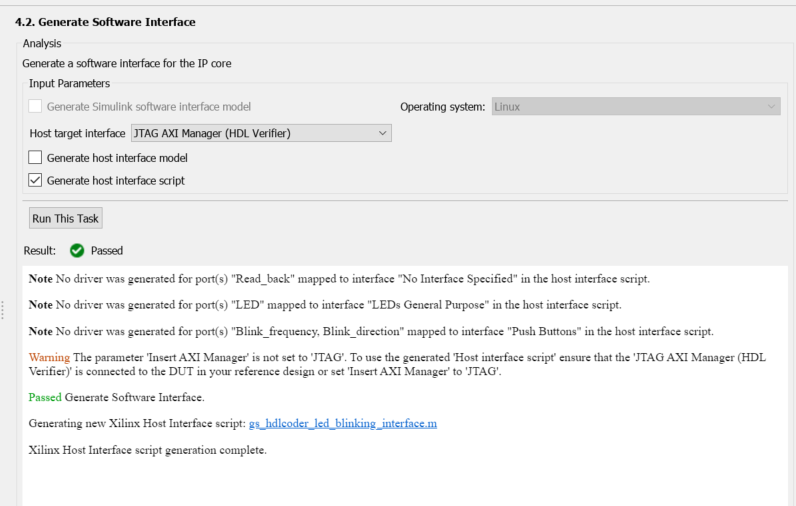

オプションで独自のカスタム リファレンス設計を作成して、生成された IP コアをリファレンス設計に統合できます。このワークフローには Embedded Coder® ソフトウェアは必要ありません。プロセッサ上で実行される組み込みコードを生成する必要がないためです。これは、ワークフローに [ソフトウェア インターフェイス モデルを生成] タスクがないことを意味します。

FPGA ボードのワークフローには、以下の機能があります。

[ターゲットのリファレンス設計を設定] タスク。リファレンス設計、そのツールのバージョン、指定するパラメーターが事前設定されます。

[ターゲット インターフェイスを設定] タスク。DUT ポートをターゲット プラットフォーム上のインターフェイスにマッピングします。

[ターゲット周波数を設定] タスク。その周波数をもつクロック信号を生成するリファレンス設計のクロック モジュールを変更するために、[ターゲット周波数 (MHz)] を指定します。

[RTL コードと IP コアの生成] タスク。再利用可能で、共有可能な IP コアを生成します。IP コアは、RTL コード、C ヘッダー ファイル、および IP コア定義ファイルをパッケージ化します。

[プロジェクトを作成] タスク。IP コアを事前定義されたリファレンス設計に統合するためのプロジェクトを作成します。

オプションの AXI4 または AXI4-Lite インターフェイスをもつ IP コアを生成できます。

AXI4 インターフェイスをもつ FPGA リファレンス設計をターゲットにする

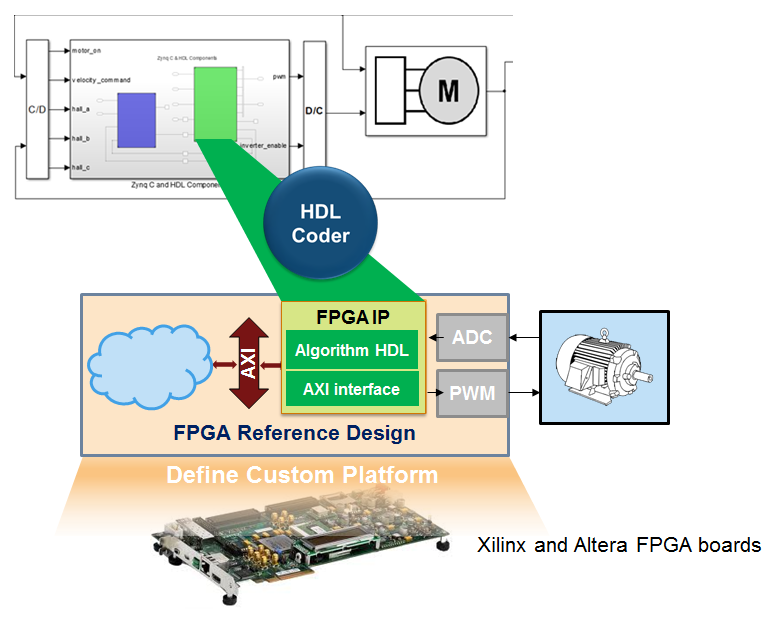

次の図は、HDL Coder™ が AXI4 インターフェイスをもつ IP コアを生成する方法および IP コアを FPGA リファレンス設計に統合する方法を示しています。ボードおよびリファレンス設計の登録システムを参照してください。

HDL Coder を使用して、生成した AXI4-Lite インターフェイスを以下の AXI4 または AXI4-Lite マスター デバイスをもつ IP コアに接続します。

MicroBlaze プロセッサ。

Nios II プロセッサ。

外部プロセッサに接続する PCIe エンドポイント。

JTAG Master。

HDL IP コアを MicroBlaze などのプロセッサに接続する場合、プロセッサ上で実行するには手書きの C コードを統合しなければなりません。生成された IP コア レポートは、レジスタ アドレスのマッピング情報を表示します。IP コアのレジスタ スペースでレジスタ オフセットを検出するには、このマッピング情報を使用します。各レジスタのメモリ アドレスを取得するには、リファレンス設計で指定するベース アドレスにレジスタ オフセットを追加します。生成された IP コア フォルダーの C ヘッダー ファイルにあるレジスタ オフセットを検出することもできます。

AXI4 インターフェイスのない FPGA リファレンス設計をターゲットにする

リファレンス設計定義関数で、AXI4 レジスタ インターフェイスのない独自のカスタム リファレンス設計を作成できます。addRegisterInterfaceも参照してください。

カスタム リファレンス設計を作成するときに、スタンドアロン FPGA ボードをターゲットにする場合、hdlcoder.ReferenceDesign クラスの EmbeddedCoderSupportPackage メソッドを使用します。

hRD.EmbeddedCoderSupportPackage = ...

hdlcoder.EmbeddedCoderSupportPackage.None;EmbeddedCoderSupportPackageを参照してください。ボードのサポート

HDL Coder は、[IP Core Generation] ワークフローで次の FPGA ボードをサポートします。

Xilinx Kintex-7 KC705 開発ボード

これらのボードを使用して、生成された IP コアを [default system] のリファレンス設計に統合できます。既定では、このリファレンス設計にはレジスタ インターフェイスはありません。オプションで、リファレンス設計定義関数にインターフェイスを追加できます。