このページは前リリースの情報です。該当の英語のページはこのリリースで削除されています。

HDL Coder での Xilinx System Generator for DSP の使用

この例では、HDL Coder™ での Xilinx® System Generator for DSP の使用方法を示します。

はじめに

Xilinx System Generator Subsystem ブロックを使用すると、Simulink® と Xilinx の両方のブロックを使用した設計をモデル化し、統合された HDL コードを自動的に生成できます。HDL Coder™ で、Simulink ブロックから HDL コードが生成され、さらに Xilinx System Generator を使用して Xilinx System Generator Subsystem ブロックから HDL コードが生成されます。

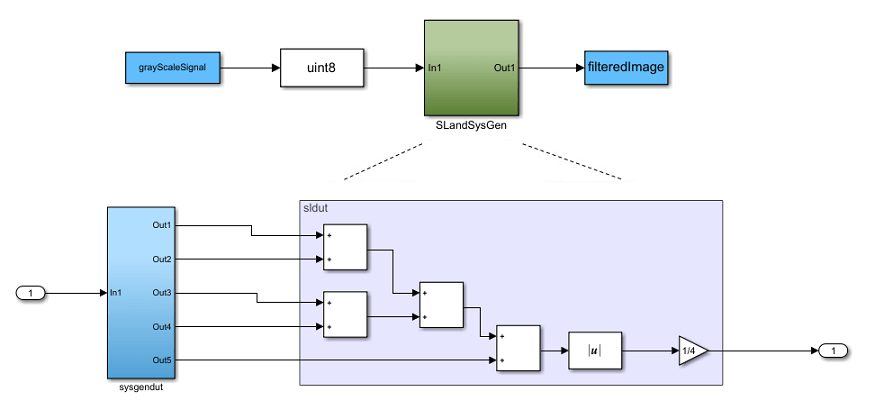

この例の設計 (コード生成サブシステム) には、Simulink ネイティブ ブロックで構成される部分と Xilinx ブロックで構成される部分の 2 つの部分があります。Xilinx ブロックはモデル hdlcoder_slsysgen の最上位の SLandSysGen Subsystem 内にある Xilinx System Generator Subsystem sysgendut にまとめられています。これらの Xilinx FPGA のブロックは、System Generator で最適化されます。設計の残りの部分については、Simulink ブロックと HDL Coder からモデルベース デザイン機能と HDL 最適化 (分散型パイプラインや遅延の均衡化など) が提供されます。

open_system('hdlcoder_slsysgen'); open_system('hdlcoder_slsysgen/SLandSysGen');

Simulink® コンポーネントに対するモデルレベルの最適化の実行

この例では、SLandSysGen Subsystem 内の sldut セクションで示される加算ツリーを Simulink ブロックでモデル化します。速度の最適化のために分散型パイプライン機能を使用できます。

分散型パイプラインでは、パイプライン レジスタを加算ツリーに移動することで、モデル関数を変更せずにクリティカル パスを減らすことができます。リソース共有などの他の最適化も使用できますが、この例では使用しません。

open_system('hdlcoder_slsysgen/SLandSysGen');

Xilinx System Generator Subsystem の作成

Xilinx System Generator Subsystem を作成するには次のようにします。

Xilinx ブロックを 1 つのサブシステムにまとめ、HDL アーキテクチャを既定値の

Moduleのままにします。サブシステムの最上位に System Generator のトークンを配置します。Xilinx System Generator Subsystem 内にサブシステムの階層構造を含めることができますが、階層構造の最上位に System Generator のトークンが存在しなければなりません。

open_system('hdlcoder_slsysgen/SLandSysGen/sysgendut');

Gateway In ブロックと Gateway Out ブロックの構成

それぞれの Xilinx System Generator Subsystem で、入力端子と出力端子を Gateway In ブロックと Gateway Out ブロックに直接接続しなければなりません。

Gateway In ブロックは非自明なデータ型変換をしてはなりません。たとえば、Gateway In ブロックは uint8 と UFix_8_0 との間で変換できますが、データの符号、語長または小数部の長さの変更は許可されていません。

HDL コードの生成

HDL コードは、コマンド ラインで makehdl を使用するか HDL ワークフロー アドバイザーを使用して生成できます。makehdl を使用する場合は次のようにします。

makehdl('hdlcoder_slsysgen/SLandSysGen');

他のモデルと同じように、テストベンチを生成して設計のシミュレーションや合成も可能です。