レート差の大きいマルチレート設計ための生成された HDL コードの最適化

問題点

Simulink® でマルチレート アルゴリズムから HDL コードを生成すると、HDL Coder™ で多数のパイプライン レジスタが生成されて、HDL 設計が FPGA に適合しなくなる可能性があります。この問題はモデル化パターンが原因で発生し、レート差が大きくなる可能性があります。モデル化技術を使用してサンプル時間の比率を管理することで、この問題を解決できます。

説明

この問題は、Simulink® モデルのサンプル レートの差が大きい場合、または異なるクロックレート パスが生じる次のような特定のブロック実装や最適化を使用すると発生します。

Multicycle ブロックの実装

入力および出力パイプライン

分散型パイプライン方式

浮動小数点ライブラリのマッピング

ネイティブ浮動小数点 HDL コード生成

reciprocal、sqrt、divide などの固定小数点算術関数

リソース共有

ストリーミング

余分なパイプラインによってレイテンシ オーバーヘッドが発生し、異なるレートで動作する複数の信号パス間を一致させるため遅延の挿入が必要になります。最も高速のクロック レートと最も低速のクロック レートの比率が非常に大きくなると、コード ジェネレーターは結果の HDL コードに多数のレジスタを導入する可能性があります。パイプライン レジスタの数が多くなると、生成される HDL ファイルのサイズも大きくなり、設計が FPGA に適合しなくなる可能性があります。

この問題が発生する例として、次の Simulink モデルを開きます。

open_system('hdlcoder_multirate_high_differential')

モデルをコンパイルして、hdlcoder_multirate_high_differential サブシステムをダブルクリックすると、モデルの高速クロック レート領域に浮動小数点 Gain ブロック、マルチサイクル演算子があることがわかります。

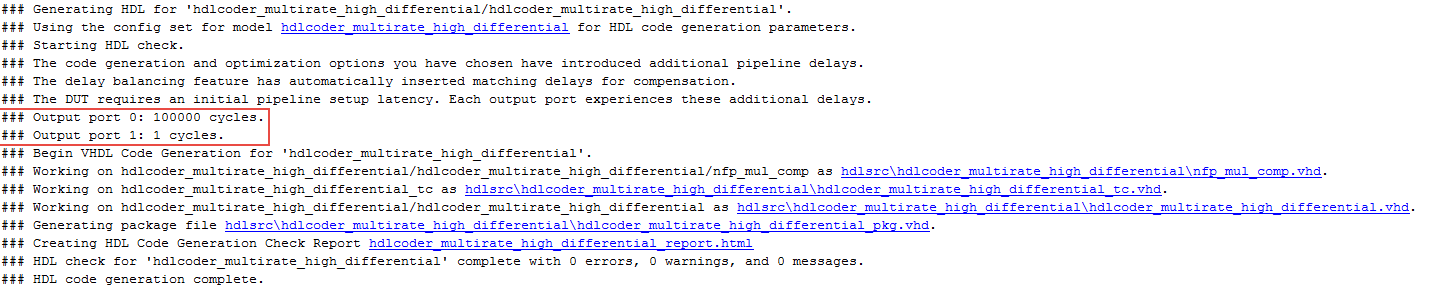

hdlcoder_multirate_high_differential サブシステムの HDL コードを生成し、出力ログをチェックします。

生成されたモデルを開きます。コマンド ラインで、「gm_hdlcoder_multirate_high_differential」と入力します。モデルをコンパイルし、hdlcoder_multirate_high_differential サブシステムをダブルクリックすると、モデルはサンプル時間の凡例に表示されているとおりに示されます。

設計の高速クロック レート領域の大きな出力レイテンシは、システムの複数の出力パス間での遅延を均衡化するためにコード ジェネレーターによって導入されます。この大きなレイテンシが原因で、生成された HDL ファイルのサイズが大きくなり、生成されたコードの効率が下がります。

推奨事項

推奨事項 1: シングルレート モデルを使用する

HDL コードをターゲットにしているほとんどのアプリケーションには、それほど大きなレート差は必要ありません。その場合は、シングルレート モデルを使用することをお勧めします。この例では、hdlcoder_multirate_high_differential サブシステム内の Constant ブロックのサンプル レートをベース モデルと同じサンプル レートに変更できます。

Constant ブロックのサンプル時間をモデルのベースのサンプル時間と同じ 10E-06 に変更した次のモデルを開きます。

open_system('hdlcoder_singlerate')

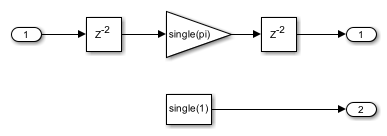

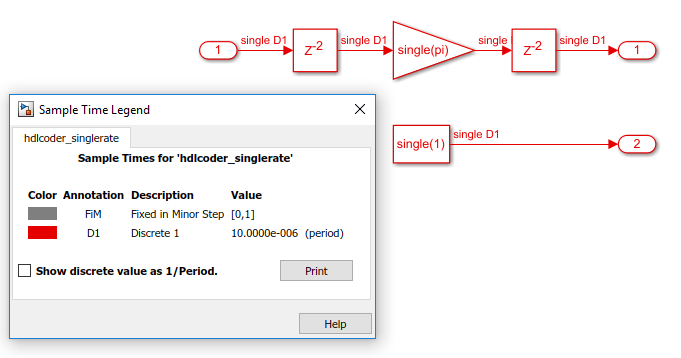

モデルをコンパイルして、hdlcoder_singlerate サブシステムをダブルクリックすると、モデル内の信号パスが同じサンプル時間 10E-06 で動作していることがわかります。

関数 hdlset_param を使用して、hdlcoder_singlerate モデルの UseFloatingPoint プロパティを on に設定します。hdlcoder_singlerate サブシステムの HDL コードを生成し、出力ログをチェックします。

出力レイテンシが大幅に減少していることが示されます。次に、生成されたモデルを開きます。MATLAB® コマンド ラインで、「gm_hdlcoder_singlerate」と入力します。モデルをコンパイルし、hdlcoder_singlerate サブシステムをダブルクリックすると、モデルはサンプル時間の凡例に表示されているとおりに示されます。

生成された HDL コードは最適になり、使用するレジスタの数が少なくなります。したがって、設計をターゲットの FPGA プラットフォームに展開できます。

推奨事項 2: レート差を小さくする

マルチレート モデルを使用する場合は、レート差を小さくすることをお勧めします。レート差は、設計で最も速いクロック レートと最も遅いクロック レートとの比率に対応します。ターゲット アプリケーションに、ナノ秒 (ns) の時間単位で実行される信号パスとマイクロ秒 (us) の時間単位で実行される信号パスの 2 つの信号パスが必要な場合は、モデル内にマルチレート パスを残す可能性があります。遅延の均衡化によって、信号パスのバランスを取るために大量のレジスタが導入される可能性があることに注意してください。

この例では、hdlcoder_multirate_high_differential Subsystem 内の Constant ブロックのサンプルレートを変更して、レート差を小さくします。

Constant ブロックのサンプル時間が 0.01 に変更された以下のモデルを開きます。

open_system ('hdlcoder_multirate_medium_differential')

モデルをコンパイルし、hdlcoder__multirate_medium_differential サブシステムをダブルクリックすると、2 つの信号パス間のレート差が 1000 であることが示されます。

hdlcoder_multirate_medium_differential サブシステムの HDL コードを生成し、出力ログをチェックします。

生成されたモデルを開きます。MATLAB® コマンド ラインで、「gm_hdlcoder_multirate_medium_differential」と入力します。生成されたモデルをコンパイルし、hdlcoder_multirate_medium_differential サブシステムをダブルクリックすると、モデルはサンプル時間の凡例に表示されているとおりに示されます。

モデルの高速クロック レート パスにはおよそ 1000 もの多数のレジスタがあります。システムのサンプルレートの 1000 倍の速さのサンプルレートで実行される制御ロジックがある場合、レジスタの追加コストが予想されます。生成されたコードをターゲット プラットフォームに展開する場合は、ターゲット プラットフォームのハードウェア リソースの制約に注意してください。この推奨事項では、最適な HDL コードの生成と、非常に大きいレート差を必要とする実際の FPGA アプリケーションのターゲット化の間にトレードオフがあります。

推奨事項 3: RAM へのパイプライン遅延のマッピング

ターゲットの FPGA デバイスの設計で使用する多数のレジスタを最適化するには、[RAM へのパイプライン遅延のマッピング] 設定を使用できます。この設定は、ターゲット FPGA デバイスの面積のフットプリントを削減するために RAM リソースを使用する HDL コードに挿入されるパイプライン レジスタのトレードオフです。この設定は、[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [最適化] 、 [一般] タブで有効にすることができます。

この設定は、コマンド ラインで MapPipelineDelaysToRAM プロパティを hdlset_param または makehdl と共に使用して指定することもできます。hdlget_param を使用してプロパティ値を表示できます。以下の方法のいずれかを使用します。

プロパティを引数として関数

makehdlに渡す。makehdl('hdlcoder_multirate_high_differential/hdlcoder_multirate_high_differential', ... 'MapPipelineDelaysToRAM','on')hdlset_paramを使用すると、モデルにパラメーターを設定してから、makehdlを使用して HDL コードを生成できる。hdlset_param('hdlcoder_multirate_high_differential', ... 'MapPipelineDelaysToRAM','on') makehdl('hdlcoder_multirate_high_differential/hdlcoder_multirate_high_differential')

この設定を前の推奨事項と組み合わせて使用することで、生成された HDL コードの効率が向上し、ターゲット プラットフォームにコードを展開できます。

参考

createFloatingPointTargetConfig