遅延の均衡化のスコープの制御

この例では、設計全体の遅延は均衡化せずに、設計の特定の部分の遅延を均衡化する方法を示します。

BalanceDelays HDL 入出力端子ブロック プロパティを使用して HDL Coder™ によって導入される追加の遅延を均衡化することで、遅延をプログラムによって均衡化できます。このプロパティは、モデル内の個々の入力端子と出力端子で有効または無効にできます。たとえば、データ パスとコントロール パスを含む設計で、遅延の均衡化を設計のデータ パスのみに適用できます。これは、データ同期を必要とするパスに焦点を当てることを意味します。テスト対象設計 (DUT) 端子レベルで BalanceDelays を使用して、HDL Coder が遅延を均衡化する方法と場所を制御できます。hdlcoder_localdelaybalancing.slx では、ユーザー定義の安定したコントロール パスに対する遅延の均衡化を無効にする方法を示します。

遅延の均衡化をデータ パスに制約

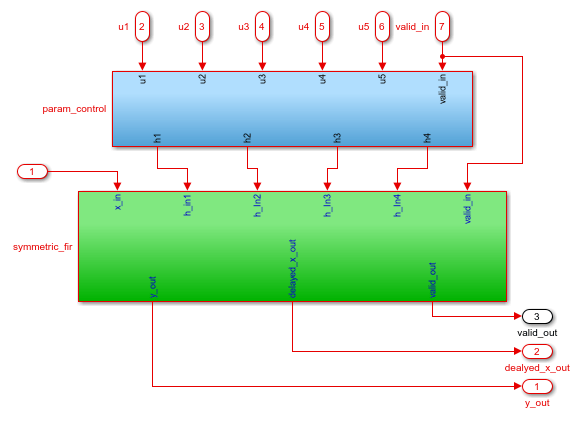

モデル例 hdlcoder_localdelaybalancing.slx には、テスト対象デバイス (DUT) サブシステム hdlcoder_localdelaybalancing/Subsystem の下に 2 つのサブシステム param_control と symmetric_fir があり、それぞれ制御ロジックとデータ パスが含まれます。

open_system('hdlcoder_localdelaybalancing'); open_system('hdlcoder_localdelaybalancing/Subsystem');

タイミングの結果を最適化するために、各サブシステムに 1 つの出力パイプライン レジスタをもつブロックが 1 つあります。

hdldispblkparams('hdlcoder_localdelaybalancing/Subsystem/param_control/And'); hdldispblkparams('hdlcoder_localdelaybalancing/Subsystem/symmetric_fir/Add');

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

HDL Block Parameters ('hdlcoder_localdelaybalancing/Subsystem/param_control/And')

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

Implementation

Architecture : default

Implementation Parameters

OutputPipeline : 1

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

HDL Block Parameters ('hdlcoder_localdelaybalancing/Subsystem/symmetric_fir/Add')

%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%

Implementation

Architecture : Linear

Implementation Parameters

OutputPipeline : 1

検証モデルの生成を有効にし、関数 makehdl を使用して HDL コードを生成します。

hdlset_param('hdlcoder_localdelaybalancing', 'GenerateValidationModel', 'on'); makehdl('hdlcoder_localdelaybalancing/Subsystem');

### Working on the model <a href="matlab:open_system('hdlcoder_localdelaybalancing')">hdlcoder_localdelaybalancing</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_localdelaybalancing/Subsystem')">hdlcoder_localdelaybalancing/Subsystem</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_localdelaybalancing', { 'HDL Code Generation' } )">hdlcoder_localdelaybalancing</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_localdelaybalancing'.

### Begin compilation of the model 'hdlcoder_localdelaybalancing'...

### Working on the model 'hdlcoder_localdelaybalancing'...

### The code generation and optimization options you have chosen have introduced additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for compensation.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Output port 3: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_localdelaybalancing', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_localdelaybalancing'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_localdelaybalancing/gm_hdlcoder_localdelaybalancing.slx')">hdlsrc/hdlcoder_localdelaybalancing/gm_hdlcoder_localdelaybalancing.slx</a>

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc/hdlcoder_localdelaybalancing/highlightDelayAbsorption')">hdlsrc/hdlcoder_localdelaybalancing/highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoder_localdelaybalancing/clearhighlighting.m')">hdlsrc/hdlcoder_localdelaybalancing/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoder_localdelaybalancing/gm_hdlcoder_localdelaybalancing_vnl')">gm_hdlcoder_localdelaybalancing_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_localdelaybalancing'.

### Working on hdlcoder_localdelaybalancing/Subsystem/param_control/params as hdlsrc/hdlcoder_localdelaybalancing/params.vhd.

### Working on hdlcoder_localdelaybalancing/Subsystem/param_control as hdlsrc/hdlcoder_localdelaybalancing/param_control.vhd.

### Working on hdlcoder_localdelaybalancing/Subsystem/symmetric_fir as hdlsrc/hdlcoder_localdelaybalancing/symmetric_fir.vhd.

### Working on hdlcoder_localdelaybalancing/Subsystem as hdlsrc/hdlcoder_localdelaybalancing/Subsystem.vhd.

### Code Generation for 'hdlcoder_localdelaybalancing' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex13756842/hdlsrc/hdlcoder_localdelaybalancing', '/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex13756842/hdlsrc/hdlcoder_localdelaybalancing/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex13756842/hdlsrc/hdlcoder_localdelaybalancing/Subsystem_report.html

### HDL check for 'hdlcoder_localdelaybalancing' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

検証モデルを読み込んで更新し、生成されたモデルのレイアウトを再配置して、param_control サブシステムに対する検証モデルを開きます。

load_system('gm_hdlcoder_localdelaybalancing_vnl'); set_param('gm_hdlcoder_localdelaybalancing_vnl', 'SimulationCommand', 'update'); arrangeLayout('gm_hdlcoder_localdelaybalancing_vnl/Subsystem/param_control') open_system('gm_hdlcoder_localdelaybalancing_vnl/Subsystem/param_control');

検証モデルに示すように、遅延の均衡化は既定でグローバルに有効になっており、コントロール パスとデータ パスの両方に一致する遅延を挿入します。検証モデルの詳細については、生成されたモデルと検証モデルを参照してください。

この例では、データの同期が必要なのは、データ パスである symmetric_fir だけです。param_control サブシステムへの入力 u1 から u4 は、FIR フィルターへの係数である定数入力です。これらの係数の DUT サブシステムを通る入力パスは安定しており、互いに同期したり、処理されたデータと同期したりする必要はありません。その結果、制御ロジックへの定数入力をもつ入力端子の遅延の均衡化を無効にして、ハードウェア リソースに保存することができます。これを達成するために、DUT サブシステムの Inport ブロック u1 から u4 までの HDL ブロック プロパティ BalanceDelays を off に設定します。安定したパスは DUT サブシステムの下位階層まで伝播するため、param_control または symmetric_fir サブシステム内の下位レベルの Inport ブロックに対してこのプロパティを無効にする必要はありません。

hdlset_param('hdlcoder_localdelaybalancing/Subsystem/u1', 'BalanceDelays', 'off'); hdlset_param('hdlcoder_localdelaybalancing/Subsystem/u2', 'BalanceDelays', 'off'); hdlset_param('hdlcoder_localdelaybalancing/Subsystem/u3', 'BalanceDelays', 'off'); hdlset_param('hdlcoder_localdelaybalancing/Subsystem/u4', 'BalanceDelays', 'off');

検証モデルを閉じ、関数 makehdl を使用して HDL コードを生成し、param_control サブシステムに対する新しい検証モデルを開きます。

bdclose('gm_hdlcoder_localdelaybalancing_vnl'); hdlset_param('hdlcoder_localdelaybalancing', 'ValidationModelNameSuffix', '_vnl_DBoff') makehdl('hdlcoder_localdelaybalancing/Subsystem'); load_system('gm_hdlcoder_localdelaybalancing_vnl_DBoff'); set_param('gm_hdlcoder_localdelaybalancing_vnl_DBoff', 'SimulationCommand', 'update'); Simulink.BlockDiagram.expandSubsystem('gm_hdlcoder_localdelaybalancing_vnl_DBoff/Subsystem/param_control/params'); open_system('gm_hdlcoder_localdelaybalancing_vnl_DBoff/Subsystem/param_control');

### Working on the model <a href="matlab:open_system('hdlcoder_localdelaybalancing')">hdlcoder_localdelaybalancing</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_localdelaybalancing/Subsystem')">hdlcoder_localdelaybalancing/Subsystem</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_localdelaybalancing', { 'HDL Code Generation' } )">hdlcoder_localdelaybalancing</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_localdelaybalancing'.

### Begin compilation of the model 'hdlcoder_localdelaybalancing'...

### Working on the model 'hdlcoder_localdelaybalancing'...

### The code generation and optimization options you have chosen have introduced additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for compensation.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Output port 2: 1 cycles.

### Output port 3: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_localdelaybalancing', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_localdelaybalancing'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_localdelaybalancing/gm_hdlcoder_localdelaybalancing.slx')">hdlsrc/hdlcoder_localdelaybalancing/gm_hdlcoder_localdelaybalancing.slx</a>

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc/hdlcoder_localdelaybalancing/highlightDelayAbsorption')">hdlsrc/hdlcoder_localdelaybalancing/highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoder_localdelaybalancing/clearhighlighting.m')">hdlsrc/hdlcoder_localdelaybalancing/clearhighlighting.m</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoder_localdelaybalancing/gm_hdlcoder_localdelaybalancing_vnl_DBoff')">gm_hdlcoder_localdelaybalancing_vnl_DBoff</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_localdelaybalancing'.

### Working on hdlcoder_localdelaybalancing/Subsystem/param_control/params as hdlsrc/hdlcoder_localdelaybalancing/params.vhd.

### Working on hdlcoder_localdelaybalancing/Subsystem/param_control as hdlsrc/hdlcoder_localdelaybalancing/param_control.vhd.

### Working on hdlcoder_localdelaybalancing/Subsystem/symmetric_fir as hdlsrc/hdlcoder_localdelaybalancing/symmetric_fir.vhd.

### Working on hdlcoder_localdelaybalancing/Subsystem as hdlsrc/hdlcoder_localdelaybalancing/Subsystem.vhd.

### Code Generation for 'hdlcoder_localdelaybalancing' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex13756842/hdlsrc/hdlcoder_localdelaybalancing', '/tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex13756842/hdlsrc/hdlcoder_localdelaybalancing/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3695514/tpd4e99feb/hdlcoder-ex13756842/hdlsrc/hdlcoder_localdelaybalancing/Subsystem_report.html

### HDL check for 'hdlcoder_localdelaybalancing' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

これで、遅延の均衡化がデータ パスのサブシステムでのみアクティブになり、生成されたモデルとコードのコントロール パスのサブシステムには遅延が含まれなくなります。