レイテンシを加味したモデル化における遅延吸収の使用

HDL コードの生成時に遅延の均衡化で実行される遅延吸収による最適化を適用するためのレイテンシを加味した設計のモデル化方法を学習します。

遅延吸収は、遅延の均衡化による最適化の一部です。遅延吸収では、最適化によって生じるパイプライン遅延の代わりに設計上の遅延を使用することで、使用されないレイテンシが設計に追加されることを防ぎます。遅延吸収を使用するには、レイテンシを加味したモデル化を行います。つまり、モデルに設計上の遅延を追加して、最適化によって導入されるレイテンシと置き換えます。レイテンシを加味して設計をモデル化することにより、HDL Coder™ で遅延吸収を使用して設計上の遅延を吸収できるようになり、モデルにレイテンシを追加する余分なパイプライン遅延が導入されなくなります。これにより、元のモデルと生成されたモデルの間でタイミングの差が生じなくなり、生成される HDL コードと機能的に等価なモデルが HDL Coder で生成されます。

設計に含まれる遅延には、設計上の遅延とパイプライン遅延があります。設計上の遅延は、Delay ブロックや状態をもつ他のブロック (Queue、HDL FIFO、Buffer ブロックなど) を使用して手動で設計に挿入する遅延です。パイプライン遅延は、最適化設定 (入出力パイプライン オプションなど) またはブロック実装設定 (Divide ブロックの ShiftAdd 実装や Trigonometric Function ブロックの CORDIC 近似など) によって生成される遅延です。

特定のブロック実装、浮動小数点演算、および入力パイプラインやリソース共有などの最適化設定により、生成された HDL コードや生成されたモデルでレイテンシが発生することがあります。追加のレイテンシにより、結果的に元のモデルと生成されたモデルの間にタイミングの差が生じます。フィードバック ループで制御システムを使用するときなど、このタイミングの差を回避するために、モデルに設計上の遅延を追加できます。遅延吸収で設計上の遅延を吸収するには次のようにします。

レイテンシを発生させるブロックの後に Delay ブロックを配置します。Delay ブロックは、レイテンシを発生させるブロックの下流であれば、データ パスの任意の位置に配置できます。

Delay ブロックの [遅延の長さ] パラメーターをブロックのレイテンシと等しい値に設定します。

Delay ブロックを元のモデルに追加すると、元のモデルをレイテンシを加味してシミュレートできます。

レイテンシを発生させる可能性があるブロックには以下があります。

カスタム レイテンシ値がゼロより大きい Divide、Sqrt、および Reciprocal ブロック

[関数] が

sin、cos、sincos、cos+jsin、またはatan2に設定され、[近似法] がCORDICに設定された Trigonometric Function ブロックHDL ブロック プロパティ "LatencyStrategy" が

Max、Min、またはゼロより大きいカスタム値に設定されたネイティブ浮動小数点演算子

固定小数点型のカスタム レイテンシをもつブロックを調べるには、HDLMathLib ライブラリを開きます。このライブラリに、制御信号をもつ固定小数点ブロックが含まれています。

open_system('HDLMathLib')

ブロックによってレイテンシが導入される場合のレイテンシを加味したモデル化

HDL Coder によって遅延がどのように吸収されるかを調べるには、モデル hdlcoder_absorb_delays を開きます。

open_system('hdlcoder_absorb_delays') set_param('hdlcoder_absorb_delays', 'SimulationCommand', 'Update')

HDL_DUT サブシステムの内部を見ると、Divide ブロックの横に [遅延の長さ] が 12 と等しい Delay ブロックがあります。この [遅延の長さ] は、固定小数点データ型の除算演算のレイテンシに対応しています。この場合に必要な [遅延の長さ] はビット幅 8 と 4 の和であり、つまり 12 と等しくなります。

load_system('hdlcoder_absorb_delays') open_system('hdlcoder_absorb_delays/HDL_DUT')

DUT サブシステムの HDL コードを生成するには、makehdl 関数を使用します。

makehdl('hdlcoder_absorb_delays/HDL_DUT')

### Working on the model <a href="matlab:open_system('hdlcoder_absorb_delays')">hdlcoder_absorb_delays</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_absorb_delays/HDL_DUT')">hdlcoder_absorb_delays/HDL_DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_absorb_delays', { 'HDL Code Generation' } )">hdlcoder_absorb_delays</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_absorb_delays'.

### Begin compilation of the model 'hdlcoder_absorb_delays'...

### Begin compilation of the model 'hdlcoder_absorb_delays'...

### Working on the model 'hdlcoder_absorb_delays'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_absorb_delays', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_absorb_delays'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_absorb_delays/gm_hdlcoder_absorb_delays.slx')">hdlsrc/hdlcoder_absorb_delays/gm_hdlcoder_absorb_delays.slx</a>

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc/hdlcoder_absorb_delays/highlightDelayAbsorption')">hdlsrc/hdlcoder_absorb_delays/highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc/hdlcoder_absorb_delays/clearhighlighting.m')">hdlsrc/hdlcoder_absorb_delays/clearhighlighting.m</a>

### Begin VHDL Code Generation for 'hdlcoder_absorb_delays'.

### Working on hdlcoder_absorb_delays/HDL_DUT/Divide as hdlsrc/hdlcoder_absorb_delays/Divide.vhd.

### Working on hdlcoder_absorb_delays/HDL_DUT as hdlsrc/hdlcoder_absorb_delays/HDL_DUT.vhd.

### Generating package file hdlsrc/hdlcoder_absorb_delays/HDL_DUT_pkg.vhd.

### Code Generation for 'hdlcoder_absorb_delays' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delays', '/tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delays/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delays/HDL_DUT_report.html

### HDL check for 'hdlcoder_absorb_delays' complete with 0 errors, 0 warnings, and 2 messages.

### HDL code generation complete.

生成されたモデルでは、Divide ブロックの横の遅延がブロックのレイテンシに吸収されています。この Divide ブロックをダブルクリックすると、元の Divide ブロックと [遅延の長さ] が 12 の Delay ブロックが表示されます。

load_system('hdlsrc/hdlcoder_absorb_delays/gm_hdlcoder_absorb_delays.slx') open_system('gm_hdlcoder_absorb_delays/HDL_DUT/Divide')

浮動小数点演算の遅延吸収を示す例については、ネイティブ浮動小数点のレイテンシに関する考慮事項を参照してください。

最適化によってレイテンシが導入される場合のレイテンシを加味したモデル化

ストリーミングなどの最適化によってレイテンシが導入されることがあります。たとえば、モデル hdlcoder_absorb_delay_streaming を開きます。この DUT には、元の設計をレイテンシを加味してモデル化するための Delay ブロックと、Product ブロックを含むサブシステムが含まれています。入力はサイズ 10 のベクトルです。

load_system('hdlcoder_absorb_delay_streaming'); open_system('hdlcoder_absorb_delay_streaming/DUT'); set_param('hdlcoder_absorb_delay_streaming','SimulationCommand','Update');

ベクトル計算をストリーミングするには、下位レベルのサブシステムで HDL ブロック プロパティ StreamingFactor を 10 に設定します。レイテンシを加味したモデル化を行うには、モデル プロパティ AllowDelayDistribution (既定で有効) を使用して、モデル内の Delay ブロックを遅延吸収で吸収できるようにします。その後、makehdl 関数を使用して DUT サブシステムの HDL コードを生成します。

hdlset_param('hdlcoder_absorb_delay_streaming/DUT/Subsystem', 'StreamingFactor', 10); hdlget_param('hdlcoder_absorb_delay_streaming', 'AllowDelayDistribution')

ans =

'on'

makehdl('hdlcoder_absorb_delay_streaming/DUT');

### Working on the model <a href="matlab:open_system('hdlcoder_absorb_delay_streaming')">hdlcoder_absorb_delay_streaming</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_absorb_delay_streaming/DUT')">hdlcoder_absorb_delay_streaming/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_absorb_delay_streaming', { 'HDL Code Generation' } )">hdlcoder_absorb_delay_streaming</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_absorb_delay_streaming'.

### Begin compilation of the model 'hdlcoder_absorb_delay_streaming'...

### Working on the model 'hdlcoder_absorb_delay_streaming'...

### Working on... <a href="matlab:configset.internal.open('hdlcoder_absorb_delay_streaming', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_absorb_delay_streaming'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_absorb_delay_streaming/gm_hdlcoder_absorb_delay_streaming.slx')">hdlsrc/hdlcoder_absorb_delay_streaming/gm_hdlcoder_absorb_delay_streaming.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoder_absorb_delay_streaming/gm_hdlcoder_absorb_delay_streaming_vnl')">gm_hdlcoder_absorb_delay_streaming_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_absorb_delay_streaming'.

### MESSAGE: The design requires 10 times faster clock with respect to the base rate = 0.1.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdlsrc/hdlcoder_absorb_delay_streaming/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on hdlcoder_absorb_delay_streaming/DUT/Subsystem as hdlsrc/hdlcoder_absorb_delay_streaming/Subsystem.vhd.

### Working on hdlcoder_absorb_delay_streaming/DUT as hdlsrc/hdlcoder_absorb_delay_streaming/DUT.vhd.

### Generating package file hdlsrc/hdlcoder_absorb_delay_streaming/DUT_pkg.vhd.

### Code Generation for 'hdlcoder_absorb_delay_streaming' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delay_streaming', '/tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delay_streaming/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delay_streaming/DUT_report.html

### HDL check for 'hdlcoder_absorb_delay_streaming' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

ストリーミングが有効になっている場合、生成される設計に 1 サイクルの遅延をもつ Deserializer ブロックが挿入されます。元のモデルに Delay ブロックが含まれていなければ、生成される設計に元の設計と比べて 1 サイクルの余分なレイテンシが含まれることになります。遅延吸収による最適化では、生成される設計に追加のレイテンシが含まれないように、ストリーミングによって生じる遅延を元のモデルの Delay ブロックを使用してオフセットします。生成されたモデルを開いて、コード生成後に吸収された元の Delay ブロックを確認します。

open_system('gm_hdlcoder_absorb_delay_streaming/DUT'); set_param('gm_hdlcoder_absorb_delay_streaming','SimulationCommand','Update');

元のモデルの Delay ブロックを使用しないように遅延吸収を無効にするには、モデル プロパティ AllowDelayDistribution を off に設定します。この場合、遅延吸収を無効にしたため、生成されるモデルに 1 サイクルの余分なレイテンシがあることに注意してください。

hdlset_param('hdlcoder_absorb_delay_streaming', 'AllowDelayDistribution', 'off'); makehdl('hdlcoder_absorb_delay_streaming/DUT');

### Working on the model <a href="matlab:open_system('hdlcoder_absorb_delay_streaming')">hdlcoder_absorb_delay_streaming</a>

### Generating HDL for <a href="matlab:open_system('hdlcoder_absorb_delay_streaming/DUT')">hdlcoder_absorb_delay_streaming/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoder_absorb_delay_streaming', { 'HDL Code Generation' } )">hdlcoder_absorb_delay_streaming</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoder_absorb_delay_streaming'.

### Begin compilation of the model 'hdlcoder_absorb_delay_streaming'...

### Working on the model 'hdlcoder_absorb_delay_streaming'...

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 1 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoder_absorb_delay_streaming', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoder_absorb_delay_streaming'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/hdlcoder_absorb_delay_streaming/gm_hdlcoder_absorb_delay_streaming.slx')">hdlsrc/hdlcoder_absorb_delay_streaming/gm_hdlcoder_absorb_delay_streaming.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/hdlcoder_absorb_delay_streaming/gm_hdlcoder_absorb_delay_streaming_vnl')">gm_hdlcoder_absorb_delay_streaming_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_absorb_delay_streaming'.

### MESSAGE: The design requires 10 times faster clock with respect to the base rate = 0.1.

### Begin VHDL Code Generation for 'DUT_tc'.

### Working on DUT_tc as hdlsrc/hdlcoder_absorb_delay_streaming/DUT_tc.vhd.

### Code Generation for 'DUT_tc' completed.

### Working on hdlcoder_absorb_delay_streaming/DUT/Subsystem as hdlsrc/hdlcoder_absorb_delay_streaming/Subsystem.vhd.

### Working on hdlcoder_absorb_delay_streaming/DUT as hdlsrc/hdlcoder_absorb_delay_streaming/DUT.vhd.

### Generating package file hdlsrc/hdlcoder_absorb_delay_streaming/DUT_pkg.vhd.

### Code Generation for 'hdlcoder_absorb_delay_streaming' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delay_streaming', '/tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delay_streaming/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/hdlcoder_absorb_delay_streaming/DUT_report.html

### HDL check for 'hdlcoder_absorb_delay_streaming' complete with 0 errors, 0 warnings, and 1 messages.

### HDL code generation complete.

open_system('gm_hdlcoder_absorb_delay_streaming/DUT');

ブロックの HDL ブロック プロパティ AllowDelayDistribution を無効にすることで、特定の Delay ブロックに対する遅延吸収を無効にすることもできます。詳細については、AllowDelayDistributionを参照してください。

フィードバック ループでのレイテンシを加味したモデル化

フィードバック ループでレイテンシを加味したモデル化を行うときは、次のいずれかが可能です。

クロックレート パイプラインを使用する。詳細については、クロックレート パイプラインを参照してください。

遅延吸収を使用する。たとえば、クロック レートで設計上の遅延として表現されるレイテンシをある程度加味してフィードバック ループをモデル化することで、ネイティブ浮動小数点演算子やパイプライン最適化によって生じる遅延を吸収できます。

この例では、フィードバック ループで遅延吸収を使用してレイテンシを加味したモデル化を行います。

この例には出力パイプラインが含まれています。これは設計の速度の最適化に役立ちますが、それぞれのパイプライン用に余分なレイテンシのサイクルが導入されることになります。この追加のレイテンシは、アルゴリズムの数値と機能が維持されるように遅延の均衡化において均衡化されます。ただし、フィードバック ループでの遅延の均衡化には、レイテンシを加味したモデル化が必要になります。設計上の遅延を吸収することで、パイプライン最適化の結果として生じるタイミングの不一致を防ぐためです。

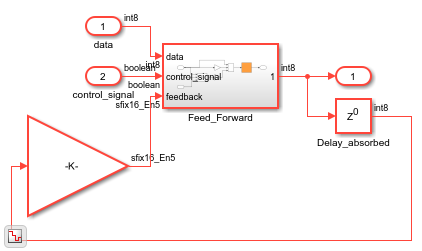

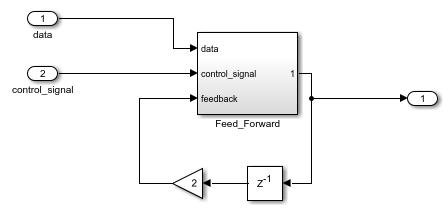

たとえば、フィードバック ループに出力パイプラインが追加されている場合に、レイテンシを加味したモデル化を行わずにコードを生成すると、HDL Coder で遅延の均衡化のエラーが発生します。これは delay_absorption_feedback_loop モデルで確認できます。このモデルでは、サブシステム delay_absorption_feedback_loop/DUT/Subsystem がフィードバック ループ内にあり、delay_absorption_feedback_loop/DUT/Feed_Forward/Sum ブロックの HDL ブロック プロパティ OutputPipeline が 2 に設定されています。

モデルを読み込んで、その DUT サブシステムを開きます。

load_system('delay_absorption_feedback_loop'); open_system('delay_absorption_feedback_loop/DUT');

hdlsaveparams を使用して既定以外のパラメーターを表示し、Sum ブロックの OutputPipeline の設定を確認します。

hdlsaveparams('delay_absorption_feedback_loop');

%% Set Model 'delay_absorption_feedback_loop' HDL parameters

hdlset_param('delay_absorption_feedback_loop', 'GenerateValidationModel', 'on');

hdlset_param('delay_absorption_feedback_loop', 'HDLSubsystem', 'delay_absorption_feedback_loop/DUT');

% Set Sum HDL parameters

hdlset_param('delay_absorption_feedback_loop/DUT/Feed_Forward/Sum', 'OutputPipeline', 2);

makehdl 関数を使用してコードを生成しようとすると、HDL コード生成レポートで遅延の均衡化のエラーが報告されます。このエラーを修正するには、出力パイプラインの最適化によって追加されるレイテンシと一致するように、十分な量のレイテンシを設計に追加する必要があります。

この例では、合計 2 つの単位遅延が必要であり、つまり [遅延の長さ] が 2 の設計上の遅延が 1 つ必要になります。フィードバック パスにある現在の Delay ブロックは吸収されており、2 サイクルの余分なレイテンシのうちの一方は処理されているため、エラーでは余分なレイテンシが 1 サイクルだけ報告されています。[遅延の長さ] が 1 になっているフィードバック遅延ブロックの [遅延の長さ] を 2 に増やします。これを行うには、Delay ブロックでパラメーターを設定するか、次のコマンドを使用します。

set_param('delay_absorption_feedback_loop/DUT/Delay', 'DelayLength', '2');

makehdl 関数を使用して HDL コードを生成します。

makehdl('delay_absorption_feedback_loop/DUT');

### Working on the model <a href="matlab:open_system('delay_absorption_feedback_loop')">delay_absorption_feedback_loop</a>

### Generating HDL for <a href="matlab:open_system('delay_absorption_feedback_loop/DUT')">delay_absorption_feedback_loop/DUT</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('delay_absorption_feedback_loop', { 'HDL Code Generation' } )">delay_absorption_feedback_loop</a> for HDL code generation parameters.

### Running HDL checks on the model 'delay_absorption_feedback_loop'.

### Begin compilation of the model 'delay_absorption_feedback_loop'...

### Working on the model 'delay_absorption_feedback_loop'...

### The code generation and optimization options you have chosen have introduced additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for compensation.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 2 cycles.

### Working on... <a href="matlab:configset.internal.open('delay_absorption_feedback_loop', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_delay_absorption_feedback_loop'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc/delay_absorption_feedback_loop/gm_delay_absorption_feedback_loop.slx')">hdlsrc/delay_absorption_feedback_loop/gm_delay_absorption_feedback_loop.slx</a>

### Generating new validation model: '<a href="matlab:open_system('hdlsrc/delay_absorption_feedback_loop/gm_delay_absorption_feedback_loop_vnl')">gm_delay_absorption_feedback_loop_vnl</a>'.

### Validation model generation complete.

### Begin VHDL Code Generation for 'delay_absorption_feedback_loop'.

### Working on delay_absorption_feedback_loop/DUT/Feed_Forward as hdlsrc/delay_absorption_feedback_loop/Feed_Forward.vhd.

### Working on delay_absorption_feedback_loop/DUT as hdlsrc/delay_absorption_feedback_loop/DUT.vhd.

### Generating package file hdlsrc/delay_absorption_feedback_loop/DUT_pkg.vhd.

### Code Generation for 'delay_absorption_feedback_loop' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openReportV2Dialog('/tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/delay_absorption_feedback_loop', '/tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/delay_absorption_feedback_loop/html/index.html')">index.html</a>

### Creating HDL Code Generation Check Report file:///tmp/Bdoc26a_3146167_3686806/tpe15ad821/hdlcoder-ex00529152/hdlsrc/delay_absorption_feedback_loop/DUT_report.html

### HDL check for 'delay_absorption_feedback_loop' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.

生成されたモデルを開き、吸収された設計上の遅延を確認します。出力パイプラインによって追加されるレイテンシに対応するために、フィードバック遅延が吸収されて Feed_Forward サブシステムに移動しています。遅延吸収の結果として余分なレイテンシが導入されることはありません。

open_system('gm_delay_absorption_feedback_loop/DUT'); set_param('gm_delay_absorption_feedback_loop', 'SimulationCommand', 'update');