このページは前リリースの情報です。該当の英語のページはこのリリースで削除されています。

ハードウェア ソフトウェア協調設計の基礎

ハードウェア ソフトウェア協調設計ワークフローについて、およびワークフロー アドバイザーを使用して SoC プラットフォームでアルゴリズムを実行する方法について説明する

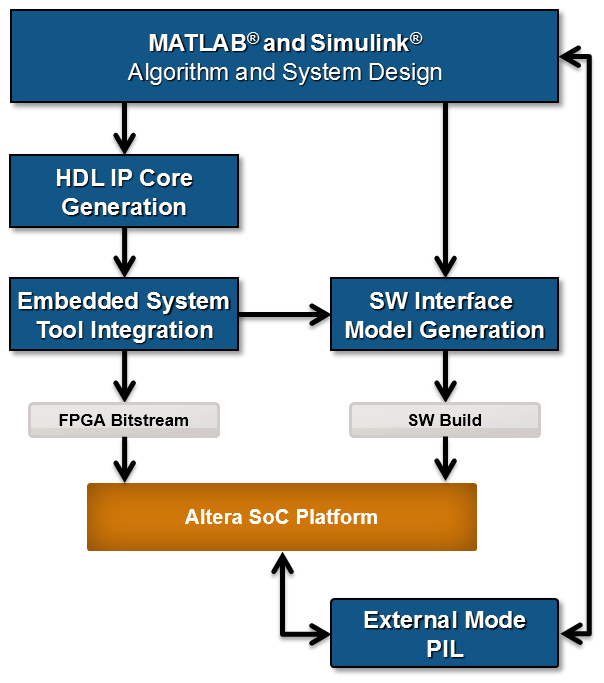

ハードウェア ソフトウェア協調設計ワークフローを使用して、設計を分割して SoC プラットフォームで実行できます。HDL ワークフロー アドバイザーでは、IP Core Generation ワークフローを使用して、SoC 搭載の FPGA で実行される HDL IP コアを生成できます。Embedded Coder® を使用すると、組み込みソフトウェアを生成してビルドし、ARM® プロセッサで実行できます。

トピック

- SoC プラットフォーム向けのハードウェア ソフトウェア協調設計ワークフロー

SoC プラットフォームをターゲットにする場合のワークフロー ステップの概要。

- HDL ワークフロー アドバイザーのご利用の前に

HDL ワークフロー アドバイザーの基礎とさまざまなタスクの実行方法について学習します。

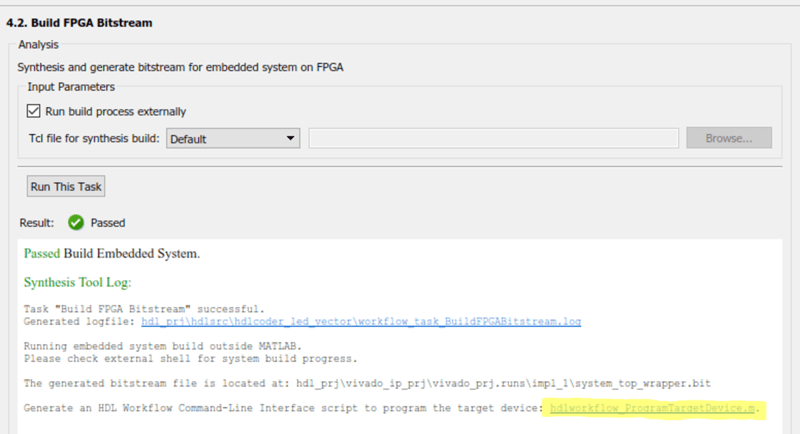

- スクリプトを使用した HDL ワークフローの実行

HDL ワークフロー CLI コマンド スクリプトをエクスポート、インポートまたは構成する

- AXI4 スレーブ インターフェイスの生成のための設計のモデル化

スカラー端子、ベクトル端子、バス データ型の AXI4 または AXI4-Lite インターフェイス用のモデルの設計および値の読み戻し方法。

- AXI4-Stream インターフェイス生成向けのモデル設計

AXI4-Stream ベクトルまたはスカラー インターフェイス生成向けのモデルの設計法

- AXI4 Master インターフェイスを生成するためのモデル設計

AXI4 Master プロトコルの説明および AXI4-Master インターフェイスを備えた IP コアの生成用にモデルを設計する方法の説明。