このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

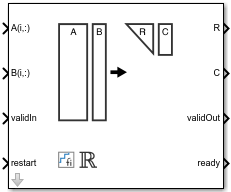

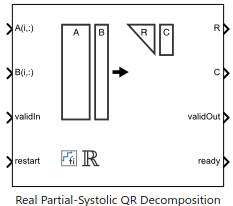

Real Partial-Systolic QR Decomposition

実数値の行列の QR 分解

ライブラリ:

Fixed-Point Designer HDL Support /

Matrices and Linear Algebra /

Matrix Factorizations

説明

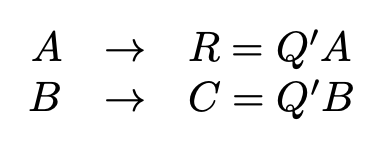

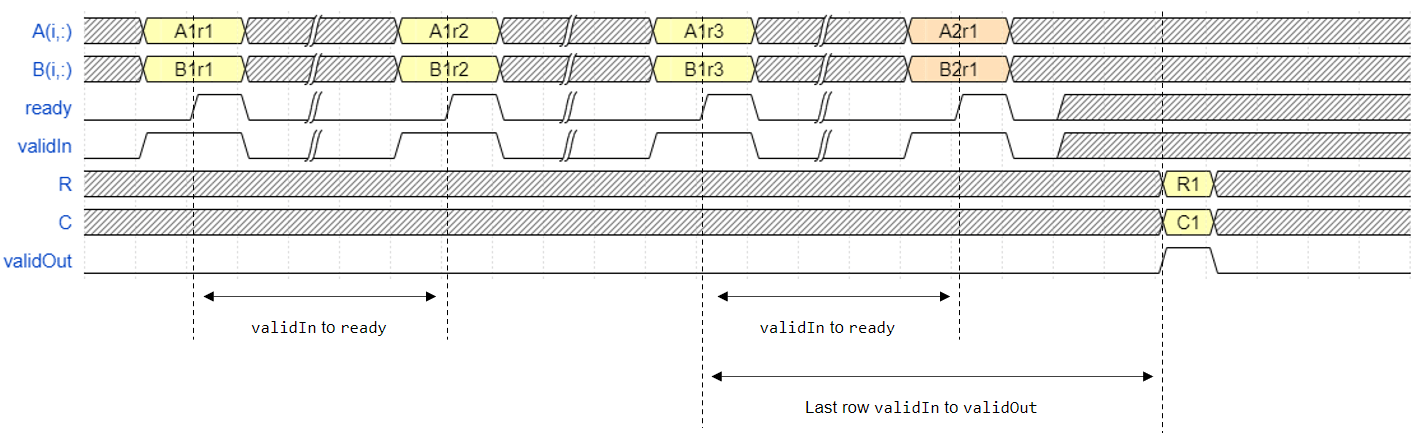

Real Partial-Systolic QR Decomposition ブロックは QR 分解を使用して R と C = Q'B を計算します。ここで QR = A、A および B は実数値の行列です。Ax = B の最小二乗解は、x = R\C です。R は上三角行列、Q は直交行列です。C = Q' を計算するには、B を単位行列に設定します。

正則化パラメーターが非ゼロの場合、Real Partial-Systolic QR Decomposition ブロックは をインプレースで に変換し、 をインプレースで に変換します。ここで、λ は正則化パラメーター、QR は のサイズを抑えた QR 分解、A は m 行 n 列の行列、p は B の列数、In = eye(n)、0n,p = zeros(n,p) です。

例

端子

入力

出力

パラメーター

アルゴリズム

参照

[1] "AMBA AXI and ACE Protocol Specification Version E." https://developer.arm.com/documentation/ihi0022/e/AMBA-AXI3-and-AXI4-Protocol-Specification/Single-Interface-Requirements/Basic-read-and-write-transactions/Handshake-process