このページは前リリースの情報です。該当の英語のページはこのリリースで削除されています。

Infineon AURIX を使用したマルチコア シミュレーションと最適化されたコード生成

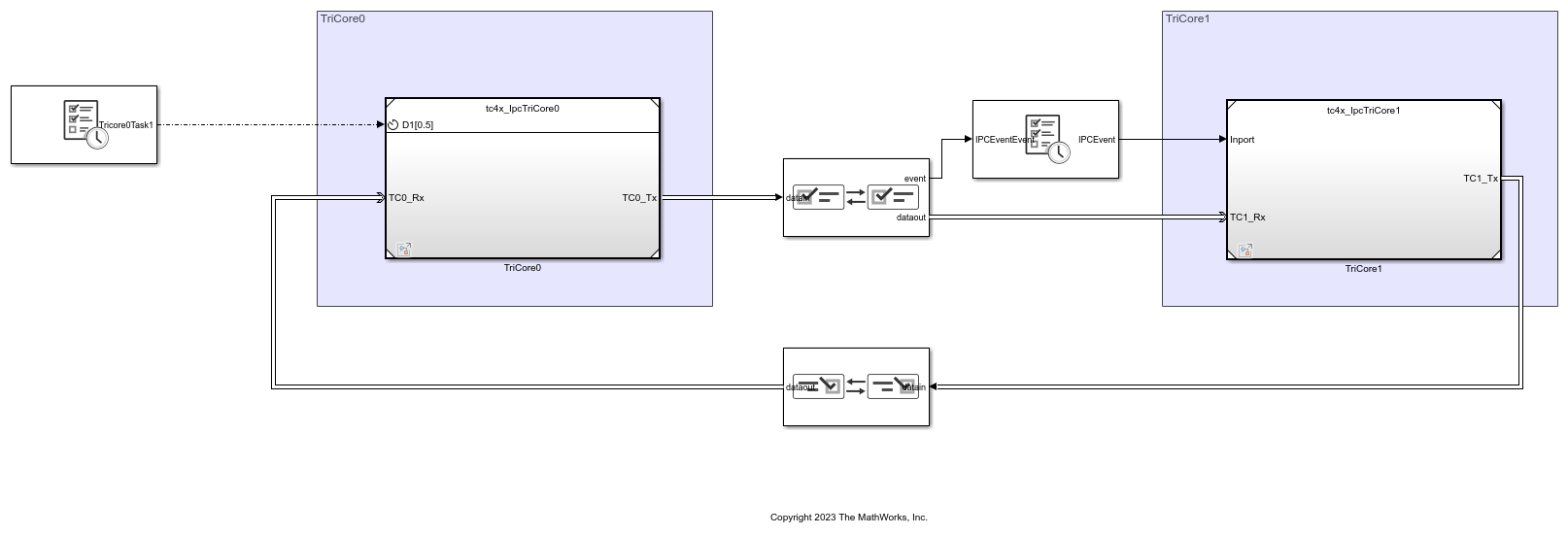

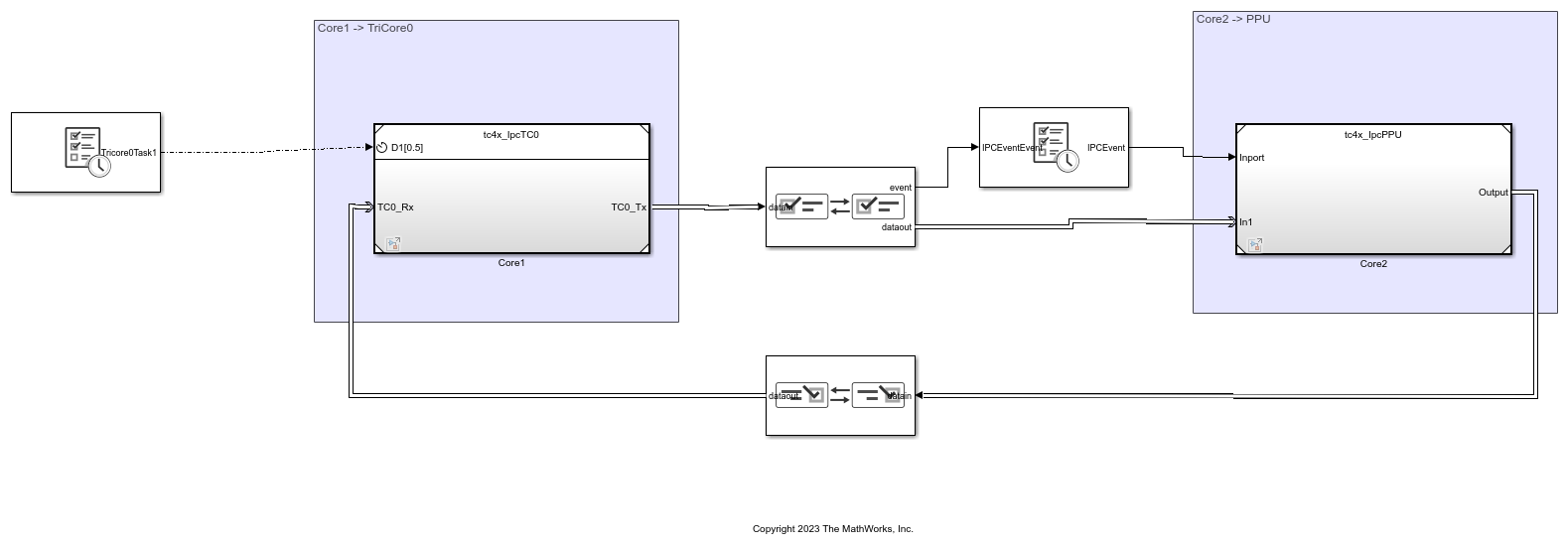

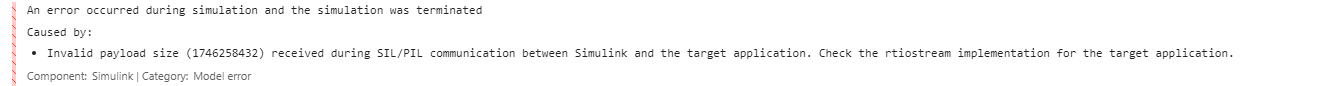

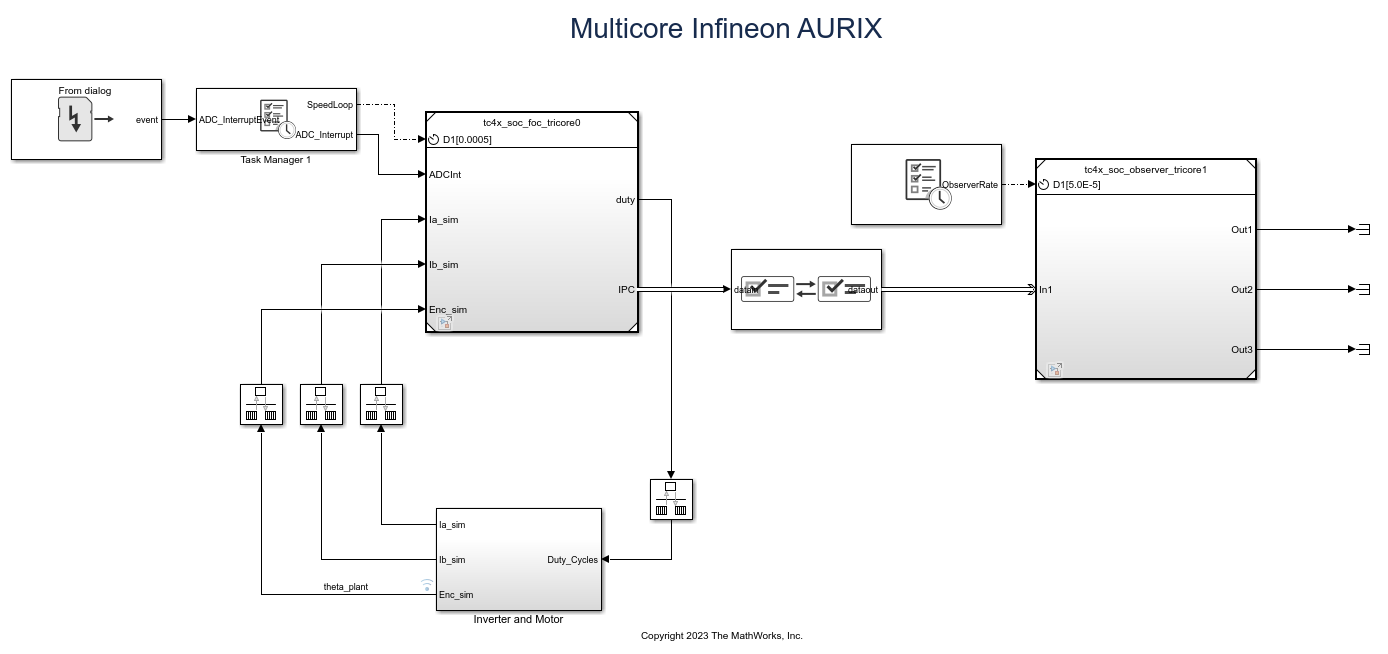

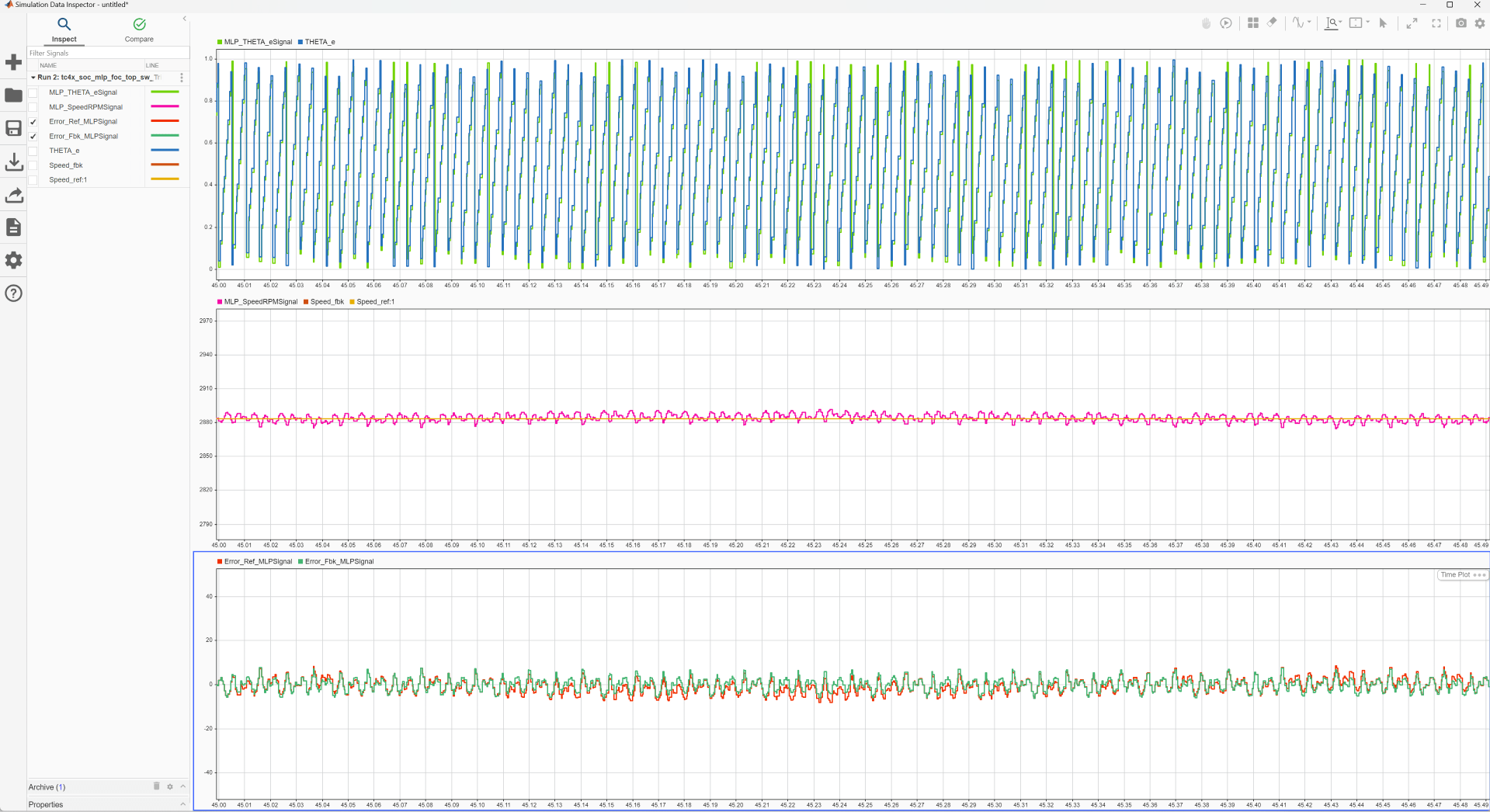

Infineon AURIX TC4x マイクロコントローラーには、6 つの同種の TriCore® CPU (TriCore 0 ~ TriCore 5) と 1 つの異種の並列処理ユニット (PPU) が含まれています。使用可能なコアで異なるモデルを実行したり、複雑なモデルを分割してこれらの複数のコアで同時に実行して、設計のモジュール性を実現したりできます。Interprocess Data Channel ブロックは、複数のコア間の通信を処理します。マルチコア モデルをシミュレーションした後、SoC Builder ツールを使用して生成されたコードを Infineon AURIX TC4x ハードウェア ボードに展開し、Infineon の One Eye ツールを使用してハードウェアからの信号を監視できます。

PPU は TriCore よりも高速に計算を実行します。PPU コアは、コード置換ライブラリを使用して生成されたコードの一部をハードウェア固有のコードに置き換えることにより、モデルのパフォーマンスを高速化します。TriCore 0 コアは主要コアであり、残りのすべての補助コア (TriCore 1 ~ TriCore 5 および PPU) と通信できます。

Infineon AURIX マイクロコントローラーの複数のコアを使用して SoC モデルを作成した後、SoC Builder ツールを使用して実行可能ファイル、コードを生成し、ハードウェア ボードをプログラムします。マルチコア モデルを検証、ビルド、実行して、実行可能ファイルを生成し、コード化し、Infineon AURIX TC4x ハードウェア ボードをプログラムする方法を理解するには、Getting Started with Multicore Modeling and Targeting for Infineon AURIX TC4x Microcontrollersの例を参照してください。

ブロック

ツール

| SoC Builder | Build, load, and execute multicore application models on Infineon AURIX TC4x hardware boards (R2024b 以降) |

| ハードウェア マッピング | Map tasks and peripherals in a model to hardware board configurations (R2022b 以降) |

トピック

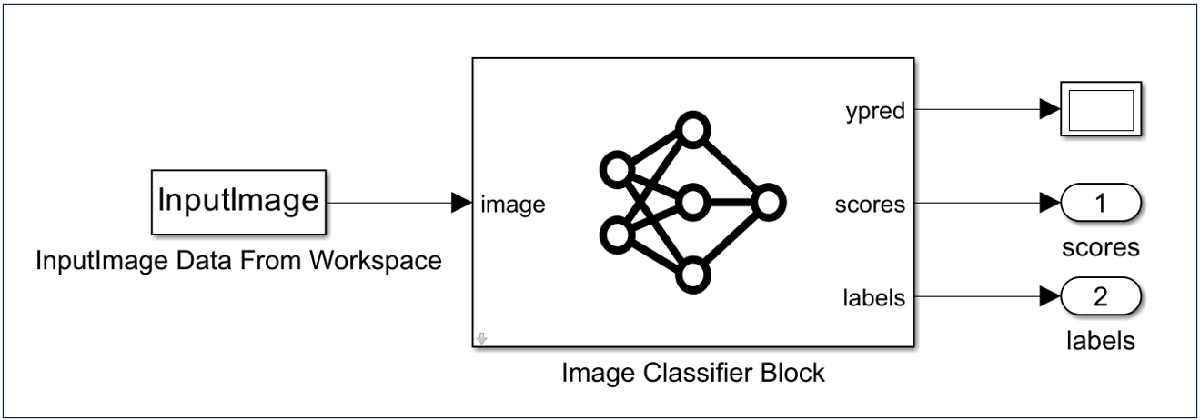

- Parallel Processing Unit for Optimized Code Generation

Use PPU to implement models with large data processing requirements or fast execution time requirements.

- PIL Simulation Using nSIM Simulator

Run PIL simulations and test PPU based application models using nSIM simulator.

- Generate Code and Deploy Using SoC Builder

Generate code and run it on the target hardware board using the SoC Builder tool.

- Generate Software Executables for Multicore Models

Generate ELF file for all participating homogenous cores of Infineon AURIX.

- Task Duration

Set the execution time or duration of a task in Task Manager block.

- What is Task Execution?

Learn the definition of task execution and task life-cycle in a processor.

- Task Execution Playback Using Recorded Data

Replay task execution timing using recorded task timing data from previous simulations or processors.