このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Sample and Hold

入力信号のサンプルとホールド

ライブラリ:

DSP System Toolbox /

Signal Operations

DSP System Toolbox HDL Support /

Signal Operations

説明

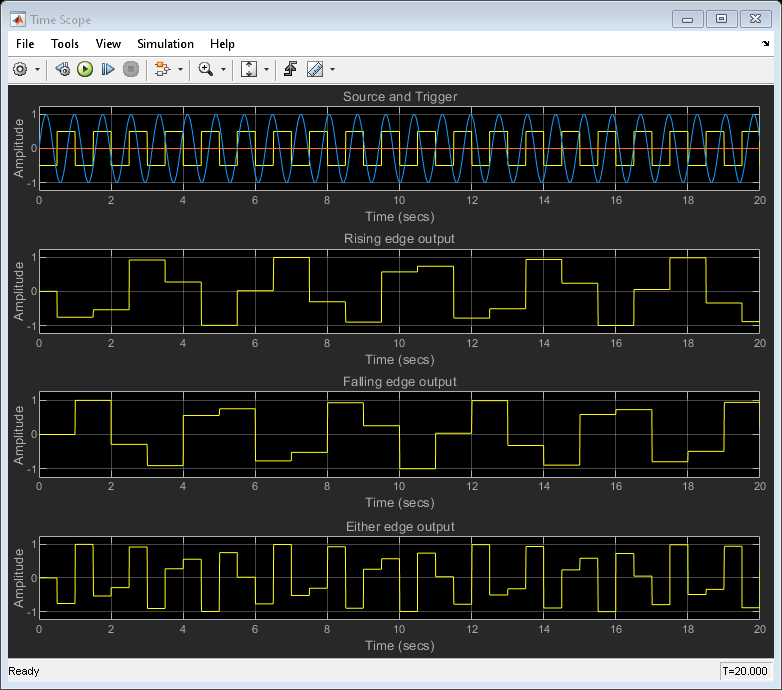

Sample and Hold ブロックは、トリガー端子 ( でマーク) でトリガー イベントを受信するたびに、信号端子で入力を取得します。その後、ブロックは次のトリガー イベントが発生するまで、取得した入力値で出力を保持します。

でマーク) でトリガー イベントを受信するたびに、信号端子で入力を取得します。その後、ブロックは次のトリガー イベントが発生するまで、取得した入力値で出力を保持します。

例

端子

入力

出力

パラメーター

ブロックの特性

データ型 |

|

直達 |

|

多次元信号 |

|

可変サイズの信号 |

|

ゼロクロッシング検出 |

|

拡張機能

バージョン履歴

R2006a より前に導入