SPICE NMOS

SPICE-compatible N-Channel MOSFET

Libraries:

Simscape /

Electrical /

Additional Components /

SPICE Semiconductors

Description

The SPICE NMOS block represents a SPICE-compatible negative-channel (N-Channel) metal-oxide semiconductor (MOS) field-effect transistor (FET). If the gate-source voltage increases the channel conductance increases. If the gate-source voltage is decreased, the channel conductance decreases.

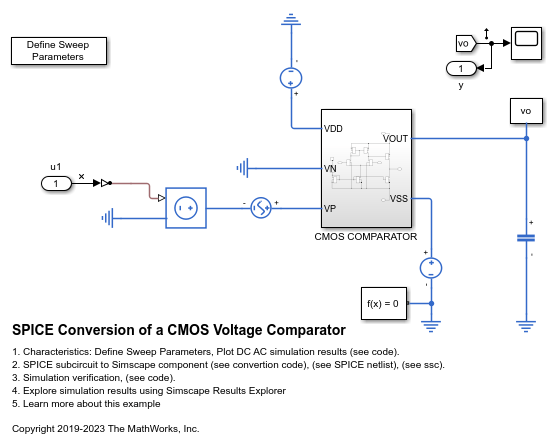

SPICE, or Simulation Program with Integrated Circuit Emphasis,

is a simulation tool for electronic circuits. You can convert some SPICE subcircuits into

equivalent Simscape™

Electrical™ models using the Environment Parameters block and

SPICE-compatible blocks from the Additional Components library. For more

information, see subcircuit2ssc.

Equation Variables

Variables for the SPICE NMOS block equations include:

Variables that you define by specifying parameters for the SPICE NMOS block. The visibility of some of the parameters depends on the value that you set for other parameters. For more information, see Parameters.

Geometry-adjusted variables, which depend on several of the values that you specify using parameters for the SPICE NMOS block. For more information, see Geometry-Adjusted Variables.

Temperature, T, which is

300.15Kby default. You can use a different value by specifying parameters for the SPICE NMOS block or by specifying parameters for both the SPICE NMOS block and an Environment Parameters block. For more information, see Transistor Temperature.Minimal conductance, GMIN, which is

1e-121/Ohmby default. You can use a different value by specifying a parameter for an Environment Parameters block. For more information, see Minimal Conduction.Thermal voltage, Vtn. For more information, see Thermal Voltage.

Several variables in the equations for the SPICE N-channel MOSFET model consider the geometry of the device that the block represents. These geometry-adjusted variables depend on variables that you define by specifying SPICE NMOS block parameters. The geometry-adjusted variables depend on these variables:

AREA — Area of the device

SCALE — Number of parallel connected devices

The associated unadjusted variable

The table includes the geometry-adjusted variables and the defining equations.

| Variable | Description | Equation |

|---|---|---|

| KPd | Geometry-adjusted transconductance |

|

| ISd | Geometry-adjusted bulk saturation current |

|

| JSd | Geometry-adjusted bulk junction saturation current density |

|

| CBDd | Geometry-adjusted zero-bias bulk-drain capacitance |

|

| CBSd | Geometry-adjusted zero-bias bulk-source capacitance |

|

| CGSOd | Geometry-adjusted gate-source overlap capacitance |

|

| CGDOd | Geometry-adjusted gate-drain overlap capacitance |

|

| CGBOd | Geometry-adjusted gate-bulk overlap capacitance |

|

| CJ | Geometry-adjusted bottom capacitance per junction area |

|

| CJSW | Geometry-adjusted sidewall capacitance per junction perimeter |

|

| RDd | Geometry-adjusted drain resistance |

|

| RSd | Geometry-adjusted source resistance |

|

| RSHd | Geometry-adjusted sheet resistance |

|

There are two different options for defining transistor temperature, T:

Fixed temperature — The block uses a temperature that is independent of the circuit temperature when the Model temperature dependence using parameter in the Temperature settings of the SPICE NMOS block is set to

Fixed temperature. For this model, the block sets T equal to TFIXED.Device temperature — The block uses a temperature that depends on circuit temperature when the Model temperature dependence using parameter in the Temperature settings of the SPICE NMOS block is set to

Device temperature. For this model, the block defines temperature asWhere:

TC is the circuit temperature.

If there is not an Environment Parameters block in the circuit, TC is equal to 300.15 K.

If there is an Environment Parameters block in the circuit, TC is equal to the value that you specify for the Temperature parameter in the SPICE settings of the Environment Parameters block. The default value for the Temperature parameter is

300.15K.TOFFSET is the offset local circuit temperature.

Minimal conductance, GMIN, has a default value of

1e–12

1/Ohm. To specify a different value:

If there is not already an Environment Parameters block in the circuit, add one.

In the SPICE settings of the Environment Parameters block, specify the desired GMIN value for the GMIN parameter.

Vtn is the thermal voltage, which is defined as

Where:

N is the emission coefficient.

T is the transistor temperature. For more information, see Transistor Temperature.

k is the Boltzmann constant.

q is the elementary charge on an electron.

Parameters Calculations

The tables show how the SPICE NMOS block determines some of its parameters based on values that you specify.

Drain Resistance

| Parameter Values | Geometry-Adjusted Transistor Drain Resistance | ||

|---|---|---|---|

| Drain resistance, RD | Sheet resistance, RSH | Number of drain squares, NRD | |

NaN | NaN | NaN | 0 |

NaN | RSH | NaN | 0 |

NaN | NaN | NRD | 0 |

| RD | NaN or RSH | NaN or NRD | RDd |

NaN | RSH | NRD | RSHd*NRD |

Source Resistance

| Parameter Values | Geometry-Adjusted Transistor Source Resistance | ||

|---|---|---|---|

| Source resistance, RS | Sheet resistance, RSH | Number of source squares, NRS | |

NaN | NaN | NaN | 0 |

NaN | RSH | NaN | 0 |

NaN | NaN | NRS | 0 |

| RS | NaN or RSH | NaN or NRS | RSd |

NaN | RSH | NRS | RSHd*NRS |

Transconductance and Surface Mobility

| Parameter Values | Geometry-Adjusted Transconductance (level 1), in A/V2 | Geometry-Adjusted Transconductance (level 3), in A/V2 | Surface mobility (level 3), in cm2/s/V | ||

|---|---|---|---|---|---|

| Oxide thickness, TOX | Surface mobility, U0 | Transconductance, KP | |||

NaN | NaN | NaN | 2e-5 (default value) | 2e-5 (default value) | 600 (default value) |

NaN | NaN | KP | KPd | KPd | 600 |

NaN | U0 | NaN | 2e-5 | UO*EPXox/1e-7 | U0 |

NaN | U0 | KP | KPd | KPd | U0 |

| TOX | NaN | NaN | 600*EPXox/TOX | 600*EPXox/TOX | 600 |

| TOX | NaN | KP | KPd | KPd | 600 |

| TOX | U0 | NaN | UO*EPXox/TOX | UO*EPXox/TOX | U0 |

| TOX | U0 | KP | KPd | KPd | U0 |

Oxide Thickness and Threshold Voltage

| Parameter Values | Surface potential, PHI (level 1), in V | Threshold voltage, VTO (level 1), in V | Surface potential, PHI (level 3), in V | Threshold voltage, VTO (level 3), in V | |||

|---|---|---|---|---|---|---|---|

| Oxide thickness, TOX | Substrate doping, NSUB | Surface potential, PHI | Threshold voltage, VTO | ||||

NaN | NaN | NaN | NaN | 0.6 (default value) | 0 (default value) | 0.6 (default value) | 0 (default value) |

NaN | NaN | NaN | VTO | 0.6 | VTO | 0.6 | VTO |

NaN | NaN | PHI | NaN | PHI | 0 | PHI | 0 |

NaN | NaN | PHI | VTO | PHI | VTO | PHI | VTO |

NaN | NSUB | NaN | NaN | 0.6 | 0 | PHI (1e-7, NSUB) | VTO (1e-7, NSUB) |

NaN | NSUB | NaN | VTO | 0.6 | VTO | PHI (1e-7, NSUB) | VTO |

NaN | NSUB | PHI | NaN | PHI | 0 | PHI | VTO (1e-7, NSUB) |

NaN | NSUB | PHI | VTO | PHI | VTO | PHI | VTO |

TOX | NaN | NaN | NaN | 0.6 | 0 | 0.6 | 0 |

TOX | NaN | NaN | VTO | 0.6 | VTO | 0.6 | VTO |

TOX | NaN | PHI | NaN | PHI | 0 | PHI | 0 |

TOX | NaN | PHI | VTO | PHI | VTO | PHI | VTO |

TOX | NSUB | NaN | NaN | PHI (NSUB, TOX) | VTO (NSUB, TOX) | PHI (NSUB, TOX) | VTO (NSUB, TOX) |

TOX | NSUB | NaN | VTO | PHI (NSUB, TOX) | VTO | PHI (NSUB, TOX) | VTO |

TOX | NSUB | PHI | NaN | PHI | VTO (NSUB, TOX) | PHI | VTO (NSUB, TOX) |

TOX | NSUB | PHI | VTO | PHI | VTO | PHI | VTO |

Where PHI (NSUB, TOX), PHI (1e-7,

NSUB), VTO (NSUB, TOX), and VTO (1e-7,

NSUB) are obtained using these equations:

Bulk-Source Diode Model

The table shows the equations that define the relationship between the bulk-source current, Ibs, and the bulk-source voltage, Vbs. As applicable, the model parameters are first adjusted for temperature. For more information, see Temperature Dependence.

| Applicable Range of Vbs Values | Corresponding Ibs Equation |

|---|---|

Where:

ISbs is the bulk saturation current, such that, if:

and , .

Where:

JSd is the geometry-adjusted bulk junction saturation current density.

AS is the source area.

If or , , where ISd is the geometry-adjusted bulk saturation current.

Vtn is the thermal voltage. For more information, see Thermal Voltage.

Gmin is the minimal conductance. For more information, see Minimal Conduction.

Bulk-Drain Diode Model

The table shows the equations that define the relationship between the bulk-drain current Ibd, and the bulk-drain voltage, Vbd. As applicable, the model parameters are first adjusted for temperature. For more information, see Temperature Dependence.

| Applicable Range of Vbd Values | Corresponding Ibd Equation |

|---|---|

Where:

ISbd is the bulk drain current, such that:

If and , .

Where:

JSd is the geometry-adjusted bulk junction saturation current density.

AD is the drain area.

If or , , where ISd is the geometry-adjusted bulk saturation current.

Vtn is the thermal voltage. For more information, see Thermal Voltage.

Gmin is the minimal conductance. For more information, see Minimal Conduction.

Level 1 Drain Current Model

This table shows relationship between the drain current, Id, and the drain-source voltage, Vds, in normal mode (Vds ≥ 0). As applicable, model parameters are first adjusted for temperature.

Normal Mode

| Applicable Range of Vgs and Vds Values | Corresponding Id Equation |

|---|---|

Where:

Von depends on Vbs and PHI.

Applicable Relationship of Vbs and PHI Values Corresponding Von Equation MTYPE is 1.

BETA is

KP is:

The Transconductance, KP, if this parameter has a numerical value.

, if Transconductance, KP is

NaNand you specify values for both the Oxide thickness, TOX and Substrate doping, NSUB parameters.

WIDTH is the channel width.

LENGTH is the channel length.

LD is the lateral diffusion.

VBI is a built-in voltage value the block uses in calculations. The value is a function of temperature. For a detailed definition, see Temperature Dependence.

PHI is:

The Surface potential, PHI, if this parameter has a numerical value.

, if Surface potential, PHI is

NaNand you specify values for both the Oxide thickness, TOX and Substrate doping, NSUB parameters.

LAMBDA is the channel modulation.

GAMMA is:

The Bulk threshold, GAMMA, if this parameter has a numerical value.

, if Bulk threshold, GAMMA is

NaNand you specify values for both the Oxide thickness, TOX and Substrate doping, NSUB parameters.

ε0 is the permittivity of free space, 8.854214871e-12 F/m.

ni is the carrier concentration of intrinsic silicon, 1.45e10 cm-3.

This table shows relationship between the drain current Id and the drain-source voltage Vds in inverse mode (Vds < 0). As applicable, model parameters are first adjusted for temperature.

Inverse Mode

| Applicable Range of Vgd and Vds Values | Corresponding Id Equation |

|---|---|

Von depends on Vbd and PHI.

| Applicable Relationship of Vbs and PHI Values | Corresponding Von Equation |

|---|---|

Level 3 Drain Current Model

The block provides the following model for drain current Ids in normal mode () after adjusting the applicable model parameters for temperature.

Where:

IDS0 is the Basic Drain Current Model.

ScaleVMAX is the Velocity Saturation Scaling.

ScaleLChan is the Channel Length Modulation Scaling.

ScaleINV is the Weak Inversion Scaling.

The block uses the same model for drain current in inverse mode (), with the following substitutions:

The relationship between the drain current, Ids, and the drain-source voltage, Vds is

Where:

BETA is calculated as described in Level 1 Drain Current Model.

FGATE is calculated as

Where:

THETA models the dependence of the mobility on the gate-source voltage.

If you specify a nonzero value for the Fast surface state density, NFS parameter, the block calculates Von using this equation:

Otherwise,

The block calculates xn as

The block calculates Vbulk as follows:

If

Otherwise, the block calculates Vbulk as

Thermal voltage such that

The block calculates VTH using the following equation:

For information about how the block calculates VBI, see Temperature Dependence.

ETA is the Vds dependence threshold volt, ETA.

-

Where εox is the permittivity of the oxide and TOX is the Oxide thickness, TOX.

If you specify a nonzero value for the Junction depth, XJ parameter and a value for the Substrate doping, NSUB parameter, the block calculates Fs using these equations:

Where εsi is the permittivity of silicon.

Otherwise,

The block calculates FB as

The block calculates Fn as

DELTA is the width effect on threshold.

VDSX is the lesser of VDS and the saturation voltage, Vdsat.

If you specify a positive value for the Max carrier drift velocity, VMAX parameter, the block calculates Vdsat using the following equation:

Otherwise, the block calculates Vdsat as

If you specify a positive value for the Max carrier drift velocity, VMAX parameter, the block calculates ScaleVMAX as

Otherwise,

The block scales the drain current to account for channel length modulation if the block meets all of the following criteria:

The Max carrier drift velocity, VMAX is less than or equal to zero or α is nonzero.

The block scales the drain current using the following equation:

To calculate the block:

Calculates the intermediate value .

If you specify a positive value for the Max carrier drift velocity, VMAX parameter, the block computes the intermediate value gdsat as the greater of 1e-12 and the result of the following equation:

Where:

Then, the block uses the following equation to calculate the intermediate value Δl0:

Where

Otherwise, the block uses the following equation to calculate the intermediate value as

The block checks for punch through and calculates .

If

the block calculates using the following equation:

Otherwise,

If VGS is less than Von, the block calculates ScaleINV using the following equation:

Otherwise,

Junction Charge Model

The block models Junction Overlap Charges and Bulk Junction Charges.

The block calculates the following junction overlap charges:

Where:

QGS is the gate-source overlap charge.

CGSOd is the geometry adjusted gate-source overlap capacitance.

WIDTH is the channel width.

Where:

QGD is the gate-drain overlap charge.

CGDOd is the geometry adjusted gate-drain overlap capacitance.

Where:

QGB is the gate-bulk overlap charge.

CGBOd is the geometry adjusted gate-bulk overlap capacitance.

LENGTH is the channel length.

LD is the lateral diffusion.

This table shows relationship between the bulk-drain bottom junction charge Qbottom and the junction voltage, Vbd. As applicable, model parameters are first adjusted for temperature.

| Applicable Range of Vbd Values | Corresponding Qbottom Equation |

|---|---|

if otherwise. | |

if otherwise. |

Where:

PB is the bulk junction potential.

FC is the capacitance coefficient.

CBDd is the geometry-adjusted zero-bias bulk-drain capacitance.

CJd is the geometry-adjusted bottom capacitance per junction area.

AD is the drain area.

MJ is the bottom grading coefficient.

To calculate the bulk-source bottom junction charge, the block substitutes variables in the equations in the preceding table. The block substitutes:

Vbs for Vbd

AS for AD

CBSd for CBDd

This table shows relationship between the bulk-drain sidewall junction charge Qsidewall and the junction voltage Vbd. As applicable, model parameters are first adjusted for temperature.

| Applicable Range of Vbd Values | Corresponding Qsidewall Equation |

|---|---|

Where:

CJSWd is the geometry adjusted sidewall capacitance per junction perimeter.

PD is the drain perimeter.

MGSW is the side grading coefficient.

To calculate the bulk-source sidewall junction charge and the sidewall junction voltage, the block substitutes variables in the equations in the preceding table. The block substitutes:

Vbs for Vbd

PS for PD

Capacitance Model

The SPICE NMOS block allows you to model the transistor capacitance model in three different ways:

No intrinsic capacitance model

This table shows the relationship between the operational regions of the transistor and the gate-bulk, gate-drain, and gate-source capacitances.

| Operational region | Gate-Bulk, Cgb, Gate-Drain, Cgd, and Gate-Source, Cgs, Equations | |

|---|---|---|

| Accumulation region, | ||

| Depletion region, | ||

| Saturation region, | if then: | if then: |

| Linear region, | ||

where:

is the flat-band voltage.

Vsatmin is the minimum saturation voltage. It is a predefined parameter equal to

1V.

These equations are continuous between the depletion region and the accumulation region, and discontinuous between the depletion and the inversion region. Other SPICE tools apply smoothing functions between the inversion and depletion regions.

where m is a predefined smoothing constant.

This table shows the relationship between the operational regions of the transistor and the gate, bulk, channel, drain, and source charges for a level 1 MOS.

| Operational region | Level-1 Charges Equations |

|---|---|

| Accumulation region, | |

| Depletion region, | |

| Saturation region, | |

| Linear region, |

where:

is the charge in channel. Qc needs to be partitioned between Qd and Qs.

where:

Qg is the gate charge.

Qb is the bulk charge.

Qd is the drain charge.

Qs is the source charge.

is the charge in channel. Qc needs to be partitioned between Qd and Qs.

This table shows the relationship between the operational regions of the transistor and the gate, bulk, channel, drain, and source charges for a level-3 MOS.

| Operational region | Level-3 Charges Equations |

|---|---|

| Accumulation region, | |

| Depletion region, | |

| Saturation region, | |

| Linear region, |

where:

Vdsat is the saturation voltage

FB is the body effect coefficient

ETA is the drain-source voltage threshold coefficient

and are smoothing factors between depletion and accumulation regions to help with convergence.

Temperature Dependence

The transconductance as a function of the transistor temperature is

Where:

KPd is the geometry-adjusted transconductance.

T is the transistor temperature. For more information, see Transistor Temperature.

Tmeas is the parameter extraction temperature.

The surface potential as a function of the transistor temperature is

Where:

PHI is the surface potential.

k is the Boltzmann constant.

q is the elementary charge on an electron, 1.6021918e-19 C.

EG is the activation energy, such that:

The built-in voltage as a function of the transistor temperature is

Where:

VBI is the built-in voltage.

VTO is the threshold voltage. VTO depends on the value that you specify for the Threshold voltage, VTO parameter in the DC currents settings. If you specify a numerical value, VTO is evaluated as that value. If you specify a nonnumerical value (

NAN) and you specify numerical values for both the Oxide thickness, TOX and Substrate doping, NSUB parameters in the Process settings, then VTO is evaluated as , Where:Φ depends on the gate type, which you specify using the Gate type, TPG parameter. If you specify

Aluminum (0), . Otherwise, , Where:MTYPE is the transistor type. For an N-channel MOSFET, MTYPE = 1.

TPG represents the gate type and also depends on the option that you specify for the Gate type, TPG parameter in the Process settings. If you specify

Opposite of substrate (1)— TPG = 1Same as substrate (-1)— TPG = -1

NSS is the surface state density.

TOX is the oxide thickness.

ε0 is the permittivity of free space.

GAMMA is the bulk threshold. GAMMA depends on the value that you specify for the Bulk threshold, GAMMA parameter in the DC currents settings. If you specify a numerical value, GAMMA is evaluated as that value. If you specify a nonnumerical value (

NAN) and you specify numerical values for both the Oxide thickness, TOX and Substrate doping, NSUB parameters in the Process settings, then VTO is evaluated as , where NSUB is the substrate doping.

The bulk saturation current as a function of the transistor temperature is

Where:

ISd is the geometry-adjusted bulk saturation current.

ND is the emission coefficient.

The bulk junction saturation current density as a function of the transistor temperature is

Where JSd is the geometry-adjusted bulk junction saturation current density.

The bulk junction potential as a function of the transistor temperature is

Where PB is the bulk junction potential.

The bulk-drain junction capacitance as a function of the transistor temperature is

Where:

CBDd is the geometry adjusted zero-bias bulk-drain capacitance.

MJ is the bottom grading coefficient.

The block uses the CBD(T) equation to calculate:

The bulk-source junction capacitance by substituting CBSd, the geometry-adjusted zero-bias bulk-source capacitance, for CBDd.

The bottom junction capacitance by substituting CJd, the geometry-adjusted bottom capacitance per junction area for CBDd.

The relationship between the sidewall junction capacitance CJSW and the transistor temperature, T, is

Where:

CJSWd is the side geometry-adjusted sidewall capacitance per junction perimeter.

MJSW is the side grading coefficient.

Examples

Assumptions and Limitations

The block does not support noise analysis.

The block applies initial conditions across junction capacitors and not across the block ports.

Ports

Conserving

Parameters

References

[1] G. Massobrio and P. Antognetti. Semiconductor Device Modeling with SPICE. 2nd Edition. New York: McGraw-Hill, 1993.

[2] Ping Yang, et al. ‘An Investigation of the Charge Conservation Problem for MOSFET Circuit Simulation’. IEEE Journal of Solid-State Circuits, vol. 18, no. 1, Feb. 1983, pp. 128–38. DOI.org (Crossref), doi:10.1109/JSSC.1983.1051909.

Extended Capabilities

Version History

Introduced in R2009a