時間ベースのスケジューリング モデル例

シングルレート モデリング (OSなしのベア ボード)

このモデルでは、ベアボード ターゲット (オペレーティング システムが搭載されていない) に構成したシングル レートの離散時間モデルのコード生成を示します。

モデル例を開く

モデル例 SingleRateBareBoard を開きます。

open_system('SingleRateBareBoard')

このモデルは 1 つのサンプル時間を使用し、ブロック線図の更新時にサンプル時間の色を表示するように設定されています。Inport ブロック In1_1s と In2_1s は 1 秒のサンプル時間を指定し、これは、モデル コンフィギュレーション パラメーター [周期的なサンプル時間の制約] の設定により実施されます。

このモデルは注釈付きの色分けされたサンプル時間を表示するように設定されています。モデルを開いた後に表示するには、Ctrl+D を押してブロック線図を更新します。凡例を表示するには、Ctrl+J を押します。このモデルは 1 つのサンプル時間で設定されているため、モデル内で最速の離散サンプル時間を表す赤色で表示されます。

シングルタスク モードのマルチレート モデル化 (OS なしのベア ボード)

このモデルでは、ベアボード ターゲット (オペレーティング システムが搭載されていない) に構成したマルチ レートの離散時間モデルに生成されるコードを説明します。

モデル例を開く

モデル例 MultirateSingleTaskingBareBoard を開きます。

open_system('MultirateSingleTaskingBareBoard')

このモデルには 2 つのサンプル時間が含まれています。Inport ブロック 1 と Inport ブロック 2 は、それぞれ 1 秒と 2 秒のサンプル時間を指定します。これには、モデル コンフィギュレーション パラメーター [周期的なサンプル時間の制約] の設定が適用されています。ソルバーにはシングルタスク操作が設定されています。したがってプリエンプションは発生せず、異なるサンプル時間で実行されるブロック間に Rate Transition ブロックは含められません。

このモデルは注釈付きの色分けされたサンプル時間を表示するように設定されています。モデルを開いた後に表示するには、Ctrl+D を押してブロック線図を更新します。凡例を表示するには、Ctrl+J を押します。赤色はモデル内の最速の離散サンプル時間を表し、緑色は 2 番目に速いサンプル時間を、黄色は混在しているサンプル時間を表します。

マルチタスク モードのマルチレート モデル化 (OS なしのベア ボード)

このモデルでは、マルチタスクのベアボード ターゲット (オペレーティング システムのないもの) に構成したマルチレートの離散時間モデル用の生成コードを説明します。

モデル例を開く

モデル例 MultirateMultitaskingBareBoard を開きます。

open_system('MultirateMultitaskingBareBoard')

モデル例の確認

このモデルには 2 つのサンプル時間が含まれています。Inport ブロック 1 と Inport ブロック 2 は、それぞれ 1 秒と 2 秒のサンプル時間を指定します。これには、モデル コンフィギュレーション パラメーター [周期的なサンプル時間の制約] の設定が適用されています。ソルバーにはマルチタスク動作が設定されています。つまり、1 秒のタスクが 2 秒のタスクをプリエンプトする場合に、Rate Transition ブロックではデータの整合性が確実に維持される必要があります。Simulink® および Simulink Coder™ によって適切なレート変換が常に適用されます。このモデルでは明示的に Rate Transition ブロックを指定します。または、モデル コンフィギュレーション パラメーター [データ転送に対するレート変換を自動的に取り扱う] を設定して Simulink でこのブロックを自動的に挿入できます。

このモデルは、ブロック線図の更新時にサンプル時間の色を表示するように設定されています。モデルを開いた後に表示するには、Ctrl+D を押してブロック線図を更新します。凡例を表示するには、Ctrl+J を押します。赤色はモデル内の最速の離散サンプル時間を表し、緑色は 2 番目に速いサンプル時間を、黄色は混在しているサンプル時間を表します。

データ転送の仮定

タスク間データ転送の操作の基礎:

1 つの読み取りタスクと 1 つの書き込みタスクの間でデータ遷移が発生する。

バイト単位の変数の読み取りと書き込みはアトミックである。

データの遷移中に 2 つのタスクが対話した場合、一方のタスクがもう一方のタスクをプリエンプトする場合がある。

周期的タスクの場合、速いレートのタスクの優先順位は遅いレートのタスクよりも高くなる。すなわち、速いレートのタスクは遅いレートのタスクを常にプリエンプトする。

タスクは 1 つのプロセッサ上で実行される。タイム スライスは許可されない。

プロセスは、特にデータがタスク間で転送されているときはクラッシュまたは再起動しない。

マルチタスク モードのマルチレート モデル化 (VxWorks® OS)

この例では、マルチタスク オペレーティング システム ターゲット (VxWorks®) 用に設定されたマルチレート離散モデルのコードを生成します。このモデルには 2 つのサンプル時間が含まれています。Inport ブロック 1 と Inport ブロック 2 は、それぞれ 1 秒と 2 秒のサンプル時間を指定します。これには、モデル コンフィギュレーション パラメーター [周期的なサンプル時間の制約] の設定が適用されています。ソルバーにはマルチタスク動作が設定されています。つまり、1 秒のタスクが 2 秒のタスクをプリエンプトする場合に、Rate Transition ブロックではデータの整合性が確実に維持される必要があります。Simulink® とコード ジェネレーターは、適切なレート変換を適用します。このモデルでは明示的に Rate Transition ブロックを指定します。または、モデル コンフィギュレーション パラメーター [データ転送に対するレート変換を自動的に取り扱う] を設定して、このブロックを挿入するよう Simulink® に指示することができます。

このモデルは注釈付きの色分けされたサンプル時間を表示するように設定されています。モデルを開いた後に表示するには、Ctrl+D を押してブロック線図を更新します。凡例を表示するには、Ctrl+J を押します。赤色はモデル内の最速の離散サンプル時間を表し、緑色は 2 番目に速いサンプル時間を、黄色は混在しているサンプル時間を表します。

モデル例

model = 'MultirateMultitaskingOS';

open_system(model);

確定性とデータの整合性のトレードによるシステム性能の改善

このモデルは、Rate Transition ブロックがマルチレート、マルチタスク モデルで使用された場合の操作モードの相違点を説明します。Rate Transition ブロックの柔軟なオプションにより、アプリケーションに最適なモードを選択できます。確定レベルとデータの整合性をトレードし、システム性能を改善できます。

Rate Transition ブロックの操作モード

データの整合性と確定性を確保 (DetAndInteg): 信号 (幅の広い信号のすべての要素を含む) のすべてのデータ バイトが同じタイム ステップからとなるようにデータが転送されます。また、データがあるレートから別のレートに転送される相対サンプル時間 (遅延) は常に同じになります。ANSI® C コードのみが使用され、ターゲット固有の 'クリティカル セクション' 保護は必要ありません。

整合性を確保 (IntegOnly): 信号 (幅の広い信号のすべての要素を含む) のすべてのデータ バイトが同じタイム ステップからとなるようにデータが転送されます。ただし、あるデータ転送から次のデータ転送までの、データが転送される相対サンプル時間 (遅延) は異なることがあります。このモードでは、データの読み取り/書き込みを行うコードが DetandInt モードよりも頻繁に実行されます。最悪の場合、遅延は DetandInt モードと等しくなりますが、遅延は短くなる可能性があり、これは一部のアプリケーションにおいて重要です。また、このモードは DetandInt モードでサポートされない非同期レートとの間のデータ転送をサポートします。ANSI-C コードのみが使用され、ターゲット固有の 'クリティカル セクション' 保護は必要ありません。

データ整合操作は行われない (None): この場合、Rate Transition ブロックはコードを生成しません。このモードは、スカラー データ型のアトミック アクセスが保証される一部のアプリケーションにおいて、データの相対時相値が重要でない場合に許容されます。このモードでは遅延は発生しません。

データ転送の仮定

タスク間データ転送の操作の基礎:

1 つの読み取りタスクと 1 つの書き込みタスクの間でデータ遷移が発生する。

バイト単位の変数の読み取りと書き込みはアトミックである。

データの遷移中に 2 つのタスクが対話した場合、一方のタスクがもう一方のタスクをプリエンプトする場合がある。

周期的タスクの場合、速いレートのタスクの優先順位は遅いレートのタスクよりも高くなる。すなわち、速いレートのタスクは遅いレートのタスクを常にプリエンプトする。

すべてのタスクは 1 つのプロセッサ上で実行される。タイム スライスは許可されない。

プロセスはクラッシュまたは再起動しない (特にデータがタスク間を転送されているとき)。

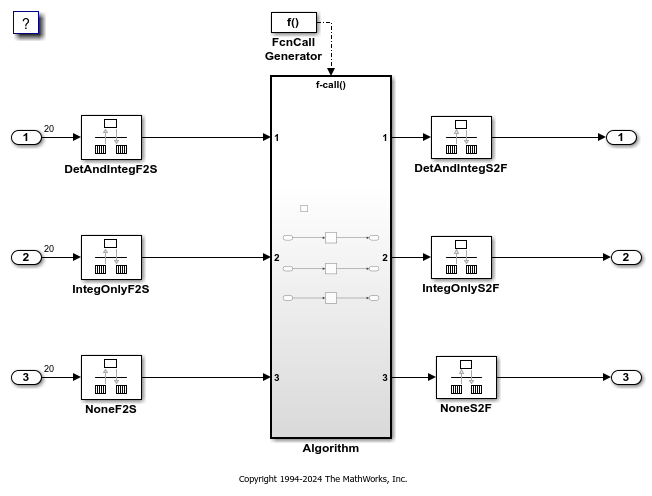

モデル MultirateMultitaskingRateTransitions

open_system('MultirateMultitaskingRateTransitions')

モデル MultirateMultitaskingRateTransitions では、以下の Rate Transition ブロックの操作モードにおける相違を示します。

Rate Transition ブロック DetAndIntegF2S

確定性とデータの整合性 (高速から低速への遷移):

ブロック出力は永続的なデータ バッファーとして使用される。

データは遅いレートで出力に書き込まれるが、速いレート コンテキスト時に実行される。

遅いレートから見えるデータは常に、速いレートと遅いレートの両方が最後に実行されたときの値となる。遅いレートが実行されている間、速いレートによる後続のステップ (および関連付けられたデータ更新) は、遅いレートからは見えない。

Rate Transition ブロック DetAndIntegS2F

確定性とデータの整合性 (低速から高速への遷移):

2 つの永続的なデータ バッファー、内部バッファーおよびブロック出力を使用する。

内部バッファーは遅いレートで出力にコピーされるが、速いレート コンテキスト時に実行される。

内部バッファーは遅いレートで遅いレート コンテキスト時に書き込まれる。

速いレートから見えるデータは常に遅延しており、したがってデータは遅いレート コードの前のステップからのものとなる。

Rate Transition ブロック IntegOnlyF2S

データの整合性のみ (高速から低速への遷移):

ブロック出力は永続的なデータ バッファーとして使用される。

読み取り処理中のフラグが立っていなければ、データは速いレート コンテキスト時にバッファーに書き込まれる。

フラグが設定されるとデータが遅いレートでバッファーから出力にコピーされ、その後フラグはクリアされる。これは確定的なケースと比較すると追加のコピーとなる。

遅いレートから見えるデータは、遅いレートと速いレートの両方が実行された時点からのものではなく、速いレートのより最近のステップからのものである場合がある。

Rate Transition ブロック IntegOnlyS2F

データの整合性のみ (低速から高速への遷移):

2 つの永続的なデータ バッファー (いずれも内部バッファー) を使用する。

2 つのバッファーの一方は常に速いレートで出力にコピーされる。

2 つのバッファーの一方は遅いレートで遅いレート コンテキスト時に書き込まれ、その後アクティブなバッファーが切り替わる。

速いレートから見えるデータは確定的なケースの場合よりも最近のものになることがある。遅いレートと速いレートの両方にヒットがある場合は特に、速いレートからは遅いレートの前の値が見える。ただし、速いレートの後続のステップからは更新された値が見えることがある (遅いレートによってアクティブでないバッファーが更新され、アクティブなバッファー フラグが切り替わる場合)。

Rate Transition ブロック NoneF2S

確定性とデータの整合性が見送られる場合、Rate Transition ブロックのコードは生成されません。

Rate Transition ブロック NoneS2F

確定性とデータの整合性が見送られる場合、Rate Transition ブロックのコードは生成されません。

bdclose('MultirateMultitaskingRateTransitions');