このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

MATLAB テストベンチを作成する

HDL Verifier™ ソフトウェアは、MATLAB® 環境内で HDL モジュールを検証する手段を提供します。これを行うには、HDL モデルと、HDL モデルとデータを共有できる MATLAB 関数をコーディングします。この章では、HDL シミュレータと通信する MATLAB テストベンチ関数のプログラミング、インターフェイス、およびスケジュール規則について説明します。Vivado® シミュレータとのコシミュレーションは MATLAB 関数のコシミュレーションをサポートしていないことに注意してください。

MATLAB テスト ベンチ 関数を使用すると、HDL モデルまたはモデル内のコンポーネントのパフォーマンスを検証できます。テストベンチ機能は、テスト対象の HDL 設計の入力ポートに接続された信号に値を駆動し、モジュールの出力ポートから信号値を受信します。

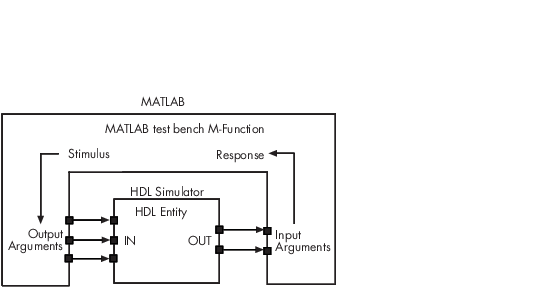

次の図は、テストベンチ シミュレーション セッション中に MATLAB 関数がどのようにラップアラウンドして HDL シミュレータと通信するかを示しています。

MATLAB とリンクすると、HDL シミュレーターはクライアントとして機能し、MATLAB はサーバーとして機能します。次の図は、TCP/IP ソケット ポート 4449 でサーバーに接続する複数クライアントのシナリオを示しています。

MATLAB サーバーは、複数の同時 HDL シミュレータ セッションと HDL モジュールを処理できます。ただし、サーバーが各モジュールおよびセッションに関連付けられた I/O を追跡できるようにするには、推奨ガイドラインに従う必要があります。提供された関数 hdldaemon を使用して起動する MATLAB サーバーは、同じコンピューターまたは別のコンピューターで実行されている HDL シミュレーターのインスタンスからの接続要求を待機します。サーバーはリクエストを受信すると、HDL 設計内のモジュールに代わってタスクを実行するためにコーディングした指定された MATLAB 関数を実行します。サーバーの起動時に指定するパラメータは、サーバーが共有メモリまたは TCP/IP ソケット通信リンクを確立するかどうかを示します。

有効なマシン構成については、コシミュレーション構成 を参照してください。

メモ

テストベンチ機能とコンポーネント機能のプログラミング、インターフェイス、およびスケジュール規則は実質的に同一です。ほとんどの場合、両方のタイプの機能に同じ手順が適用されます。

HDL シミュレータとのコシミュレーション用の MATLAB テストベンチ セッションを作成するには、次のワークフロー手順に従います。

MATLAB テストベンチ用の HDL モジュールの作成

MATLAB による検証用 HDL モジュールのコーディング

HDL Verifier インターフェースにおける通信の最も基本的な要素は HDL モジュールです。インターフェースは、HDL シミュレータと MATLAB 間のすべてのデータをポート データとして渡します。HDL Verifier ソフトウェアは、既存の HDL モジュールと連携して動作します。ただし、MATLAB 検証を対象とする HDL モジュールをコーディングする場合は、その名前、2 つの環境間で共有されるデータのタイプ、および方向モードを考慮する必要があります。

MATLAB テストベンチで使用する HDL モジュール名を選択してください

必須ではありませんが、HDL モジュールに名前を付ける場合は、MATLAB 関数名としても使用できる名前を選択することを検討してください。(一般に、VHDL® または Verilog® と MATLAB の命名規則は互換性があります。)デフォルトでは、HDL Verifier ソフトウェアは、HDL モジュールとそのシミュレーション関数が同じ名前を共有していると想定します。matlabtb でテストベンチ関数呼び出しをバインドするを参照してください。

MATLAB 関数の命名ガイドラインの詳細については、MATLAB ドキュメントのファイルとファイル名に関する「MATLAB プログラミングのヒント」を参照してください。

テストベンチで使用するために HDL モジュールでポート方向モードを指定する

モジュール ステートメントでは、各ポートの方向モード (入力、出力、または双方向) を指定する必要があります。次の表では、これら 3 つのモードを定義します。

| VHDL モードを使用します... | Verilog モードを使用します... | ポートの場合... |

|---|---|---|

IN | input | MATLAB関数またはSimulink®テストベンチで駆動できる信号を表す |

OUT | output | MATLAB関数またはSimulinkテストベンチに渡される信号値を表す |

INOUT | inout | MATLAB関数またはSimulinkテストベンチによって駆動されるか、または値を渡せる双方向信号を表します。 |

テストベンチで使用するために HDL モジュールでポート データ型を指定する

このセクションでは、HDL モジュールのポートに MATLAB と互換性のあるデータ型を指定する方法について説明します。HDL Verifier インターフェイスが MATLAB 環境のデータ型を変換する方法の詳細については、サポートされているデータ型 を参照してください。

メモ

サポートされていないタイプを使用すると、HDL Verifier ソフトウェアは警告を発し、実行時にポートを無視します。たとえば、実行時に 5 つのポートを持つインターフェイスを定義し、そのうちの 1 つが VHDL アクセス ポートである場合、インターフェイスは警告を表示し、コードでは 4 つのポートのみを認識します。

VHDL エンティティのポート データ型. エンティティ ステートメントでは、MATLAB を使用してテストする予定の各ポートを、HDL Verifier ソフトウェアでサポートされている VHDL データ型で定義する必要があります。インターフェイスは、次の VHDL 型のスカラーおよび配列データを同等の MATLAB 型に変換できます。

STD_LOGIC、STD_ULOGIC、BIT、STD_LOGIC_VECTOR、STD_ULOGIC_VECTOR、およびBIT_VECTORINTEGERおよびNATURALREALTIME列挙型(ユーザー定義の列挙型と

CHARACTERを含む)

このインターフェースは、前述の型のすべてのサブタイプと配列もサポートします。

メモ

HDL Verifier ソフトウェアは、次のコンポーネントの VHDL 拡張識別子をサポートしていません。

協調シミュレーションで使用されるポートと信号名

コシミュレーションで使用されるポート名と信号名の配列インデックスとして使用される列挙リテラル

ただし、ソフトウェアは VHDL の基本識別子をサポートしています。

Verilog モジュールのポート データ型. モジュール定義では、MATLAB でテストする予定の各ポートを、HDL Verifier ソフトウェアでサポートされている Verilog ポート データ型で定義する必要があります。インターフェースは、次の Verilog ポート タイプのデータを同等の MATLAB タイプに変換できます。

登録

整数

ワイヤー

メモ

HDL Verifier ソフトウェアは、コシミュレーションで使用されるポート名と信号名の Verilog エスケープ識別子をサポートしていません。ただし、Verilog の単純な識別子はサポートされています。

テストベンチで使用するために HDL 設計をコンパイルして詳細化する

HDL ソース ファイルを作成または編集した後、HDL シミュレータ コンパイラを使用してコードをコンパイルおよびデバッグします。

その他の例については、HDL Verifier のチュートリアルとデモを参照してください。HDL コンパイラの使用の詳細については、シミュレータのドキュメントを参照してください。

サンプル VHDL エンティティ定義

このサンプル VHDL コード フラグメントは、エンティティ decoder を定義します。デフォルトでは、エンティティは MATLAB テストベンチ関数 decoder に関連付けられています。

キーワード PORT は、エンティティのポート句の開始を示します。この句は、2 つの IN ポート (isum と qsum) と 3 つの OUT ポート (adj、dvalid、および odata) を定義します。出力ポートは、処理のために MATLAB 機能入力ポートに信号を駆動します。入力ポートは、MATLAB 関数の出力ポートから信号を受信します。

両方の入力ポートは、5 つの標準ロジック値で構成されるベクトルとして定義されます。出力ポート adj も標準ロジック ベクトルとして定義されていますが、2 つの値のみで構成されます。出力ポート dvalid と odata は、スカラー標準ロジック ポートとして定義されます。HDL Verifier インターフェイスが標準ロジック スカラーおよび配列型のデータを MATLAB 環境で使用できるように変換する方法については、サポートされているデータ型 を参照してください。

ENTITY decoder IS PORT ( isum : IN std_logic_vector(4 DOWNTO 0); qsum : IN std_logic_vector(4 DOWNTO 0); adj : OUT std_logic_vector(1 DOWNTO 0); dvalid : OUT std_logic; odata : OUT std_logic); END decoder ;

テストベンチ関数を書く

MATLAB コシミュレーション関数のコーディング

HDL モジュールまたはコンポーネントを検証するための MATLAB 関数をコーディングするには、特定のコーディング規則に従う必要があります。また、発生するデータ型変換を理解し、データを操作して HDL シミュレータにデータを返すためのデータ型変換をプログラムする必要もあります。

HDL モジュールまたはコンポーネントを検証するための MATLAB 関数をコーディングするには、次の手順を実行します。

MATLAB HDL Verifier テストベンチ関数の構文を学習します。テストベンチ関数の構文を参照してください。

HDL Verifier ソフトウェアが HDL シミュレータからのデータを MATLAB 環境で使用できるように変換する方法を理解します。サポートされているデータ型を参照してください。

MATLAB 関数の名前を選択します。HDL モジュール コンポーネントを MATLAB テスト ベンチ関数にバインドするを参照してください。

関数定義行で期待されるパラメータを定義します。MATLAB 関数の構文と関数の引数の定義を参照してください。

関数に渡されるポート データの種類を決定します。MATLAB 関数の構文と関数の引数の定義を参照してください。

portinfo構造で受信した情報を抽出し、シミュレーションに適用できる場合は適用します。ポート情報へのアクセスと適用を参照してください。必要に応じて、MATLAB 環境で操作できるようにデータを変換します。HDL データを変換して MATLAB または Simulink に送信するを参照してください。

HDL シミュレータに返す必要があるデータを変換します。HDLシミュレータに戻すためのデータの変換を参照してください。

その他のヒントについては、テストベンチとコンポーネント機能の記述 を参照してください。

テストベンチ関数の構文

MATLABテストベンチ関数の構文は

function [iport, tnext] = MyFunctionName(oport, tnow, portinfo)

各関数の引数の説明については、MATLAB 関数の構文と関数の引数の定義 を参照してください。

サンプル MATLAB テストベンチ関数

このセクションでは、サンプルの MATLAB 関数を使用して、HDL Verifier ソフトウェアに必要な MATLAB テスト ベンチ関数のセクションを識別します。このサンプルで使用されているコードの全文は、セクション MATLAB Builder EX 関数例: manchester_decoder.m で確認できます。

MATLAB Builder™ EX テストベンチ関数をコーディングするための最初のステップとして、VHDL エンティティでモデル化されたデータが MATLAB Builder EX 環境のデータにどのようにマップされるかを理解する必要があります。VHDL エンティティ decoder は次のように定義されます。

ENTITY decoder IS PORT ( isum : IN std_logic_vector(4 DOWNTO 0); qsum : IN std_logic_vector(4 DOWNTO 0); adj : OUT std_logic_vector(1 DOWNTO 0); dvalid : OUT std_logic; odata : OUT std_logic ); END decoder ;

次の説明では、manchester_decoder MATLAB Builder EX 関数の定義における重要なコード行に焦点を当てています。

MATLAB 関数名と必要なパラメータを指定します。

次のコードは、

manchester_decoderMATLAB Builder EX 関数の関数宣言です。function [iport,tnext] = manchester_decoder(oport,tnow,portinfo)

MATLAB 関数の構文と関数の引数の定義を参照してください。

関数宣言は次のアクションを実行します。

関数に名前を付けます。この宣言では関数に

manchester_decoderという名前を付けていますが、これはエンティティ名decoderとは異なります。名前が異なるため、後でエンティティをmatlabtbまたはmatlabtbeval関数で検証用に初期化するときに、関数名を明示的に指定する必要があります。HDL モジュール コンポーネントを MATLAB テスト ベンチ関数にバインドするを参照してください。必要な引数と戻りパラメータを定義します。MATLAB Builder EX テストベンチ関数は、2 つのパラメータ

iportとtnextを返し、3 つの引数oport、tnow、portinfoを渡し、示されている順序で出現する 必要があります。MATLAB 関数の構文と関数の引数の定義を参照してください。次のコード例のように、関数の出力は空の値に初期化する必要があります。

tnext = []; iport = struct();

推奨されるベスト プラクティスに従うには、関数の先頭で関数出力を初期化する必要があります。

次の図は、エンティティのポートと MATLAB Builder EX 関数の

iportおよびoportパラメータの関係を示しています。

必要な MATLAB Builder EX テストベンチ関数パラメータの詳細については、「MATLAB 関数の構文と関数の引数の定義」を参照してください。

シミュレート対象のエンティティに対して定義されているポートのデータ型をメモします。

HDL Verifier ソフトウェアは、HDL データ型を同等の MATLAB Builder EX データ型に変換し、その逆も行います。MATLAB Builder EX 関数を開発する際には、HDL シミュレータから受信し、HDL シミュレータに返す必要があるデータのタイプを知っておく必要があります。

この例で定義されているVHDLエンティティは次のポートで構成されています

VHDL ポート定義の例

ポート 方向 タイプ... ...に変換されます/...への変換が必要です isumINSTD_LOGIC_VECTOR(4 DOWNTO 0)各ビットが標準の論理文字リテラルにマップされる 5 ビットの列または行の文字ベクトル。 qsumINSTD_LOGIC_VECTOR(4 DOWNTO 0)各ビットが標準の論理文字リテラルにマップされる 5 ビットの列または行の文字ベクトル。 adjOUTSTD_LOGIC_VECTOR(1 DOWNTO 0)文字の 2 要素の列ベクトル。各文字は、論理状態を表し、単一のビットにマップされる対応する文字リテラルと一致します。 dvalidOUTSTD_LOGIC論理状態を表す文字リテラルに一致する文字。 odataOUTSTD_LOGIC論理状態を表す文字リテラルに一致する文字。 インターフェイス データ型変換の詳細については、「サポートされているデータ型」を参照してください。

必要なタイミング パラメータを設定します。

tnext割り当てステートメントは、シミュレータがナノ秒ごとに MATLAB Builder EX 関数をコールバックするようにタイミング パラメーターtnextを設定します。tnext = tnow+1e-9;

出力ポートのデータを処理のために MATLAB データ型に変換します。

次のコード抜粋は、出力ポート データのデータ型変換を示しています。

%% Compute one row and plot isum = isum + 1; adj(isum) = mvl2dec(oport.adj'); data(isum) = mvl2dec([oport.dvalid oport.odata]); . . .

mvl2decへの 2 つの呼び出しは、MATLAB Builder EX 関数がエンティティの出力ポートadj、dvalid、およびodataから受信したバイナリ データを、MATLAB Builder EX が計算できる符号なし 10 進数値に変換します。この関数は、2 ビットの転置ベクトルoport.adjを 0 ~ 4 の範囲の 10 進数値に変換し、oport.dvalidとoport.odataを 10 進数値 0 または 1 に変換します。MATLAB 関数の構文と関数の引数の定義 は、シミュレーション MATLAB 関数をコーディングするときに考慮すべきデータ変換の種類の概要を示します。

HDL シミュレータに返されるデータを変換します。

次のコード抜粋は、HDL シミュレータに返されるデータのデータ型変換を示しています。

if isum == 17 iport.isum = dec2mvl(isum,5); iport.qsum = dec2mvl(qsum,5); else iport.isum = dec2mvl(isum,5); end

dec2mvlへの 3 回の呼び出しは、MATLAB Builder EX によって計算された 10 進数値を、MATLAB Builder EX 関数がエンティティの入力ポートisumおよびqsumに格納できるバイナリ データに変換します。いずれの場合も、関数は 10 進数値を 5 要素のビット ベクトルに変換します。各ビットは、論理状態を表す文字リテラルにマップされる文字を表します。HDLシミュレータに戻すためのデータの変換 は、HDL シミュレータにデータを返すときに考慮すべきデータ変換の種類の概要を示します。

MATLAB Builder EX 関数例: manchester_decoder.m

function [iport,tnext] = manchester_decoder(oport,tnow,portinfo) % MANCHESTER_DECODER Test bench for VHDL 'decoder' % [IPORT,TNEXT]=MANCHESTER_DECODER(OPORT,TNOW,PORTINFO) - % Implements a test of the VHDL decoder entity which is part % of the Manchester receiver demo. This test bench plots % the IQ mapping produced by the decoder. % % iport oport % +-----------+ % isum -(5)->| |-(2)-> adj % qsum -(5)->| decoder |-(1)-> dvalid % | |-(1)-> odata % +-----------+ % % isum - Inphase Convolution value % qsum - Quadrature Convolution value % adj - Clock adjustment ('01','00','10') % dvalid - Data validity ('1' = data is valid) % odata - Recovered data stream % % Adjust = 0 (00b), generate full 16 cycle waveform % Copyright 2003-2009 The MathWorks, Inc. persistent isum; persistent qsum; %persistent ga; persistent x; persistent y; persistent adj; persistent data; global testisdone; % This useful feature allows you to manually % reset the plot by simply typing: >manchester_decoder tnext = []; iport = struct(); if nargin == 0, isum = []; return; end if exist('portinfo') == 1 isum = []; end tnext = tnow+1e-9; if isempty(isum), %% First call scale = 9; isum = 0; qsum = 0; for k=1:2, ga(k) = subplot(2,1,k); axis([-1 17 -1 17]); ylabel('Quadrature'); line([0 16],[8 8],'Color','r','LineStyle',':','LineWidth',1) line([8 8],[0 16],'Color','r','LineStyle',':','LineWidth',1) end xlabel('Inphase'); subplot(2,1,1); title('Clock Adjustment (adj)'); subplot(2,1,2); title('Data with Validity'); iport.isum = '00000'; iport.qsum = '00000'; return; end % compute one row, then plot isum = isum + 1; adj(isum) = bin2dec(oport.adj'); data(isum) = bin2dec([oport.dvalid oport.odata]); if isum == 17, subplot(2,1,1); for k=0:16, if adj(k+1) == 0, % Bang on! line(k,qsum,'color','k','Marker','o'); elseif adj(k+1) == 1, % line(k,qsum,'color','r','Marker','<'); else line(k,qsum,'color','b','Marker','>'); end end subplot(2,1,2); for k=0:16, if data(k+1) < 2, % Invalid line(k,qsum,'color','r','Marker','X'); else if data(k+1) == 2, %Valid and 0! line(k,qsum,'color','g','Marker','o'); else line(k,qsum,'color','k','Marker','.'); end end end isum = 0; qsum = qsum + 1; if qsum == 17, qsum = 0; disp('done'); tnext = []; % suspend callbacks testisdone = 1; return; end iport.isum = dec2bin(isum,5); iport.qsum = dec2bin(qsum,5); else iport.isum = dec2bin(isum,5); end