新規 FPGA ボード ウィザード

新規 FPGA ボード ウィザードを使用すると、ボードを FPGA ボードのリストに追加するために必要な情報をすべて入力できます。このリストは FPGA インザループ (FIL) ワークフローに適用されます。FPGA ボードを追加する前に、FPGA ボードの要件を確認して、使用するワークフローに適合していることを確認してください。

新規 FPGA ボード ウィザードには、ナビゲーション用のボタンが複数あります。

Back: 入力済みのデータの確認や編集のために、前のページに戻ります。

Next: 現在のページで必要なすべての情報を入力したら、次のページに進みます。

Help: Doc Center を開き、このトピックを表示します。

Cancel: 新規 FPGA ボード ウィザードを終了します。終了時にセッションで入力した情報を保存するかしないかを選択できます。

ボードを一度に複数のユーザーに追加

新規のボードをグローバルに追加するには、以下の手順に従ってください。グローバルに追加されたボードにアクセスするには、すべてのユーザーが同じ MATLAB® インストールを使用していなければなりません。

以下のようなフォルダーを作成します。

matlabroot/toolbox/shared/eda/board/boardfilesボード記述 XML ファイルを

boardfilesフォルダーにコピーします。XML ファイルをコピーした後、MATLAB を再起動します。FIL ワークフローの FPGA ボードのリストに新規のボードが表示されます。

同じ MATLAB インストールを使用するユーザーに対して、このフォルダーにあるすべてのボードが自動的に FPGA ボードのリストに表示されます。FPGA ボード マネージャーを使用してこれらのボードを追加しなおす必要はありません。

FPGA ボードを追加するためのワークフローの手順は以下のとおりです。

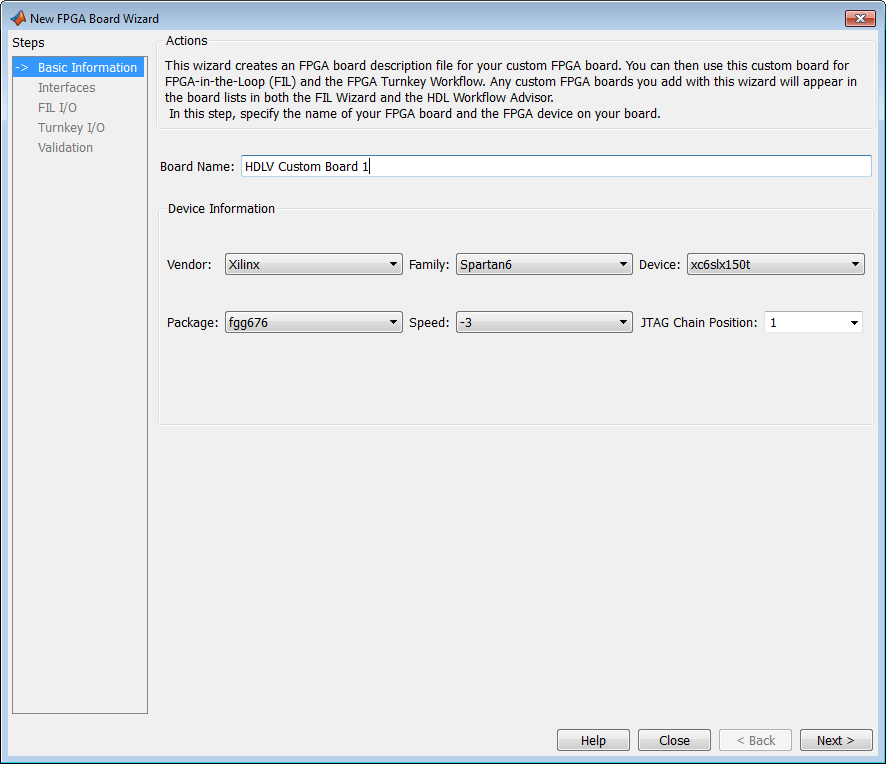

Basic Information

Board Name: 一意のボード名を入力します。

Device Information:

Vendor:

AMDまたはAlteraFamily: ファミリは指定したベンダーによって異なります。適用できる設定についてはボード仕様ファイルを参照してください。

Device: ボード仕様ファイルを使用して正しいデバイスを選択します。

AMD® ボードの場合のみ:

Package: ボード仕様ファイルを使用して正しいパッケージを選択します。

Speed: ボード仕様ファイルを使用して正しい速度を選択します。

JTAG Chain Position: 値は JTAG チェーンの開始位置を表します。この情報についてはボード仕様ファイルを参照してください。

Interfaces

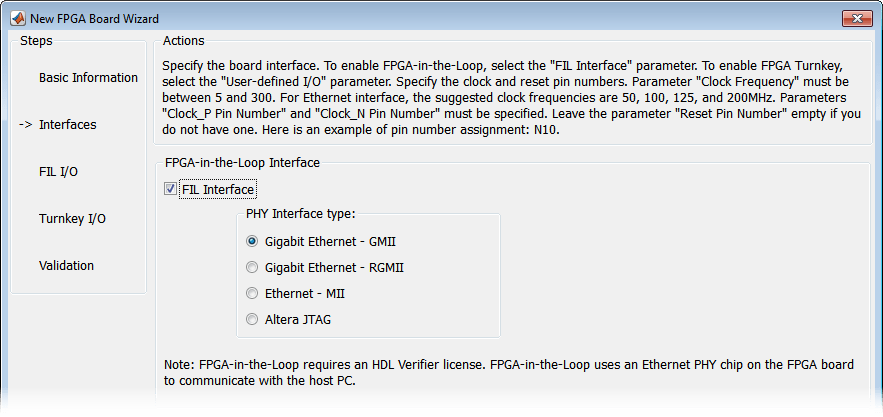

Altera ボードの FIL Interface

FPGA インザループ: このボードを FIL で使用する場合、[FIL Interface] を選択します。

次のいずれかの [PHY Interface type] を選択します。

Gigabit Ethernet — GMII

Gigabit Ethernet — RGMII (Altera® ボードのみ)

Gigabit Ethernet — SGMII (オプション SGMII は、Stratix® V または Stratix IV デバイス ファミリからボードを選択している場合に表示されます)

Ethernet — MII

Altera JTAG (Altera ボードのみ)

メモ

すべてのインターフェイスがすべてのボードに対して使用可能であるわけではありません。使用できるかどうかは、[Basic Information] で選択したボードによって異なります。

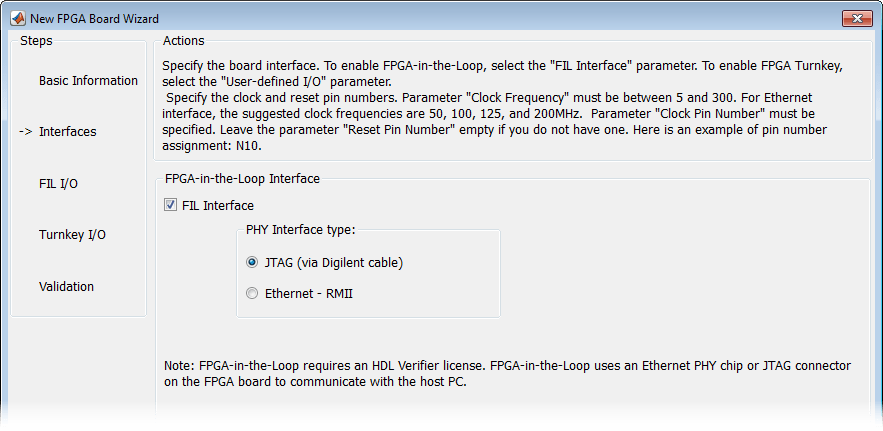

AMD ボードの FIL Interface

FPGA-in-the-Loop Interface: このボードを FIL で使用する場合、[FIL Interface] を選択します。

次のいずれかの [PHY Interface type] を選択します。

JTAG (via Digilent cable) (AMD ボードのみ)

Ethernet — RMII

メモ

すべてのインターフェイスがすべてのボードに対して使用可能であるわけではありません。使用できるかどうかは、[Basic Information] で選択したボードによって異なります。

AMD ボードへの JTAG 接続の設定方法については、Digilent ケーブル設定による JTAGを参照してください。

制限. Digilent® JTAG ケーブルを使用して FPGA 設計をシミュレートする場合、Vivado® Logic Analyzer などの JTAG へのアクセスを必要とするどのデバッグ機能も使用できません。

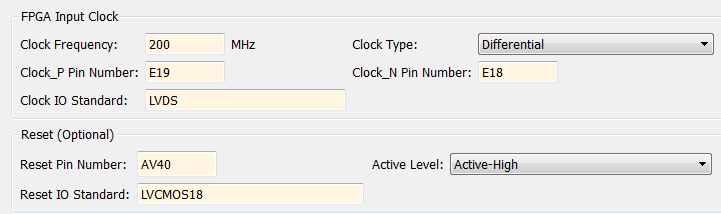

FPGA Input Clock および Reset

FPGA Input Clock — クロックの詳細はどちらのワークフローでも必要です。必要な情報はいずれもボード仕様ファイルから取得できます。

Clock Frequency — は 5 ~ 300 でなければなりません。イーサネット インターフェイスの場合、推奨されるクロック周波数は、50、100、125 および 200 MHz です。

Clock Type —

Single_EndedまたはDifferentialClock Pin Number (Single_Ended) — 必ず指定しなければなりません。例:

N10Clock_P Pin Number (Differential) — 必ず指定しなければなりません。例:

E19Clock_N Pin Number (Differential) — 必ず指定しなければなりません。例:

E18Clock IO Standard — 入力端子、出力端子または双方向端子の設定に使用するプログラミング可能な I/O 標準。例:

LVDS

Reset (Optional) — リセットを指定するには、ボード仕様ファイルでピン番号とアクティブ レベルを確認し、その情報を入力します。

Reset Pin Number — ない場合は空白のままにします。

Active Level —

Active-LowまたはActive-High。Reset IO Standard — 入力端子、出力端子または双方向端子の設定に使用するプログラミング可能な I/O 標準。例:

LVCMOS33

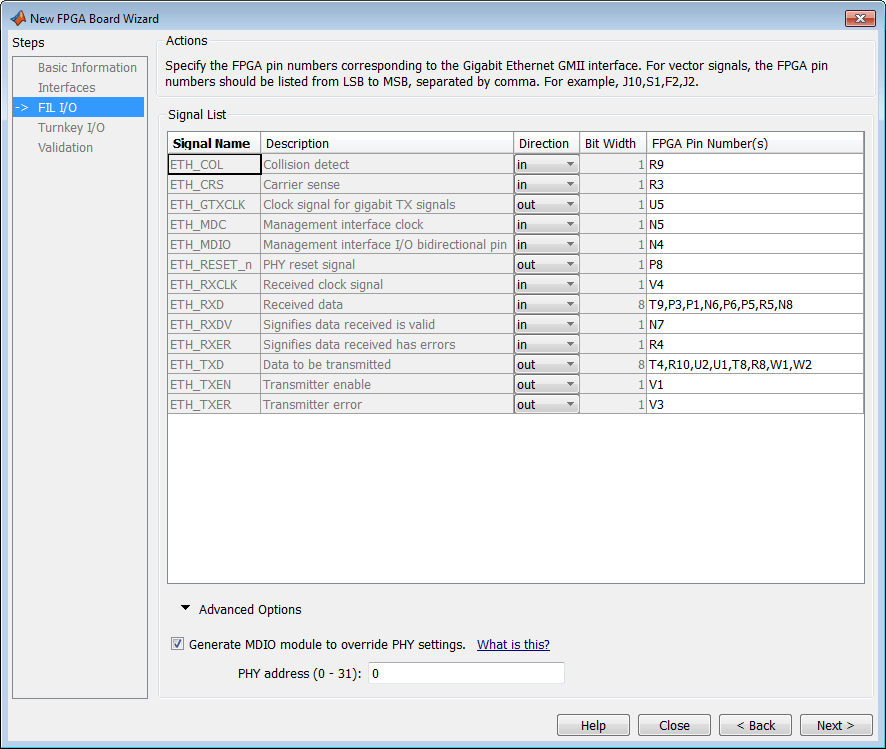

FIL I/O

ボードへのイーサネット接続を選択する場合、FPGA 上のイーサネット信号用のピンを指定しなければなりません。

Signal List: 指定した信号のすべての FPGA ピン番号を入力します。この情報はボード仕様ファイルから取得できます。ベクトル信号の場合、同じ線上のすべてのピン番号をコンマ区切りで入力します。

メモ

PHY チップにオプションの TX_ER ピンがない場合、ETH_TXER を FPGA 上の未使用のピンのいずれかに関連付けます。

Generate MDIO module to override PHY settings: この機能をどの時点で使用するかについては、この次の FPGA ボード管理データ入出力バス (MDIO) に関する節を参照してください。このオプションを選択する場合は、PHY アドレスを入力します。

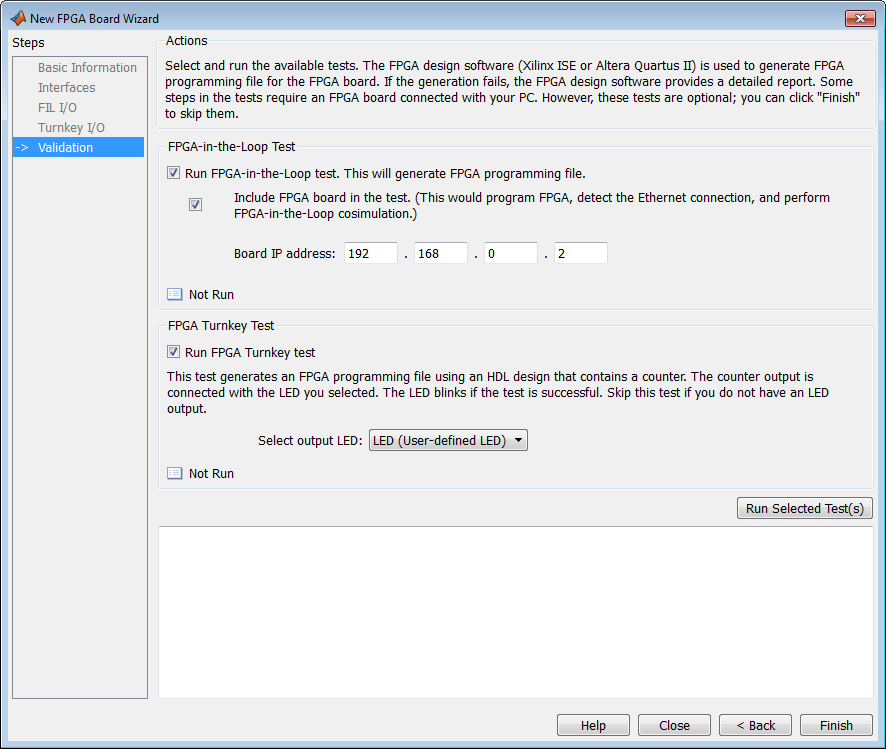

Validation

FPGA-in-the-Loop Test

Run FPGA-in-the-Loop test: 選択すると、FPGA プログラミング ファイルを生成します。

Include FPGA board in the test: (オプション) 選択すると、生成されたプログラミング ファイルで FPGA がプログラムされ、イーサネット接続が (選択されている場合) 検出され、FPGA インザループ シミュレーションが実行されます。

ボード IP アドレス: (イーサネット接続の場合のみ) このオプションは、ボードの IP アドレスが既定のアドレス (192.168.0.2) でない場合に、IP アドレスを設定するのに使用します。

ネットワーク アダプターを設定する際、必要に応じて使用しているコンピューターの IP アドレスを、192.168.0.x 以外のサブネットに変更します。ボードの既定 IP アドレス 192.168.0.2 を別のデバイスが使用している場合は、ボードの IP アドレスを以下のガイドラインに従って変更します。

サブネット アドレスは、通常、ボードの IP アドレスの最初の 3 バイトですが、これがホスト IP アドレスと一致していなければなりません。

ボードの IP アドレスの最終バイトは、ホスト IP アドレスと異なっていなければなりません。

ボードの IP アドレスは、他のコンピューターの IP アドレスと競合しないものを使用しなければなりません。

たとえば、ホスト IP アドレスが 192.168.8.2 の場合、192.168.8.3 が使用可能であれば、使用できます。

Finish

検証が完了したら、[Finish] をクリックします。ボード定義ファイルの保存を参照してください。