AMD KC705 評価ボード定義ファイルの作成

概要

FPGA インザループに対して、MathWorks® が提供する事前登録済み FPGA ボードのリストにない独自の FPGA ボードを使用することができます。新規 FPGA ボード ウィザードを使用すると、カスタム FPGA ボードを記述するボード定義ファイルを作成できます。

次の例は、FIL シミュレーションで使用する AMD® KC705 評価ボードのボード定義ファイルを作成するワークフローです。

はじめる前に

ボード仕様を確認して、次の情報をすぐに用意できるようにします。

イーサネット PHY チップへの FPGA インターフェイス

クロック ピンの名前と番号

リセット ピンの名前と番号

この例では、必要な情報は既に提供されています。一般的には、これらの情報はボード仕様ファイルで確認することができます。この例では、KC705 Evaluation Board for the Kintex-7 FPGA User Guide (AMD 発行) を使用しています。

検証を実行するには、AMD または Altera® がパスになければなりません。関数

hdlsetuptoolpathを使用して、このツールを MATLAB® で使用できるように設定します。定義ファイルを追加した後に FPGA ボードのプログラミングを検証するには、カスタム ボードをコンピューターに接続します。ただし、ボード定義ファイルを作成する時点では、ボードを接続する必要はありません。

新規 FPGA ボード ウィザードの起動

MATLAB プロンプトで以下のコマンドを入力し、FPGA ボード マネージャーを起動します。

fpgaBoardManager

[カスタム ボードの作成] をクリックして新規 FPGA ボード ウィザードを開きます。

ボードの基本情報の入力

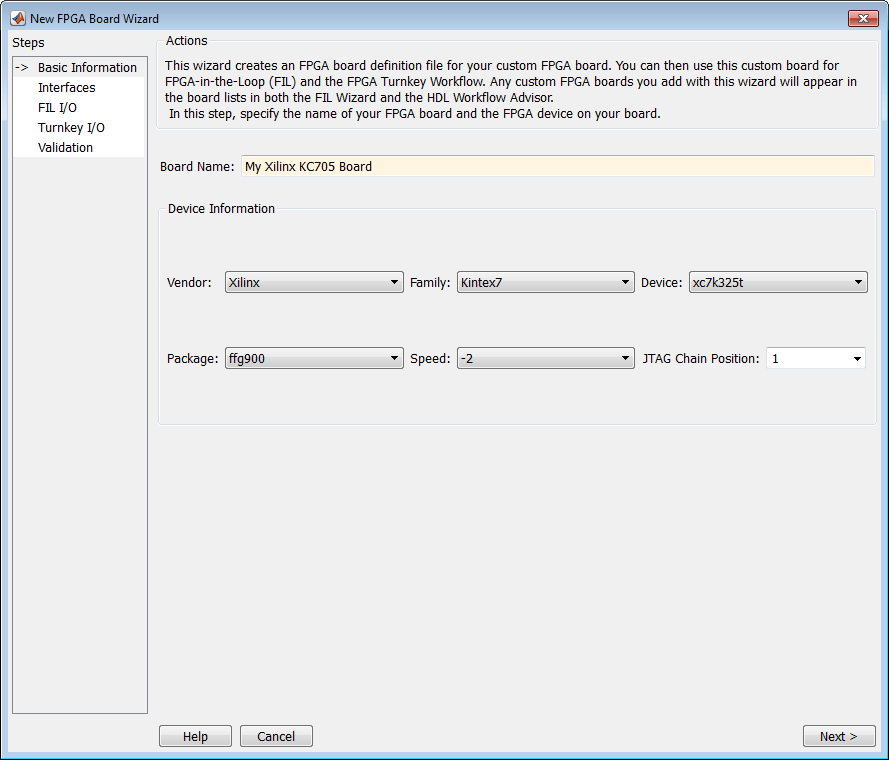

[Basic Information] ペインで、以下の情報を入力します。

Board Name: 「My AMD KC705 Board」と入力します。

Vendor:

[AMD]を選択します。Family:

[Kintex7]を選択します。Device:

[xc7k325t]を選択します。Package:

[ffg900]を選択します。Speed:

[-2]を選択します。JTAG Chain Position:

[1]を選択します。

ここで入力した情報は KC705 Evaluation Board for the Kintex-7 FPGA User Guide に記載されています。

[Next] をクリックします。

FPGA インターフェイス情報の指定

[Interfaces] ペインで、以下の操作を実行します。

[FIL Interface] を選択します。このオプションは、ボードを FPGA インザループで使用する場合に必要です。

[PHY Interface Type] で [GMII] を選択します。このオプションは、オンボード FPGA が GMII インターフェイス経由でイーサネット PHY チップに接続していることを表します。

Clock Frequency: 「200」と入力します。この AMD KC705 ボードには複数のクロック ソースがあります。200 MHz クロックは、イーサネット インターフェイスで使用する場合に推奨されるクロック周波数 (50、100、125、200 MHz) のひとつです。

Clock Type:

[Differential]を選択します。Clock_P Pin Number:「AD12」と入力します。

Clock_N Pin Number: 「AD11」と入力します。

Clock IO Standard — 空白のままにします。

Reset Pin Number: 「AB7」と入力します。この値により FPGA に対するグローバル リセットが設定されます。

Active Level:

[Active-High]を選択します。Reset IO Standard — 空白のままにします。

必要な情報はいずれもボード設計仕様から取得できます。

[Next] をクリックします。

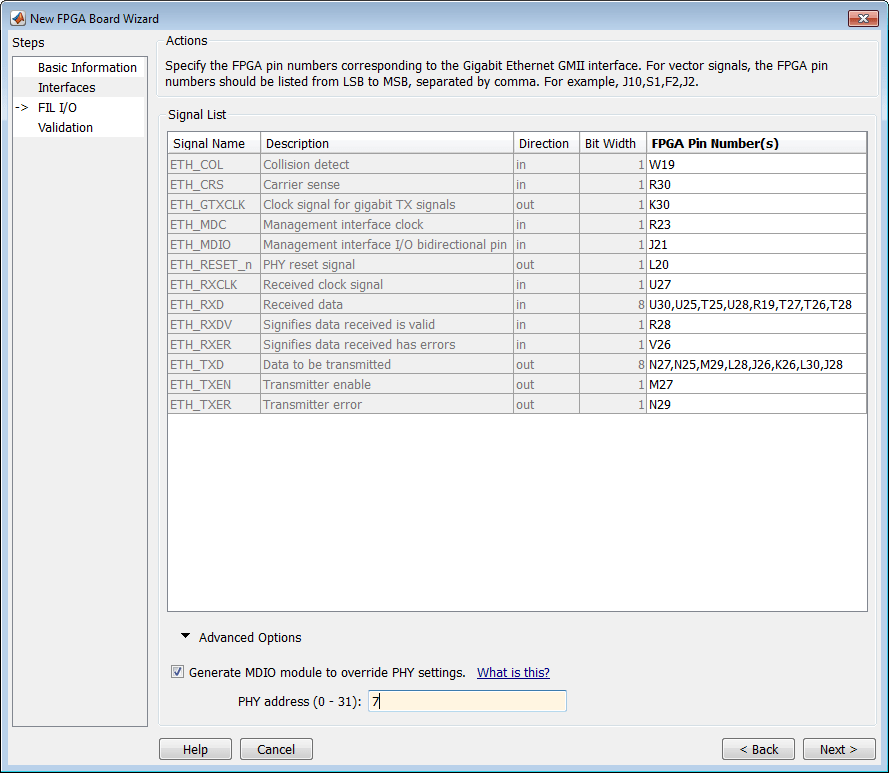

FPGA ピン番号の入力

[FIL I/O] ペインで、各 FPGA ピンの番号を入力します。この情報は必須です。

RXD 信号と TXD 信号のピン番号は、LSD (最下位桁) から順に MSD (最上位桁) までコンマ区切りで入力されます。

信号名 入力する FPGA ピン番号 ETH_COL W19 ETH_CRS R30 ETH_GTXCLK K30 ETH_MDC R23 ETH_MDIO J21 ETH_RESET_n L20 ETH_RXCLK U27 ETH_RXD U30,U25,T25,U28,R19,T27,T26,T28 ETH_RXDV R28 ETH_RXER V26 ETH_TXD N27,N25,M29,L28,J26,K26,L30,J28 ETH_TXEN M27 ETH_TXER N29 [Advanced Options] をクリックしてセクションを展開します。

[Generate MDIO module to override PHY settings] オプションをオンにします。

このオプションを選択する理由は以下のとおりです。

AMD KC705 ボードには、イーサネット PHY デバイスを MII、GMII、RGMII または SGMII モードに設定するジャンパーがあります。この例では GMII インターフェイスを使用しているため、PHY デバイスのモードが誤って設定されていると FPGA ボードが機能しません。[Generate MDIO module to override PHY settings] オプションがオンになっている場合、FPGA は MDIO (Management Data Input/Output) バスを使用してジャンパー設定をオーバーライドし、PHY チップを正しい GMII モードに設定します。

現在、このオプションは Marvell Alaska PHY デバイス 88E1111 に対してのみ適用されます。この KC705 ボードは Marvel デバイスを使用しています。

PHY address (0 – 31): 「7」と入力します。

[Next] をクリックします。

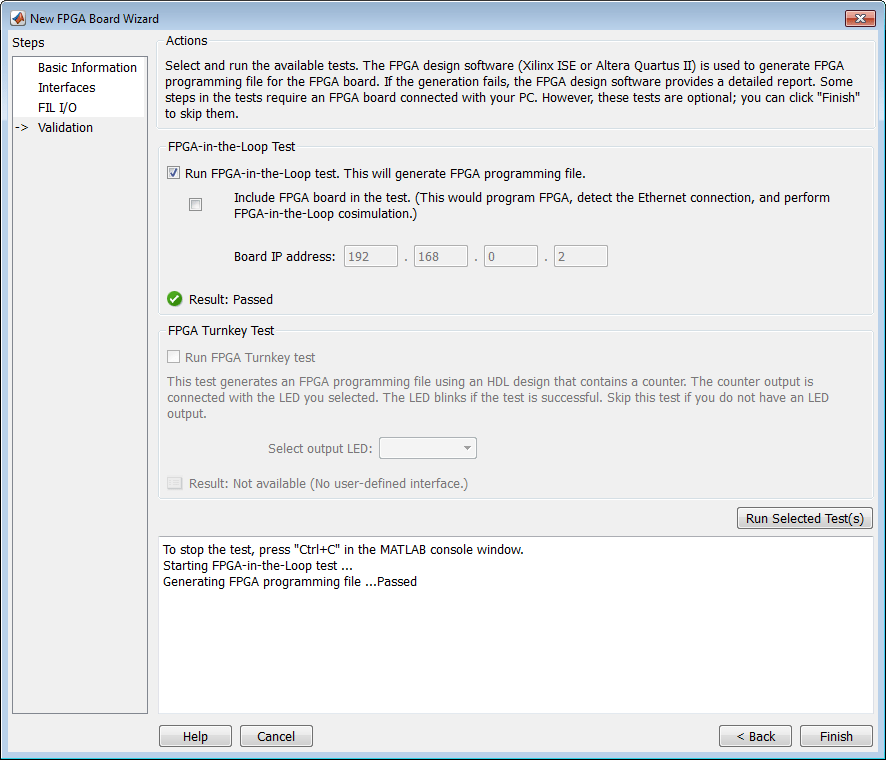

オプションの検証テストの実行

この手順では検証テストを実行します。ここでは、FPGA インザループ コシミュレーションを実行して、入力された情報が正しいかどうかを検証します。同じコンピューターに AMD ISE 13.4 以降のバージョンがインストールされている必要があります。この手順はオプションで、省略することも可能です。

メモ

検証を実行するには、AMD または Altera がパスになければなりません。関数 hdlsetuptoolpath を使用して、このツールを MATLAB で使用できるように設定します。

このテストを実行するには、以下の操作を実行します。

[Run FPGA-in-the-Loop test] オプションをオンにします。

ボードが接続されている場合は、Include FPGA board in the test オプションをオンにします。FPGA ボードの IP アドレスを入力しなければなりません。この例では、AMD KC705 ボードがホスト コンピューターに接続されていて、IP アドレスが 192.168.0.2 であると想定しています。

[Run Selected Test(s)] をクリックします。テストが完了するまで約 10 分かかります。

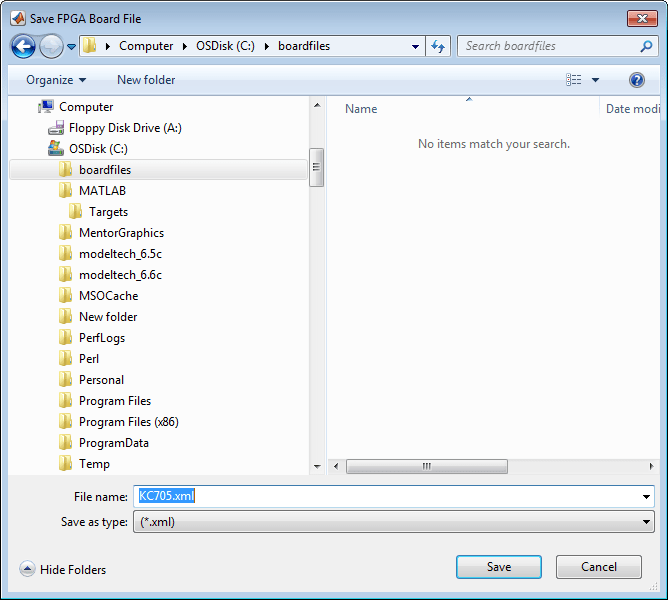

ボード定義ファイルの保存

[終了] をクリックして新規 FPGA ボード ウィザードを終了します。[名前を付けて保存] ダイアログ ボックスが表示され、FPGA ボード定義ファイルの保存場所を指定するよう要求されます。この例では、

C:\boardfiles\KC705.xmlという名前で保存します。

[保存] をクリックしてファイルを保存し、終了します。

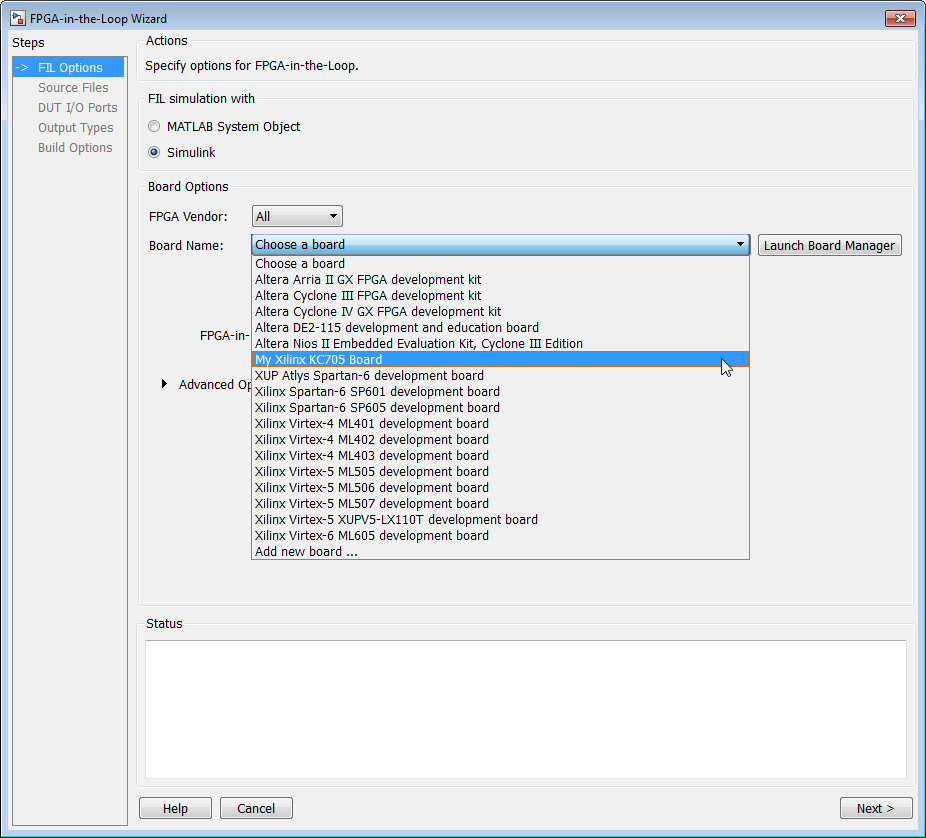

新規の FPGA ボードの使用

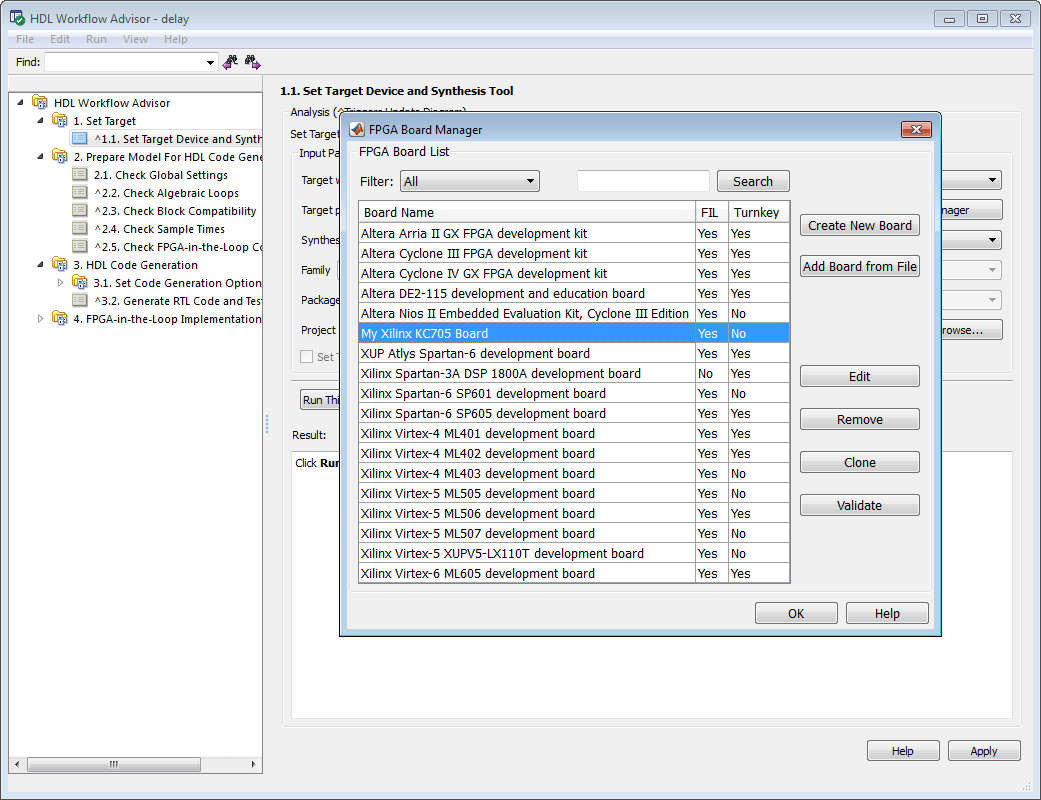

ボード定義ファイルを保存すると、画面が FPGA ボード マネージャーに戻ります。FPGA ボードのリストに、定義した新規のボードが表示されます。

[OK] をクリックして FPGA ボード マネージャーを閉じます。

FIL ウィザードまたは HDL ワークフロー アドバイザーのボードのリストでこの新規のボードが表示されます。

FIL ウィザードは MATLAB プロンプトから起動します。

>>filWizard

AMD KC705 ボードがボードのリストに表示され、FPGA インザループ シミュレーション用に選択できるようになります。

HDL ワークフロー アドバイザーを起動します。

手順 1.1 で

[FPGA インザループ]を選択し、[ボード マネージャーの起動] をクリックします。AMD KC705 ボードがボードのリストに表示され、FPGA インザループ シミュレーション用に選択できるようになります。