このページは前リリースの情報です。該当の英語のページはこのリリースで削除されています。

Microchip PolarFire SoC デバイスの IP コアの生成入門

この例では、ハードウェア ソフトウェア協調設計ワークフローを使用して Microchip PolarFire® SoC Icicle キットにおいてさまざまな周波数で LED を点滅させる方法を示します。

はじめに

この例では、HDL Coder™ を使用して Microchip PolarFire SoC Icicle キットで LED を点滅させるカスタム HDL IP コアを生成する手順について順を追って説明します。

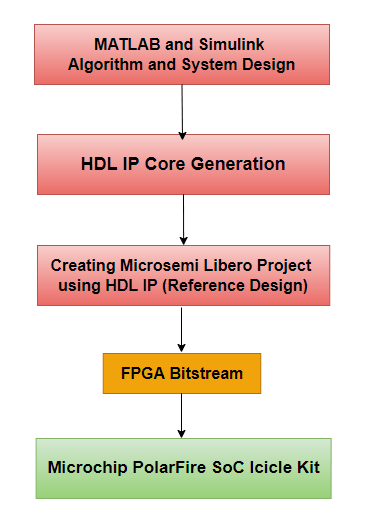

MATLAB® と Simulink® を使用して、アプリケーションの設計、シミュレーション、検証、アルゴリズムを使用した what-if シナリオの実行、パラメーターの最適化を行うことができます。次に、プログラム可能なロジックで実行するシステム要素と、RISC-V プロセッサで実行するシステム要素を決定することで、PolarFire SoC Icicle キットでハードウェア実装とソフトウェア実装用に設計を準備できます。

この例で示されているガイド付きワークフローを使用して、HDL Coder を使用してプログラム可能なロジック用の HDL コードを自動生成し、Microchip PolarFire SoC Icicle キットに設計を実装します。

このワークフローでは、次のタスクを実行します。

PolarFire SoC ハードウェアとツールを設定します。

ハードウェア実装とソフトウェア実装用に設計を分割します。

HDL ワークフロー アドバイザーを使用して HDL IP コアを生成します。

IP コアを Microchip Libero プロジェクトに統合し、PolarFireSoC ハードウェアをプログラムします。

要件

HDL の言語サポートおよびサポートされるサードパーティ製ツールとハードウェアにリストされている、サポートされているバージョンの Microchip Libero Design Suite。

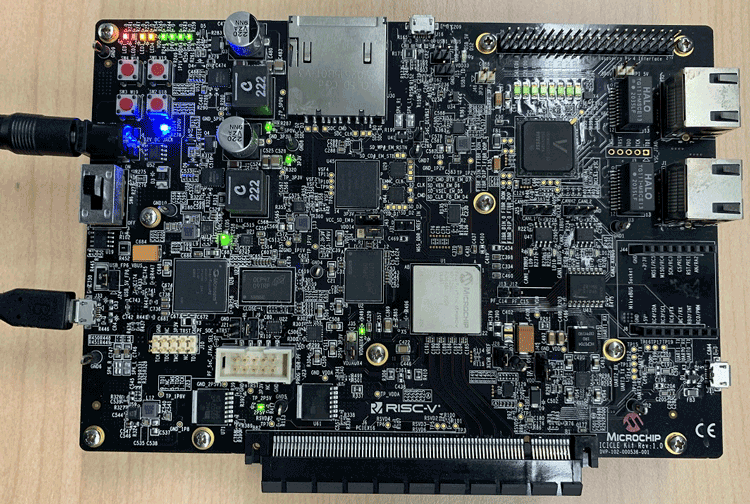

Microchip PolarFire SoC Icicle キット。

HDL Coder Support Package for Microchip FPGA and SoC Devices。

PolarFire SoC ハードウェアとツールの設定

1. 次の図に示されているように、Microchip PolarFire SoC Icicle キットを設定します。PolarFire SoC ハードウェア セットアップの詳細については、PolarFire SoC Icicle キットのクイックスタート カードを参照してください。

マイクロ USB ケーブルを使用してコンピューターを USB UART コネクタに接続します。USB デバイス ドライバー (Silicon Labs CP210x USB to UART Bridge 用のものなど) が正しくインストールされていることを確認します。インストールされていない場合は、ドライバーをオンラインで検索してインストールします。

2. イーサネット ケーブルを使用してコンピューターと PolarFire SoC ボードを接続します。

3. まだインストールしていない場合は、HDL Coder Support Packages for Microchip FPGA and SoC Devices をインストールします。インストーラーを開始するには、MATLAB ツールストリップで [アドオン]、[ハードウェア サポート パッケージの入手] をクリックします。"HDL Coder Support Packages for Microchip FPGA and SoC Devices" を検索してインストールします。

4. MathWorks® が GitHub Web サイトで提供している SD カード イメージを使用していることを確認します。Linux イメージをダウンロードするには、Github をクリックします。

5. この MATLAB コマンド ウィンドウで PolarFire SoC ハードウェア接続を設定します。

6. オプションで、PuTTY™ などのプログラムを使用する構成を使用してシリアル接続をテストできます。ボー レート: 115200、データ ビット: 8、ストップ ビット: 1、パリティ: None、フロー制御: None。PolarFire SoC ボードの電源をオフ/オンすると、シリアル コンソールで Linux® 起動ログを確認できます。

7. MATLAB コマンド ウィンドウでhdlsetuptoolpath関数を使用して Microchip Libero SoC ツール パスを設定します。コマンドを実行するときに独自の Microchip Libero インストール パスを使用します。

hdlsetuptoolpath('ToolName', 'Microchip Libero SoC', 'ToolPath', liberopath);

ハードウェア実装とソフトウェア実装用の設計の分割

PolarFire SoC ハードウェア ソフトウェア協調設計ワークフロー用に、プログラム可能なロジックで実装する設計の部分と RISC-V プロセッサで実行する部分を決定します。

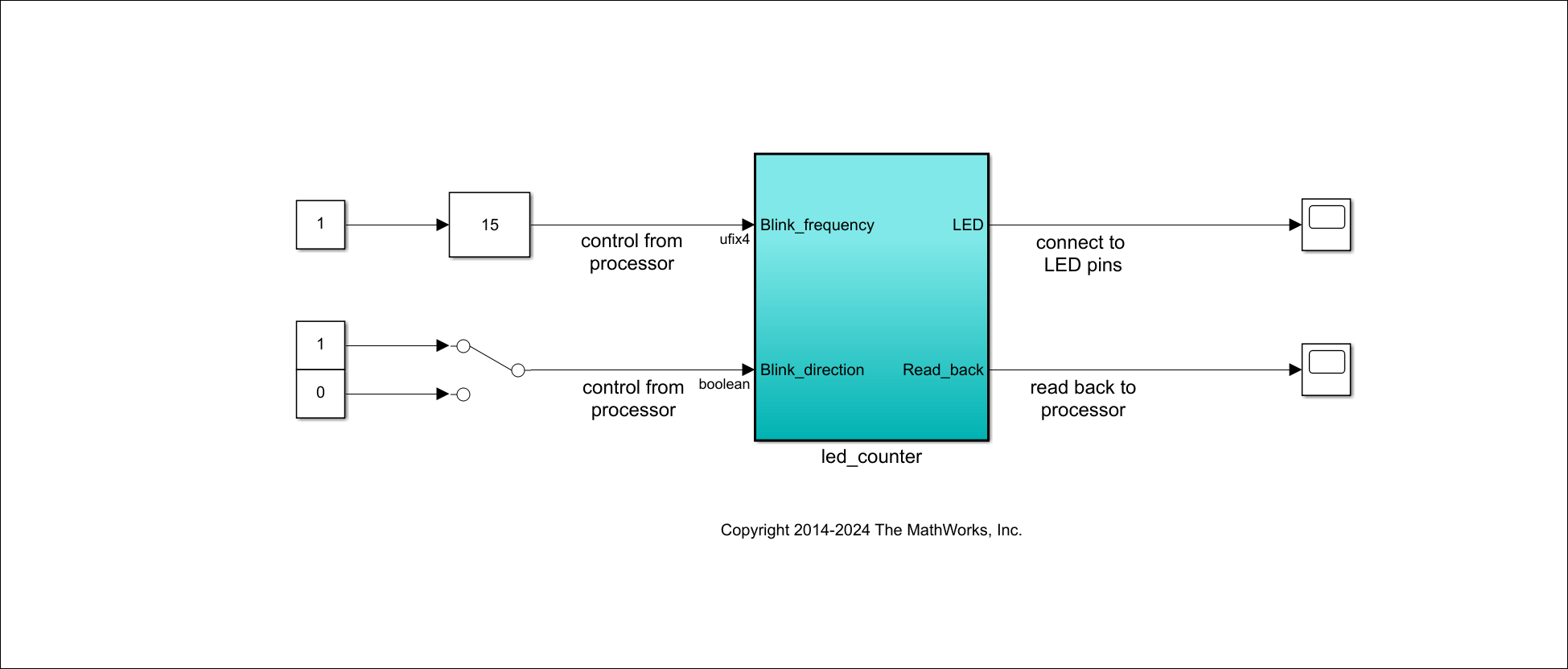

プログラム可能なロジックで実装するすべてのブロックを Atomic サブシステムにグループ化します。この Atomic サブシステムは、ハードウェアとソフトウェアの分割の境界です。このサブシステム内のブロックはプログラム可能なロジックで実装され、このサブシステムの外にあるブロックは RISC-V プロセッサで実行されます。

この例では、サブシステム [led_counter] はハードウェア サブシステムです。これは、FPGA ボード上の LED を点滅させるカウンターをモデル化します。2 つの入力端子 [Blink_frequency] および [Blink_direction] は LED の点滅頻度および方向を決定する制御端子です。サブシステム "led_counter" の外にあるブロックはソフトウェア実装用です。

Simulink で、[Slider Gain] ブロックまたは [Manual Switch] ブロックを使用してハードウェア サブシステムの入力値を調整できます。組み込みソフトウェアでは、これは AXI インターフェイスのアクセス可能なレジスタに書き込むことで、RISC-V プロセッサが生成された IP コアを制御することを意味します。ハードウェア サブシステムの出力ポート [LED] は、LED ハードウェアに接続します。出力端子 "Read_Back" を使用してデータをプロセッサに読み戻すことができます。

open_system('hdlcoder_led_blinking_4bit');

HDL ワークフロー アドバイザーを使用した HDL IP コアの生成

Simulink モデルから共有可能で再利用可能な IP コア モジュールを生成できます。生成された IP コアは FPGA デバイス上の組み込みプロセッサに接続します。HDL Coder で、Simulink ブロックから HDL コードが生成され、IP コアを組み込みプロセッサに接続する AXI インターフェイス ロジック用の HDL コードが生成されます。HDL Coder により、生成されたファイルが IP コア フォルダーにパッケージ化されます。次に、生成された IP コアを Microchip Libero 環境の大規模な FPGA 組み込み設計と統合できます。

IP コアの生成ワークフローを開始します。

1. hdlcoder_led_blinking/led_counter サブシステムから led_counter サブシステムを右クリックして [HDL コード]、[HDL ワークフロー アドバイザー] を選択し、HDL ワークフロー アドバイザーを開きます。

2. [ターゲットを設定]、[ターゲット デバイスおよび合成ツールを設定] タスクの [ターゲット ワークフロー] で [IP Core Generation] を選択します。

3. [ターゲット プラットフォーム] で "Microchip PolarFire SoC Icicle kit" を選択します。このオプションがない場合は、[さらに取得] を選択してサポート パッケージ インストーラーを開きます。

4. [このタスクを実行] をクリックして [ターゲット デバイスおよび合成ツールを設定] タスクを実行します。

5. [ターゲットを設定]、[ターゲットのリファレンス設計を設定] タスクで、[リファレンス設計] として "Default system" が既定で選択されています。

6. [このタスクを実行] をクリックして [ターゲットのリファレンス設計を設定] タスクを実行します。

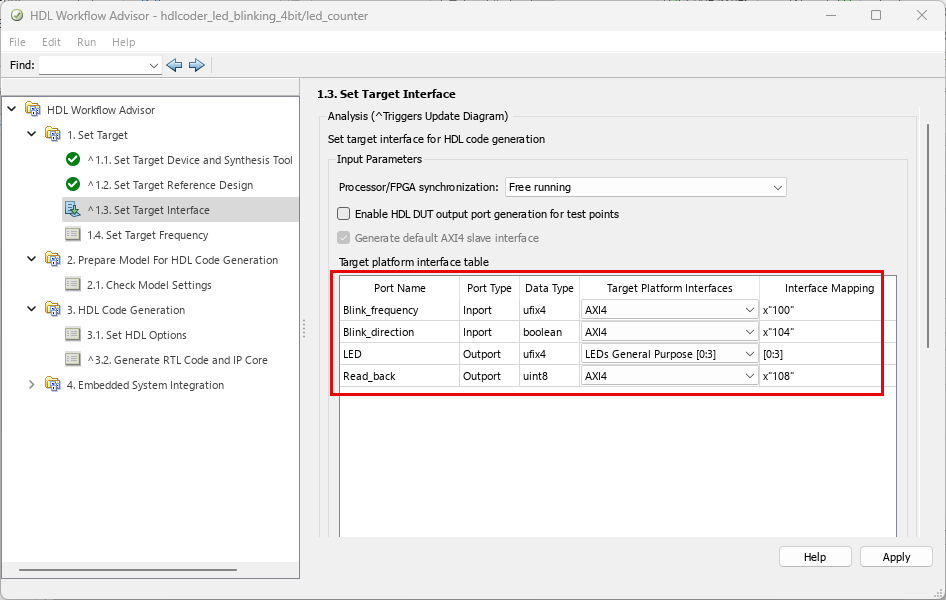

ターゲット インターフェイスを構成します。

DUT 内の各端子を IP コアのターゲット インターフェイスのいずれかにマッピングします。この例では、入力端子 "Blink_frequency" および "Blink_direction" が AXI4 インターフェイスにマッピングされています。HDL Coder はそれらに対して AXI インターフェイスでアクセス可能なレジスタを生成します。出力端子 "LED" は、PolarFire SoC ボード上の LED ハードウェアに接続する外部インターフェイス "LEDs General Purpose [0:3]" にマッピングされています。

1. [ターゲットを設定]、[ターゲット インターフェイスを設定] タスクで、"Blink_frequency"、"Blink_direction"、および "Read_back" に対して "AXI4" を選択します。

2. "LED" に対して "LEDs General Purpose [0:3]" を選択します。

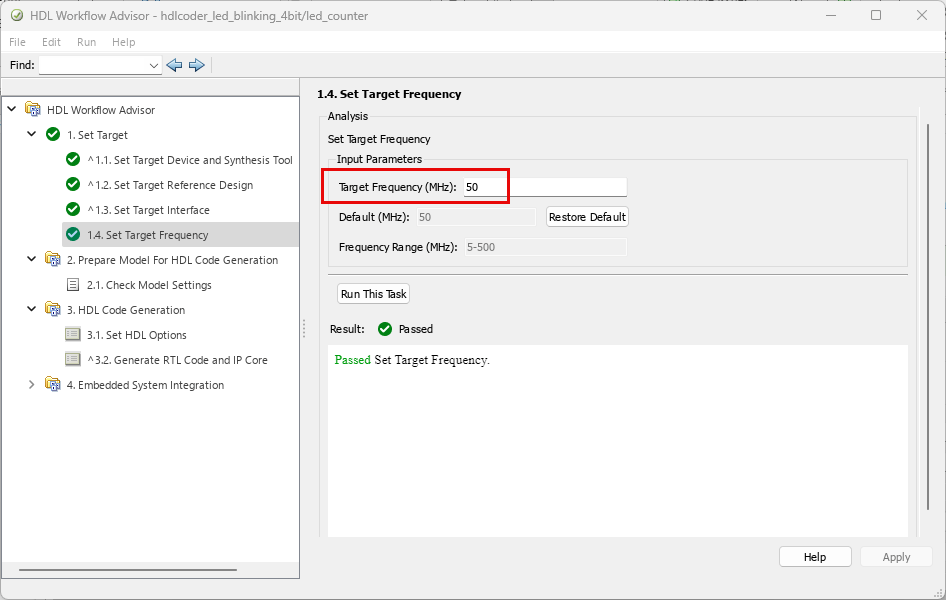

3. [ターゲットを設定]、[ターゲット インターフェイスを設定] タスクで、[ターゲット周波数] を 50 MHz と選択します。

IP コアを生成

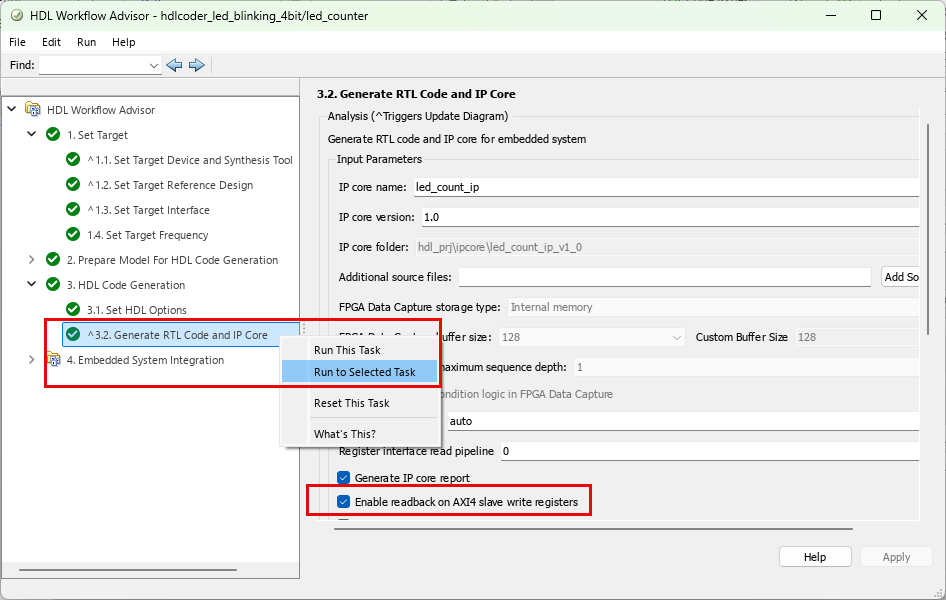

1. [3.2 RTL コードと IP コアの生成] タスクで、[AXI4 スレーブ書き込みレジスタで再読み取りを有効にする] オプションを選択して AXI4 スレーブ入力レジスタから読み取ります。[RTL コードと IP コアの生成] タスクを右クリックして [選択したタスクまで実行] を選択します。

2. IP コア レポートを生成して表示します。

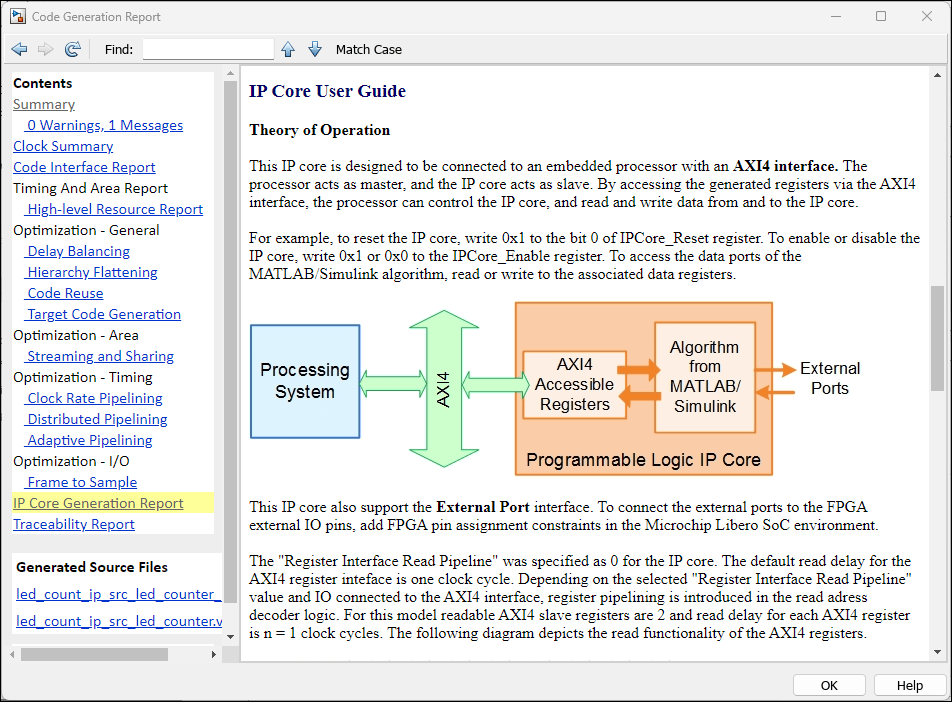

カスタム IP コアを生成すると、IP コア ファイルがプロジェクト フォルダー内の "ipcore" フォルダーに配置されます。カスタム IP コアと一緒に HTML カスタム IP コア レポートが生成されます。このレポートには、生成されたカスタム IP コアの動作と内容が記載されています。

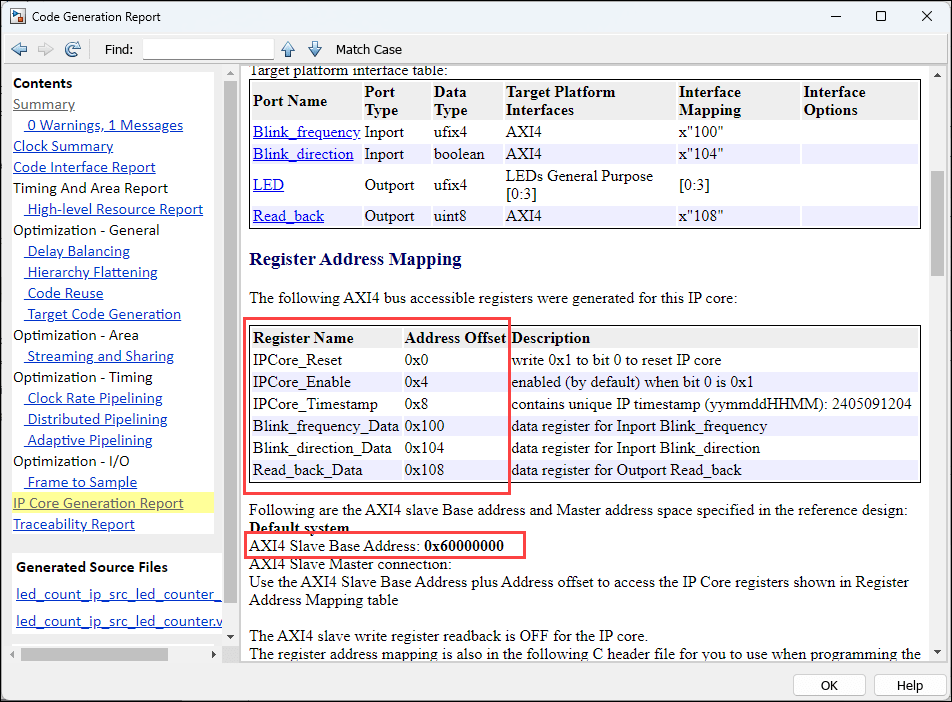

3. レジスタ アドレス マッピング。

IP コアの生成レポートには、モデルのターゲット プラットフォーム インターフェイスに関する詳細も含まれています。この図は、hdlcoder_led_blinking_4bit モデルの端子にマッピングされた AXI4 インターフェイスを示したものです。IP コアの生成レポートの表に、各 AXI4 スレーブ レジスタのインターフェイス マッピング アドレスが表示されています。これらのアドレスは AXI4 スレーブ入力レジスタの読み取りに使用します。

IP コアと Microchip Libero SoC 環境の統合

生成された IP コアを組み込みシステム リファレンス設計に挿入し、FPGA ビットストリームを生成して、ビットストリームを PolarFire SoC ハードウェアにダウンロードします。

リファレンス設計とは、事前定義された Microchip Libero プロジェクトのことです。これには、カスタム IP コアを除く、Libero ソフトウェアで設計を PolarFire SoC ボードに展開するために必要な要素が含まれます。

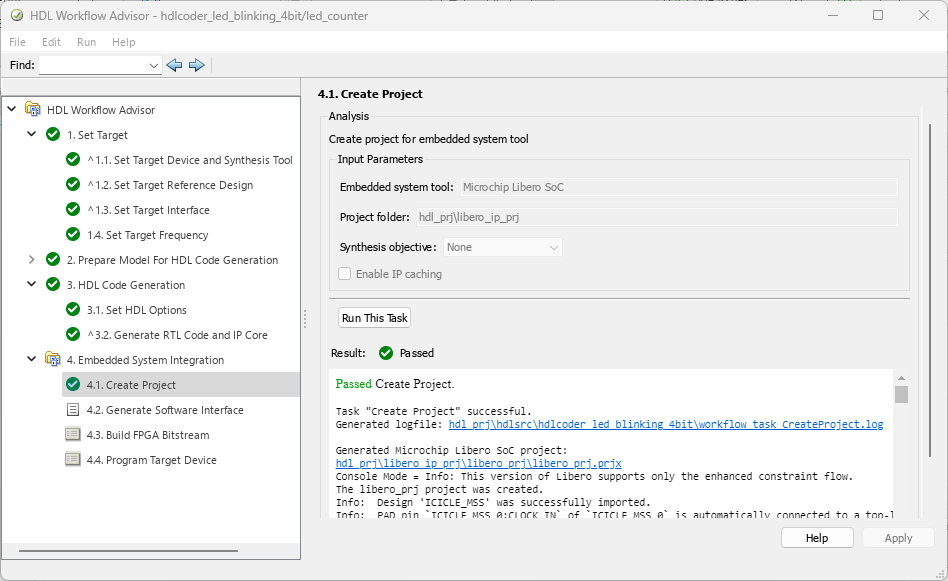

1. Microchip Libero 環境と統合するには、[組み込みシステムの統合] の [プロジェクトを作成] タスクを選択します。[このタスクを実行] をクリックします。IP インテグレーター組み込み設計を含む Microchip Libero プロジェクトが生成されます。

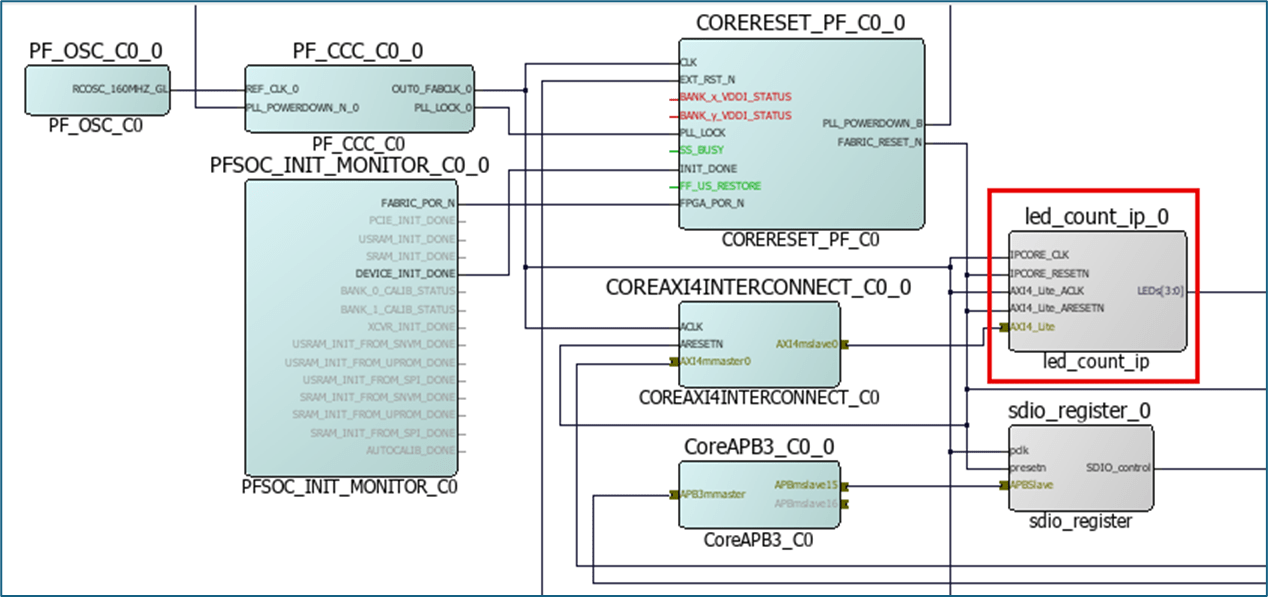

ダイアログ ボックスにプロジェクトへのリンクがあります。必要に応じて、プロジェクトを開いて参照できます。Libero ツールのブロック線図から、HDL Coder で生成された IP コア led_count_ip_0 が AXI インターフェイスを介してマイクロプロセッサ サブシステムに接続されていることを確認できます。

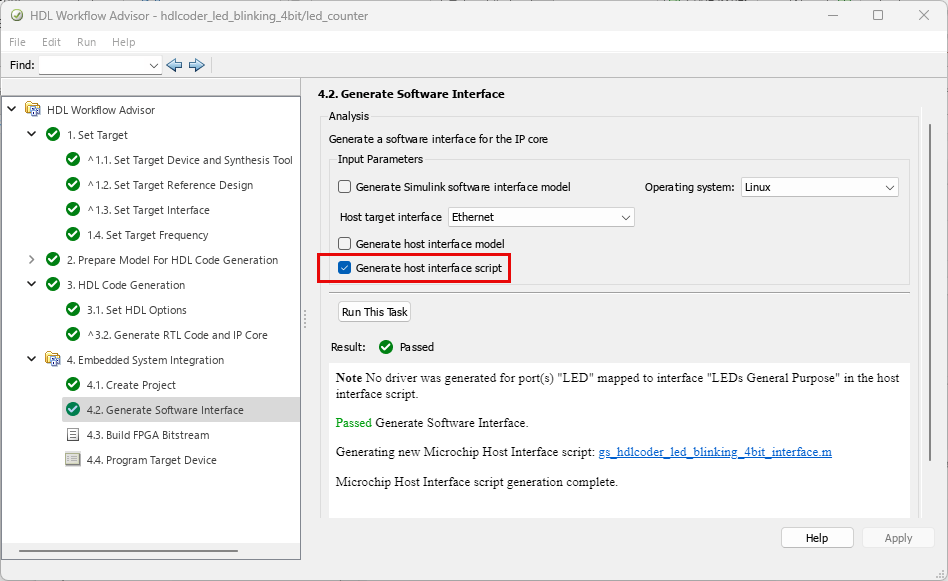

2. 次に、[4.2 ソフトウェア インターフェイスを生成] タスクを選択します。

[4.2 ソフトウェア インターフェイスを生成] タスクで、[ホスト インターフェイス スクリプトの生成] オプションを選択します。ホスト インターフェイス スクリプトには、ターゲット ハードウェアへの接続を可能にするコマンド、および生成された IP コアに対する AXI インターフェイスを介した読み取りと書き込みを可能にするコマンドが含まれます。

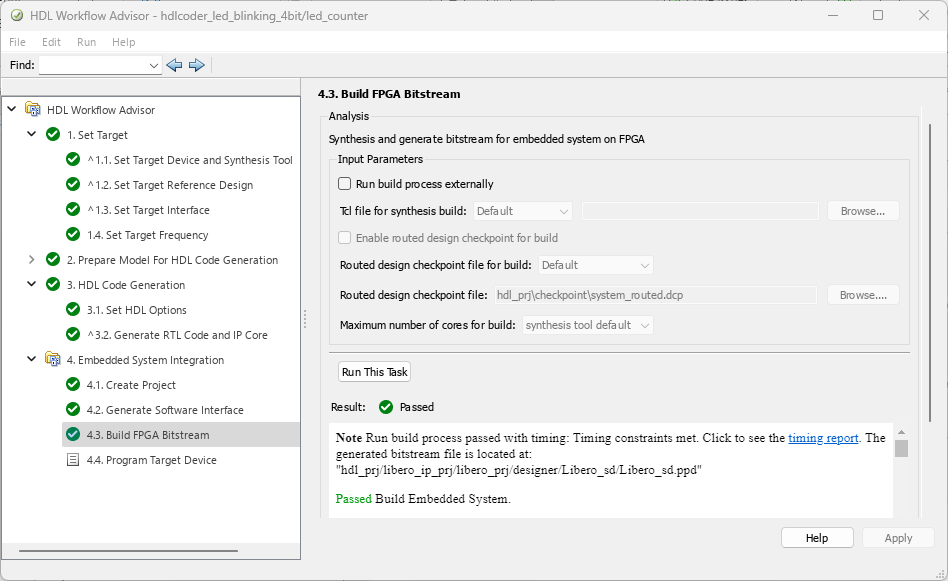

3. [FPGA ビットストリームのビルド] タスクで FPGA ビットストリームを作成します。[ビルド プロセスを外部で実行] オプションを選択すると、Libero 合成ツールが MATLAB とは別のプロセスで実行されます。hdl_prj\libero_ip_prj フォルダーに workflow_task_runExtShell.log ファイルが生成されるまで待つ必要があります。

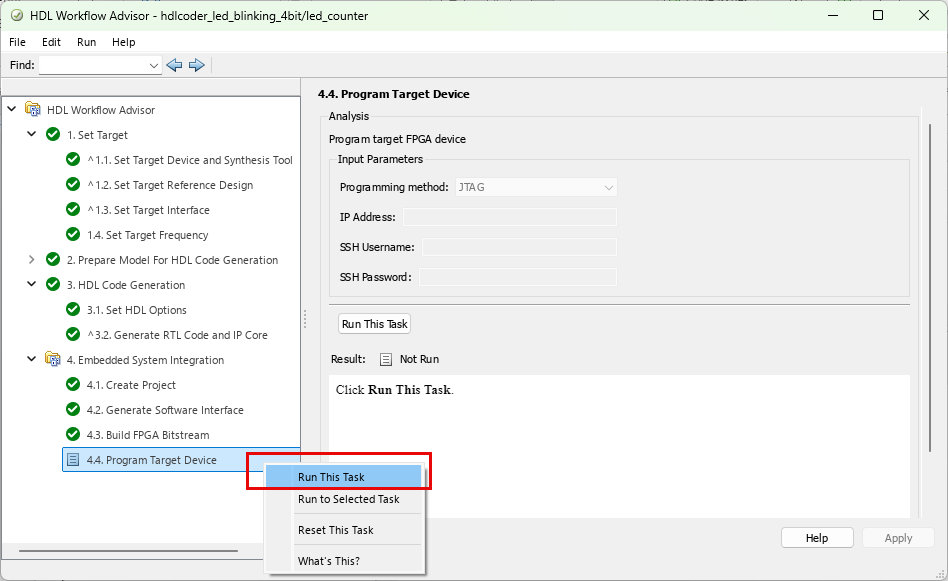

4. ビットストリームの生成後、[4.4 ターゲット デバイスをプログラム] タスクを選択し、[このタスクを実行] をクリックして PolarFire SoC ハードウェアをプログラムします。FPGA ビットストリームを PolarFire SoC ボードにダウンロードするために、[プログラミング メソッド] オプションは JTAG に設定されています。PolarFire SoC ボードの電源をオンにすると、設計が SoC ハードウェアに自動的に再読み込みされます。

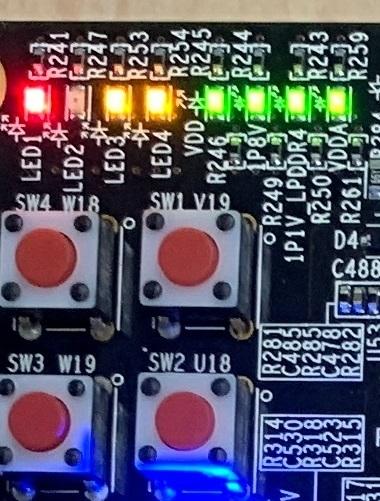

FPGA ハードウェアをプログラムした後、PolarFire SoC ボード上の LED が点滅を開始します。

AXI4 スレーブ入力レジスタの値の読み取り

AXI4 スレーブ入力レジスタの値を読み取るには、AXI4 スレーブ ベース アドレスをインターフェイス マッピング アドレスと一緒に使用します。AXI4 スレーブ ベース アドレスは IP コアの生成レポートから入手できます。AXI4 スレーブ入力レジスタの読み戻しは、Linux コンソールで devmem コマンドを使用するか、MATLAB FPGA プロトタイピング スクリプトを使用して実行できます。

devmem コマンドを使用した AXI4 スレーブ入力レジスタの読み戻し

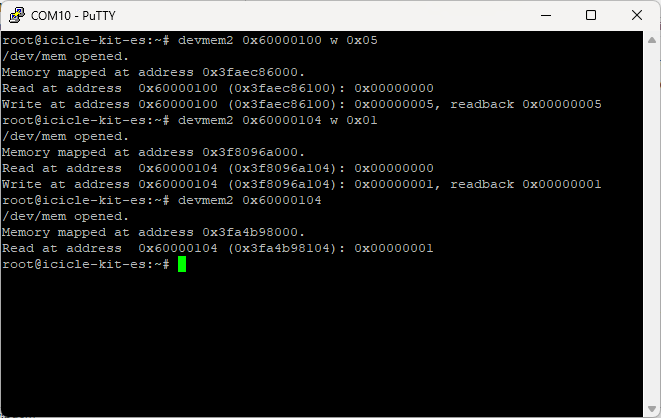

devmem コマンドは PuTTy™ または Hyper ソフトウェアを使用する Linux コンソールで使用できます。ターゲット デバイスに対するビットストリームのプログラムが完了したら、シリアル インターフェイスを使用して PuTTy または Hyper ターミナルを開きます。IP コアの生成レポートの "Register Address Mapping" を参照して、AXI4 スレーブ レジスタのベース アドレスを入手します。AXI4 スレーブ レジスタのベース アドレスが 0x60000000 であることを確認できます。このベース アドレスをアドレス オフセットと共に使用して、AXI4 スレーブ レジスタの読み取りと書き込みの操作を実行できます。

LED の点滅頻度を変更するには、PuTTY ターミナルで次の devmem コマンドを実行します。

devmem2 0x60000100 w 0x05

LED の点滅方向を変更するには、PuTTY ターミナルで次の devmem コマンドを実行します。

devmem2 0x60000104 w 0x01

点滅方向の値を読み戻すには、次の devmem2 コマンドを実行します。

devmem2 0x60000104

コマンドから返される値は 0x00000001 です。これは、前の手順で書き込んだ値です。

MATLAB FPGA IO プロトタイピング スクリプトを使用した AXI4 レジスタの値の読み戻し

[ホスト インターフェイス スクリプトの生成] オプションを選択すると、HDL Coder で 2 つの MATLAB ファイル gs_hdlcoder_led_blinking_4bit_interface.m と gs_hdlcoder_led_blinking_4bit_setup.m が生成されます。

gs_hdlcoder_led_blinking_4bit_interface.m- このインターフェイス スクリプトは、ターゲット オブジェクトを作成し、セットアップ スクリプトをインスタンス化してターゲット ハードウェアに接続します。このスクリプトにより、生成された HDL IP コアに読み取りコマンドと書き込みコマンドが送られます。gs_hdlcoder_led_blinking_4bit_setup.m- このセットアップ関数は、AXI4 スレーブ インターフェイスを追加します。スクリプトには、端子名、方向、データ型、およびインターフェイス マッピング情報をもつ DUT 端子オブジェクトも含まれています。このスクリプトにより、DUT 端子が対応するインターフェイスにマッピングされます。

readPort関数およびwritePort関数を使用して AXI レジスタのデータにアクセスするには、ホスト インターフェイス スクリプトを実行するか次の手順に従います。

1. MATLAB コマンド ウィンドウで次のコマンドを入力してハードウェア接続を設定します。

hProcessor = microchipsoc

microchipsoc 関数は SSH を介してハードウェアにログインします。このコマンドの一部としてボードの IP アドレスを指定することもできます。

2. 次のコマンドを実行して FPGA オブジェクトを作成します。

hFPGA = fpga(hProcessor)

3. 生成された FPGA オブジェクトを入力引数として gs_hdlcoder_led_blinking_4bit_setup(hFPGA) セットアップ関数を実行します。この関数により、生成された IP コアと同じインターフェイスを使用して FPGA オブジェクトが構成されます。

gs_hdlcoder_led_blinking_4bit_setup(hFPGA)

4. writePort コマンドを実行して LED の点滅頻度を変更します。

writePort(hFPGA, "Blink_frequency", 6)

5. readPort コマンドを使用して読み戻し端子 Read_back から値を読み取ります。

data_Read_back = readPort(hFPGA, "Read_back")

まとめ

この例は、Microchip PolarFire SoC Icicle キットへの MATLAB と Simulink の設計の展開を自動化するのにハードウェアとソフトウェアの協調設計ワークフローがどのように役立つかを示しています。このワークフローを繰り返すことにより、設計を分割して展開する最もよい方法を調べることができます。

次の図は、この例で行ったワークフローの概要図を示しています。ハードウェアとソフトウェアの協調設計ワークフローの詳細については、SoC プラットフォーム向けのハードウェア ソフトウェア協調設計ワークフローを参照してください。