HDL ワークフロー コマンド ライン インターフェイス入門

この例では、HDL ワークフロー アドバイザーを使用して、コマンド ラインと [スクリプトへのエクスポート] オプションから HDL ワークフローを実行する方法を示します。

はじめに

この例では、HDL ワークフロー コマンド ライン インターフェイスの手順について順を追って説明します。

HDL ワークフロー コマンド ライン インターフェイスを使用すると、次のワークフローについて、HDL ワークフロー アドバイザーと同じ一連の手順を実行し、同じ構成設定を制御できます。

汎用 ASIC/FPGA

IP コアの生成

Simulink® Real-Time™ FPGA I/O

モデルを開く

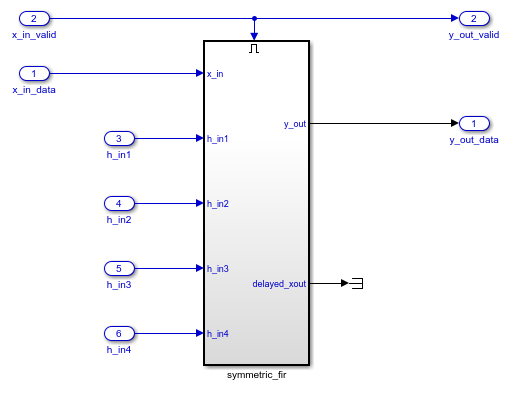

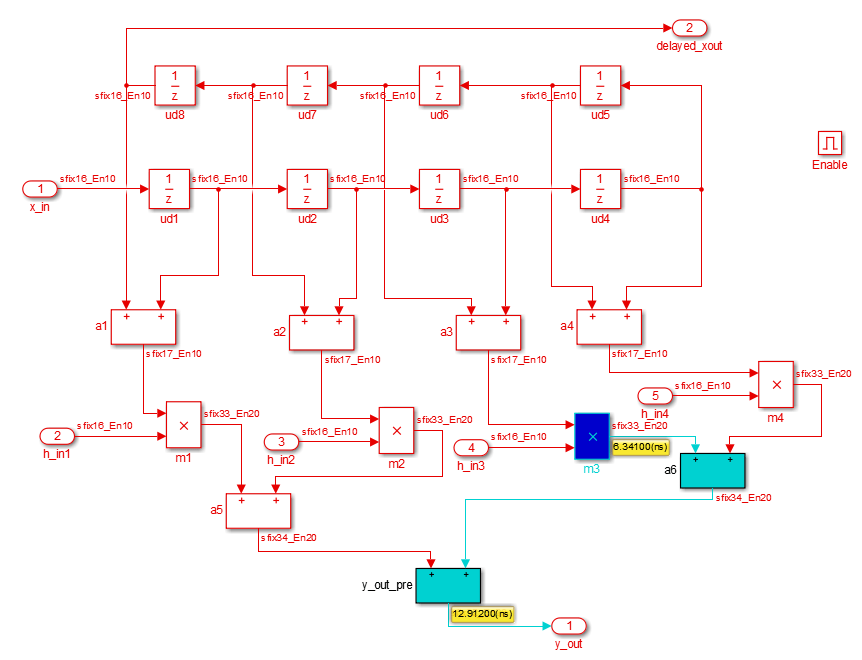

この例では "hdlcoder_sfir_fixed_stream" モデルを使用しますが、HDL ワークフロー コマンド ライン インターフェイスは上記のワークフローと連携するいずれのモデルでも使用できます。

open_system('hdlcoder_sfir_fixed_stream')

目的のサードパーティ ツールがパスに含まれていることを確認します。たとえば、ローカルの既定の Windows の場所にインストールされている Vivado を含めるには、hdlsetuptoolpathコマンドを使用します。

>> hdlsetuptoolpath('ToolName', 'Xilinx Vivado', 'ToolPath',vivadopath);コマンドを実行するときに独自の Vivado インストール パスを使用します。次に、ワークフロー アドバイザーを起動し、適切なサブシステムを DUT として選択します。

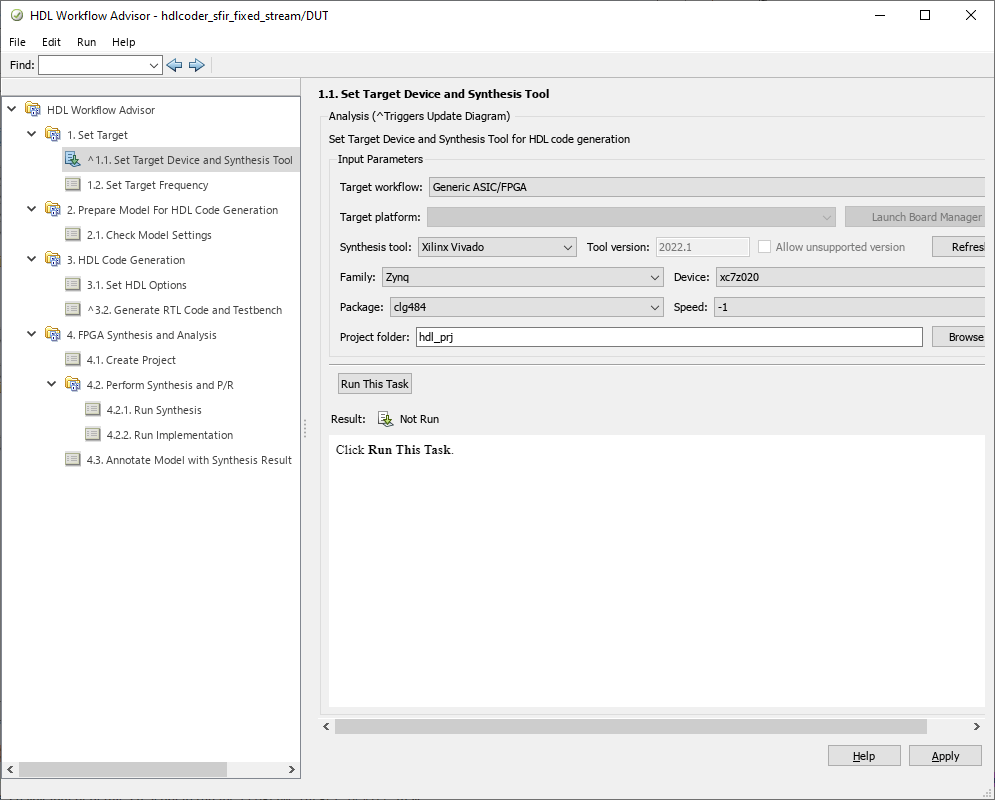

ワークフローの設定

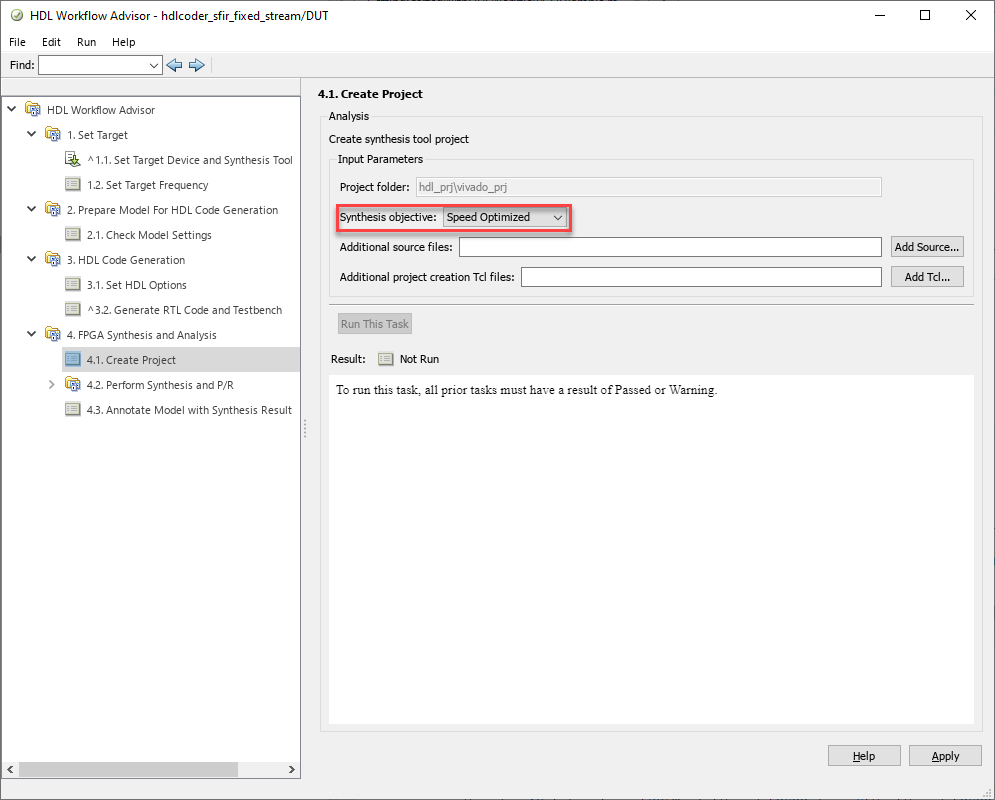

HDL ワークフロー アドバイザーを使用して、プロジェクトの合成ツールやデバイスなどの設定を目的に合わせて設定します。ここでは、合成結果をもつモデルに注釈を付けるため、最初にワークフローを [Generic ASIC/FPGA] に変更します。

合成ツールの大まかな目的も指定できます。たとえば、ツールを [速度の最適化] に設定してみます。

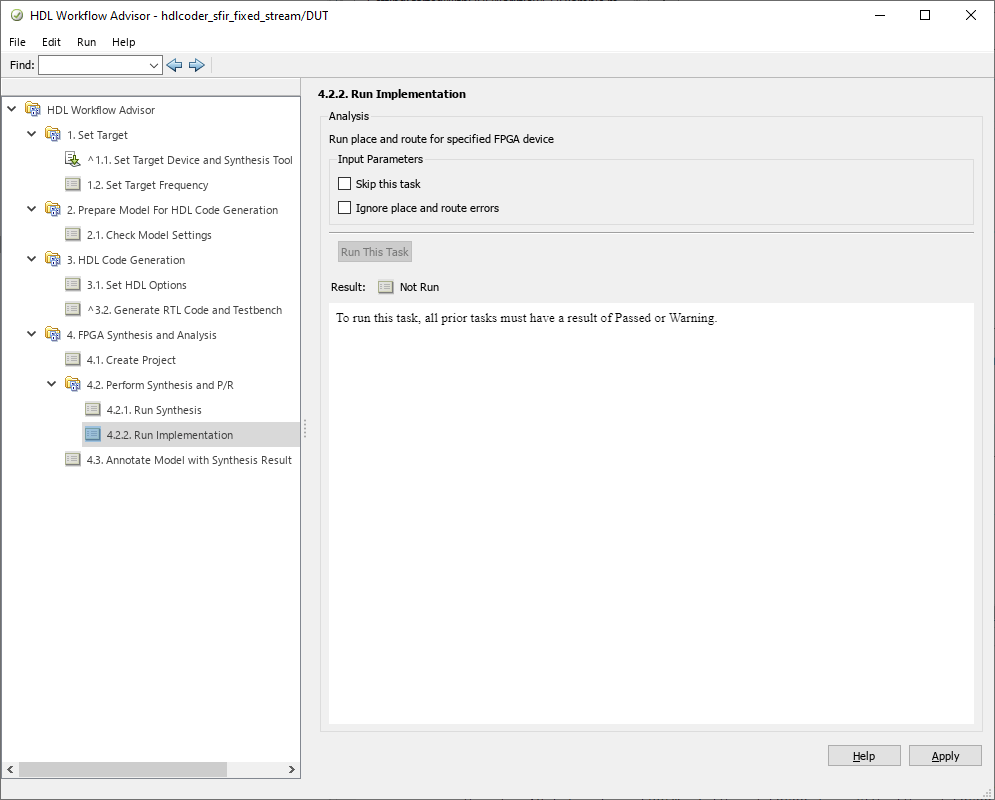

さらに、[実装を実行] の [このタスクをスキップ] チェックボックスを変更して、エクスポートされたスクリプトでこの手順も実行されるようにします。

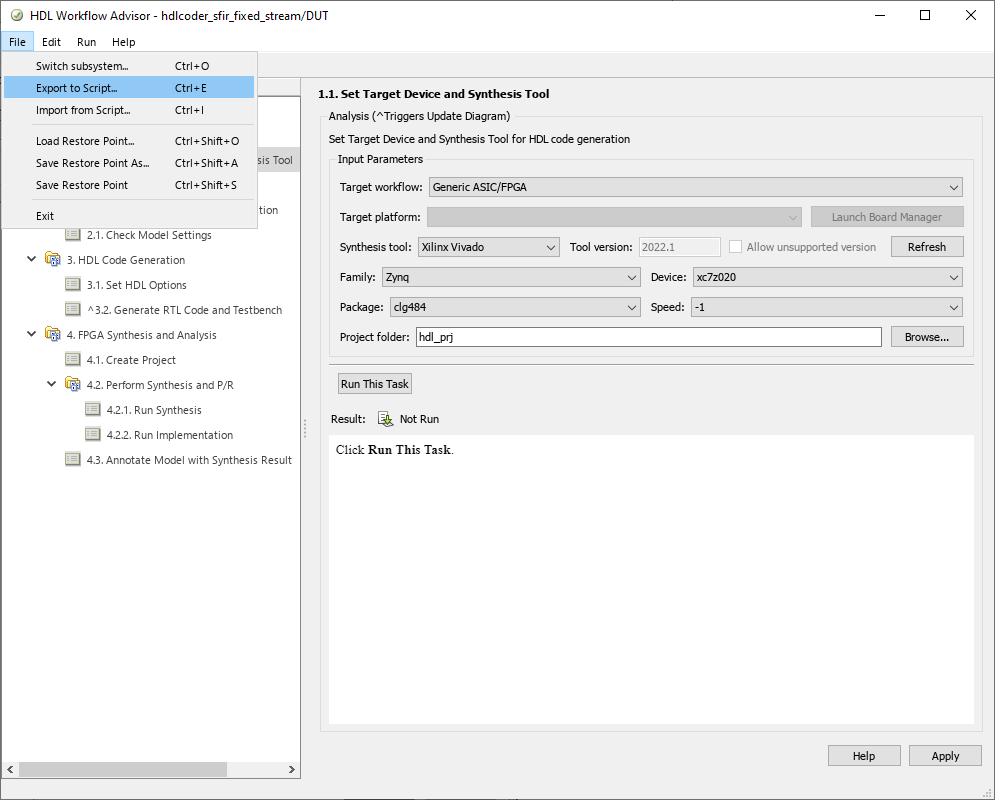

スクリプトへのエクスポート

すべての初期設定の入力が完了したら、設計の反復を高速化するために、ワークフローをコマンド ラインから直接実行できるスクリプトとしてエクスポートします。

ファイルを任意の名前で保存します。既定では "hdlworkflow.m" になります。エクスポートされたスクリプトを次に示します。

%-------------------------------------------------------------------------- % HDL Workflow Script % Generated with MATLAB 9.0 (R2016b Prerelease) at 10:40:45 on 31/12/2015 % This script was generated using the following parameter values: % Filename : '/mathworks/devel/sandbox/cberry/work/demo/hdlworkflow.m' % Overwrite : true % Comments : true % Headers : true % DUT : 'hdlcoder_sfir_fixed_stream/DUT' % To view changes after modifying the workflow, run the following command: % >> hWC.export('DUT','hdlcoder_sfir_fixed_stream/DUT'); %-------------------------------------------------------------------------- % Copyright 2018 The MathWorks, Inc. %% Load the Model load_system('hdlcoder_sfir_fixed_stream'); %% Restore the Model to default HDL parameters %hdlrestoreparams('hdlcoder_sfir_fixed_stream/DUT'); %% Model HDL Parameters %% Set Model 'hdlcoder_sfir_fixed_stream' HDL parameters hdlset_param('hdlcoder_sfir_fixed_stream', 'HDLSubsystem', 'hdlcoder_sfir_fixed_stream/DUT'); hdlset_param('hdlcoder_sfir_fixed_stream', 'ReferenceDesign', 'Default system with AXI4-Stream interface'); hdlset_param('hdlcoder_sfir_fixed_stream', 'ResetType', 'Synchronous'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisToolChipFamily', 'Zynq'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisToolDeviceName', 'xc7z020'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisToolPackageName', 'clg484'); hdlset_param('hdlcoder_sfir_fixed_stream', 'SynthesisToolSpeedValue', '-1'); hdlset_param('hdlcoder_sfir_fixed_stream', 'TargetDirectory', 'hdl_prj/hdlsrc'); %% Workflow Configuration Settings % Construct the Workflow Configuration Object with default settings hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','Generic ASIC/FPGA'); % Specify the top level project directory hWC.ProjectFolder = 'hdl_prj'; % Set Workflow tasks to run hWC.RunTaskGenerateRTLCodeAndTestbench = true; hWC.RunTaskCreateProject = true; hWC.RunTaskRunSynthesis = true; hWC.RunTaskRunImplementation = false; hWC.RunTaskAnnotateModelWithSynthesisResult = true; % Set properties related to 'RunTaskGenerateRTLCodeAndTestbench' Task hWC.GenerateRTLCode = true; hWC.GenerateRTLTestbench = false; hWC.GenerateCosimulationModel = false; hWC.CosimulationModelForUseWith ='Mentor Graphics ModelSim'; hWC.GenerateValidationModel = false; % Set properties related to 'RunTaskCreateProject' Task hWC.Objective = hdlcoder.Objective.None; hWC.AdditionalProjectCreationTclFiles =''; % Set properties related to 'RunTaskRunSynthesis' Task hWC.SkipPreRouteTimingAnalysis = false; % Set properties related to 'RunTaskRunImplementation' Task hWC.IgnorePlaceAndRouteErrors = false; % Set properties related to 'RunTaskAnnotateModelWithSynthesisResult' Task hWC.CriticalPathSource ='pre-route'; hWC.CriticalPathNumber = 1; hWC.AnnotateModel ='original'; hWC.ShowAllPaths = false; hWC.ShowDelayData = true; hWC.ShowUniquePaths = false; hWC.ShowEndsOnly = false; % Validate the Workflow Configuration Object hWC.validate; %% Run the workflow hdlcoder.runWorkflow('hdlcoder_sfir_fixed_stream/DUT', hWC);

スクリプトからのワークフローの実行

スクリプトを直接実行すると、ワークフローが実行され、一連のランタイム メッセージがコンパクトな形式で cmd ウィンドウに出力されます。合成ツールの詳細な出力情報を確認する場合は、目的のタスクの見出しの下で関連する [合成ツール ログ:] のハイパーリンクをクリックすると、このファイルが MATLAB® エディターで開きます。

>> hdlworkflow ### Workflow begin. ### ++++++++++++++ Task Generate RTL Code and Testbench ++++++++++++++ ### Generating HDL for 'hdlcoder_sfir_fixed_stream/DUT'. ### Starting HDL check. ### Begin VHDL Code Generation for 'hdlcoder_sfir_fixed_stream'. ### Working on hdlcoder_sfir_fixed_stream/DUT/symmetric_fir as hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\symmetric_fir.vhd. ### Working on hdlcoder_sfir_fixed_stream/DUT as hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\DUT.vhd. ### Creating HDL Code Generation Check Report DUT_report.html ### HDL check for 'hdlcoder_sfir_fixed_stream' complete with 0 errors, 0 warnings, and 0 messages. ### HDL code generation complete. ### ++++++++++++++ Task Create Project ++++++++++++++ ### Generating Xilinx Vivado 2014.4 project: hdl_prj\vivado_prj\DUT_vivado.xpr ### Synthesis tool log: hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\workflow_task_CreateProject.log ### Task "Create Project" successful. ### ++++++++++++++ Task Run Synthesis ++++++++++++++ ### Synthesis tool log: hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\workflow_task_RunSynthesis.log ### Task "Run Synthesis" successful. ### ++++++++++++++ Task Run Implementation ++++++++++++++ ### Synthesis tool log: hdl_prj\hdlsrc\hdlcoder_sfir_fixed_stream\workflow_task_RunImplementation.log ### Task "Run Implementation" successful. ### ++++++++++++++ Task Annotate Model with Synthesis Result ++++++++++++++ ### Parsing the timing file... ### Matched Source = 'hdlcoder_sfir_fixed_stream/DUT/symmetric_fir/m3_out1' ### Matched Destination = 'hdlcoder_sfir_fixed_stream/DUT/y_out_data' ### Highlighting CP 1 from 'hdlcoder_sfir_fixed_stream/DUT/symmetric_fir/m3_out1' to 'hdlcoder_sfir_fixed_stream/DUT/y_out_data' ... ### Click here to reset highlighting. ### Workflow complete.

対話形式でのワークフローの実行

HDL ワークフロー コマンド ライン インターフェイスは対話形式で使用することもできます。たとえば、スクリプト全体または "Workflow Configuration Settings" のセクションのみを実行した後、WorkflowConfig オブジェクト hWC がワークスペースに読み込まれます。

>> hWC =

GenericTurnkeyConfig with properties:

SynthesisTool: 'Xilinx Vivado'

TargetWorkflow: 'Generic ASIC/FPGA'

ProjectFolder: 'hdl_prj' RunTaskGenerateRTLCodeAndTestbench: true

RunTaskCreateProject: true

RunTaskRunSynthesis: true

RunTaskRunImplementation: true

RunTaskAnnotateModelWithSynthesisResult: true TaskGenerateRTLCodeAndTestbench

GenerateRTLCode: true

GenerateRTLTestbench: false

GenerateCosimulationModel: false

CosimulationModelForUseWith: 'Mentor Graphics ModelSim'

GenerateValidationModel: false TaskCreateProject

Objective: hdlcoder.Objective.SpeedOptimized

AdditionalProjectCreationTclFiles: '' TaskRunSynthesis

SkipPreRouteTimingAnalysis: false TaskRunImplementation

IgnorePlaceAndRouteErrors: false TaskAnnotateModelWithSynthesisResult

CriticalPathSource: 'pre-route'

CriticalPathNumber: 1

AnnotateModel: 'original'

ShowAllPaths: false

ShowDelayData: true

ShowUniquePaths: false

ShowEndsOnly: falseこの構成オブジェクトを編集し、変更後の設定でワークフローを実行できます。たとえば、前回の実行でタスク [実装を実行] を有効にしたため、ここではクリティカル パスのソースを "post-route" に変更すれば、モデルに注釈を付けるタスクだけを再実行できます。

>> hWC.clearAllTasks;

>> hWC.RunTaskAnnotateModelWithSynthesisResult = true;

>> hWC.CriticalPathSource = 'post-route';

その後、hdlcoder.runWorkflow コマンドを使用して、変更後のワークフローの構成を直接実行します。

>> hdlcoder.runWorkflow('hdlcoder_led_blinking/led_counter', hWC)

HDL ワークフロー アドバイザーへのスクリプトのインポート

さらに、エクスポートされたスクリプトに対する変更は、HDL ワークフロー アドバイザーにいつでもインポートし直すことができます。これを行うには、スクリプトで使用されているモデルと同じモデルが読み込まれていることを確認し、[ファイル] メニューの [スクリプトからインポート] を選択します。

インポートが完了すると、スクリプトのすべての設定が HDL ワークフロー アドバイザーに読み込まれます。

HDL ワークフロー コマンド ライン インターフェイスのプログラミング スクリプトを後で使用するために保存

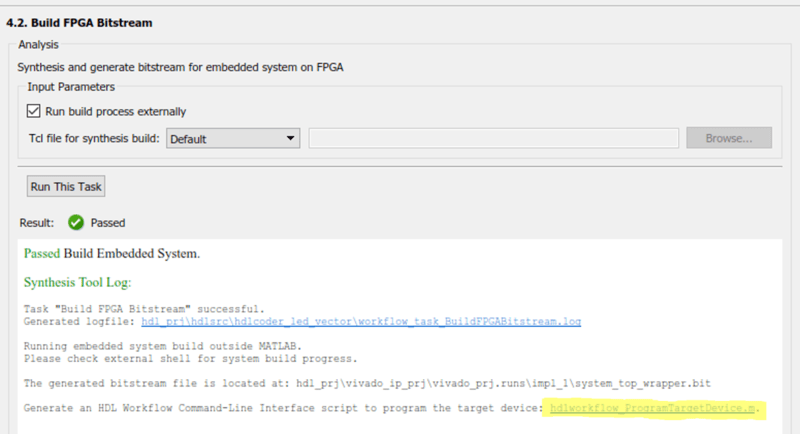

特定の状況では、HDL ワークフロー アドバイザーのすべての手順を再実行する代わりに、アドバイザーの特定のタスクだけを実行できます。たとえば、IP コアの生成ワークフローの実行時、Build FPGA Bitstream タスクで FPGA ビットストリームを生成した後、Program Target Device タスクを実行するためのスクリプトを生成するリンクがアドバイザーから提供されます。

Build FPGA Bitstream タスクで hdlworkflow_ProgramTargetDevice.m のリンクをクリックすると、既存の hdl_prj ディレクトリから Program Target Device タスクのみを実行する HDL ワークフロー コマンド ライン インターフェイス スクリプトが生成されます。そのため、ワークフローのすべての手順を実行せずに、ターゲット デバイスのプログラミングだけを再実行できます。

生成されるスクリプトは標準の HDL ワークフロー CLI スクリプトです。コマンド ライン インターフェイスでの HDL ワークフローの実行時、FPGA ビットストリームが既に生成されていれば、前のタスクとは独立して Program Target Device タスクを実行できます。

これに関連するメモとして、Program Target Device タスクで Download プログラミング メソッドを使用する場合、生成されたビットストリーム ファイルが HDL ワークフロー アドバイザーによって Zynq または Intel SoC ボードの SD カードにコピーされるため、ビットストリームをダウンロードするために Program Target Device タスクを再実行する必要はありません。Linux の起動プロセスで、SD カードから FPGA ビットストリームが自動的に再読み込みされます。

概要

HDL ワークフロー コマンド ライン インターフェイスは、グラフィカルな HDL ワークフロー アドバイザーに代わる、スクリプトによる簡単な代替方法を提供します。最初に HDL ワークフロー アドバイザーを使用してワークフローを設定した後、反復的または自動的に使用するためのスクリプトとしてエクスポートできます。