Modulo by Constant HDL Optimized

定数分母でのモジュロ演算を実行して最適化された HDL コードを生成

ライブラリ:

Fixed-Point Designer HDL Support /

Math Operations

説明

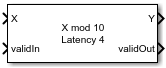

Modulo by Constant HDL Optimized ブロックは、サイクルトゥルーなレイテンシを伴う HDL 用に最適化されたアーキテクチャを使用して、定数分母でのモジュロ演算 (除算後の剰余) を実行します。

Modulo by Constant ブロックでは、Barrett Reduction と機能的に類似したアルゴリズムを使用します。逆数の乗算によって除算演算が計算されるため、一般に組み込みシステムのパフォーマンスが向上します。

例

端子

入力

被除数。実数値のスカラー、ベクトル、行列、または多次元配列として指定します。

[X] が固定小数点データ型の場合、2 進小数点スケーリングを使用しなければなりません。傾きとバイアス表現は固定小数点データ型ではサポートされていません。

データ型: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

入力が有効であるかどうか。boolean スカラーとして指定します。この制御信号は [X] 入力端子からのデータが有効であるかどうかを示します。この値が 1 (true) の場合、ブロックは [X] 入力端子の値を取得します。この値が 0 (false) の場合、ブロックは入力サンプルを無視します。

データ型: Boolean

出力

モジュラス演算の結果。スカラー、ベクトル、行列または多次元配列として返されます。

データ型: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | fixed point

出力データが有効であるかどうか。boolean スカラーとして返されます。この制御信号の値が 1 (true) の場合、ブロックは出力 [Y] を正常に計算しています。この値が 0 (false) の場合、出力データは有効ではありません。

データ型: Boolean

パラメーター

モジュラス演算に使用する除数。正の実数値の有限スカラー、ベクトル、行列、または多次元配列として指定します。

プログラムでの使用

ブロック パラメーター: Denominator |

| 型: 文字ベクトル |

| 値: 正の実数値の有限固定小数点または数値として評価される MATLAB® 式 |

データ型: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point |

既定の設定: '10' |

アルゴリズム

モジュロ演算

は、多くの数学アルゴリズムの重要な基本構成です。ただし、この X mod D の式は、固定小数点と整数の入力に対する計算が効率的でありません。組み込みプロセッサの多くには、整数の除算についての命令がありません。それらがある場合も、解を計算するために多くのクロック サイクルを必要とします。市販されている FPGA でも、効率的な乗算、加算、および減算のための演算回路は設計されていますが、除算は効率的でありません。最後に、固定小数点のモジュロ演算について、除算演算は非有界であるため、語長が小さい入力でも計算に使用される内部データ型の語長を最適化するのが困難です。

モジュロ問題の分母はコンパイル時の定数であるため、ブロックは負方向に丸められる除算を乗算とそれに続くキャストを使用して計算できます。これは、除算演算を書き換えて、

のように表されます。定数は、正確性と計算効率の両方を維持するために必要な精度になるように計算されます。後続のキャストで小数ビットを破棄します。これは、マイクロプロセッサと FPGA のどちらでも効率的な演算です。

Modulo by Constant ブロックでは、Barrett Reduction と機能的に類似したアルゴリズムを使用します。逆数の乗算によって除算演算が計算されるため、一般に組み込みシステムのパフォーマンスが向上します。

Modulo by Constant HDL Optimized ブロックは、サイクルトゥルーなレイテンシを伴う HDL 用に最適化されたアーキテクチャを使用して、定数分母でのモジュロ演算 (除算後の剰余) を実行します。

レイテンシは次のとおりです。

Denominatorが2のべき乗である場合は0それ以外の場合は

4

拡張機能

傾きとバイアス表現は固定小数点データ型ではサポートされていません。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加のコンフィギュレーション オプションがあります。

このブロックには 1 つの既定の HDL アーキテクチャがあります。

| 一般 | |

|---|---|

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

傾きとバイアス表現は固定小数点データ型ではサポートされていません。

バージョン履歴

R2021a で導入Modulo by Constant HDL Optimized ブロックのレイテンシが 9 クロック サイクルから 4 クロック サイクルに短縮しました。

Modulo by Constant HDL Optimized ブロックでベクトルおよび行列の入力がサポートされるようになりました。

For Each Subsystem ブロック内での Modulo by Constant HDL Optimized ブロックの使用がサポートされます。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)