定数による HDL 用に最適化されたモジュロの実装

この例では、Modulo by Constant HDL Optimized ブロックの使用方法を示します。

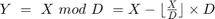

モジュロ演算

は、多くの数学アルゴリズムの重要な基本構成です。ただし、この式は、固定小数点と整数の入力に対する計算が効率的でありません。組み込みプロセッサの多くには、整数の除算についての命令がありません。それらがある場合も、計算に多くのクロック サイクルを必要とします。市販されている FPGA でも、演算回路は乗算、加算、および減算用に最適化されていますが、除算は効率的でありません。最後に、固定小数点のモジュロ演算について、除算演算は非有界であるため、計算に使用されるデータ型を選択するのが困難です。

一般的なモジュロ問題には多くの課題がありますが、分母が定数値であれば問題を単純化できます。この場合は、除算演算を次のように書き換えます。

ここで、 が以下のように十分な精度をもちます。

が以下のように十分な精度をもちます。

は引数の小数部を計算する関数です。この式で使用される演算はすべて、効率的な FPGA の展開に適しています。

は引数の小数部を計算する関数です。この式で使用される演算はすべて、効率的な FPGA の展開に適しています。

次の例では、この演算を Modulo by Constant HDL Optimized ブロックを使用して実行する方法を示し、サンプルのリソース使用率とパフォーマンスの統計を示します。

Modulo by Constant HDL Optimized ブロックの使用方法

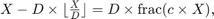

Modulo by Constant HDL Optimized ブロックでは、次のように [分母係数] パラメーターの指定が求められます。

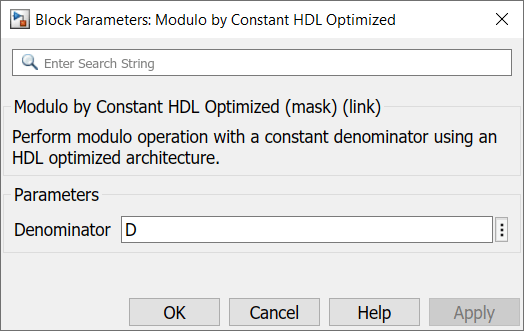

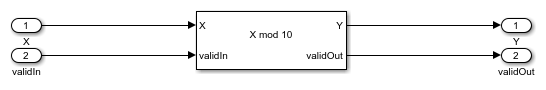

[分母係数] を 10 に設定した場合、ブロックは次のようになります。ブロックのアイコンにモジュロ演算の数式とブロックのレイテンシの両方が表示されます。ブロックのレイテンシは、2 のべき乗でない分母の場合は 4 サイクル、2 のべき乗の分母の場合は 0 サイクルです。

ブロックは、[分母係数] の値と X のデータ型から、必要なすべての定数とデータ型を計算できます。FPGA 展開用に設計されているため、制御信号 validIn と validOut を使用して X と Y が有効であるかどうかを示します。また、生成された HDL コードと同じレイテンシでシミュレーションを行います。

ブロックを使用するには、最初に固定小数点入力データを作成します。以下に示す形式は From Workspace ブロックで使用できます。

同じ形式を使用して、false から true に繰り返し切り替わる boolean の validIn 信号を作成します。

問題のデータの設定を終了するには、モジュロ演算に使用する定数分母と等しくなるように D を設定します。

モデルを開きます。

サブシステム DUT_FXP は、Modulo by Constant HDL Optimized ブロックを使用して固定小数点入力の  を計算します。

を計算します。

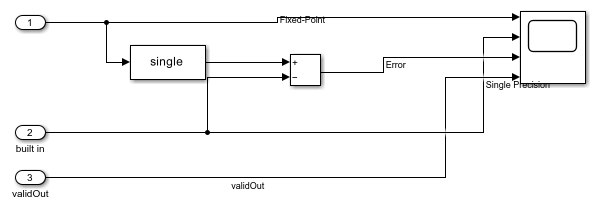

サブシステム DUT_FLT は、[関数] パラメーターが mod に設定された Math Function ブロックを使用して  を計算します。Simulink® の

を計算します。Simulink® の mod 演算では浮動小数点と整数の入力しかサポートされないため、入力データは単精度にキャストされてから Math Function ブロックに入力されます。さらに、遅延ブロックを使用してサブシステム DUT_FXP のレイテンシに一致させます。

サブシステム Compare and Plot は、すべての出力をプロットし、固定小数点の演算と浮動小数点のイデアルの差分を計算します。

モデルをシミュレートし、スコープを調べて固定小数点と浮動小数点の結果を比較します。

Modulo by Constant HDL Optimized ブロックと Math Function ブロックの結果は、下記のプロットに示すように完全に一致します。システムのレイテンシが原因で、シミュレーションを開始してから validOut が最初に High になるまでの遅延があることに注意してください。このレイテンシは、生成された HDL コードでも同じになります。

HDL コードの生成

HDL Coder™ のライセンスがある場合、次に示すように DUT_FXP サブシステムの HDL コードを生成して展開できます。

makehdl('modulo_by_constant_block_example/DUT_FXP');

実装される HDL の統計

Xilinx® Virtex®-7 XC7VX485 FFG1157-1 デバイスにおけるリソース使用率のサンプルの統計を次に示します。このデバイスでは、実装される設計を 250MHz を超えるレートで実行できます。

Resources Usage

_______________ _____

LUT 24

Slice Registers 47

DSP48 1