Infineon AURIX のマルチコア アーキテクチャ

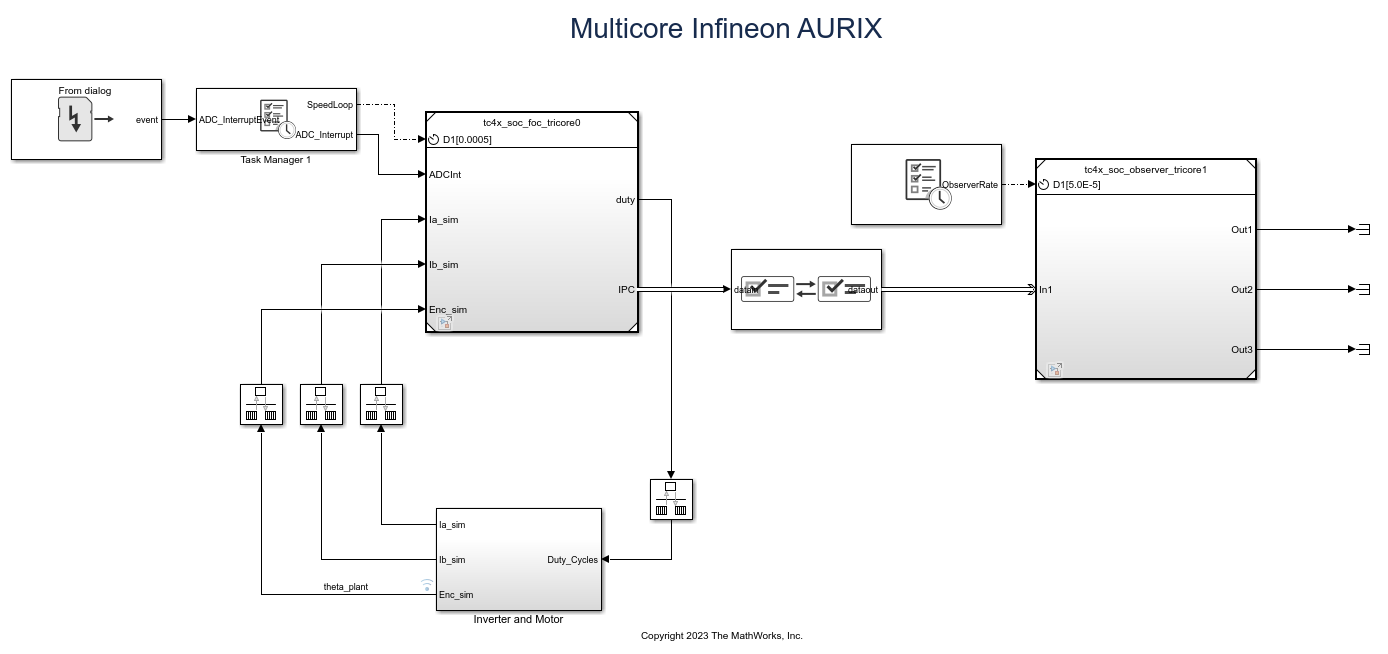

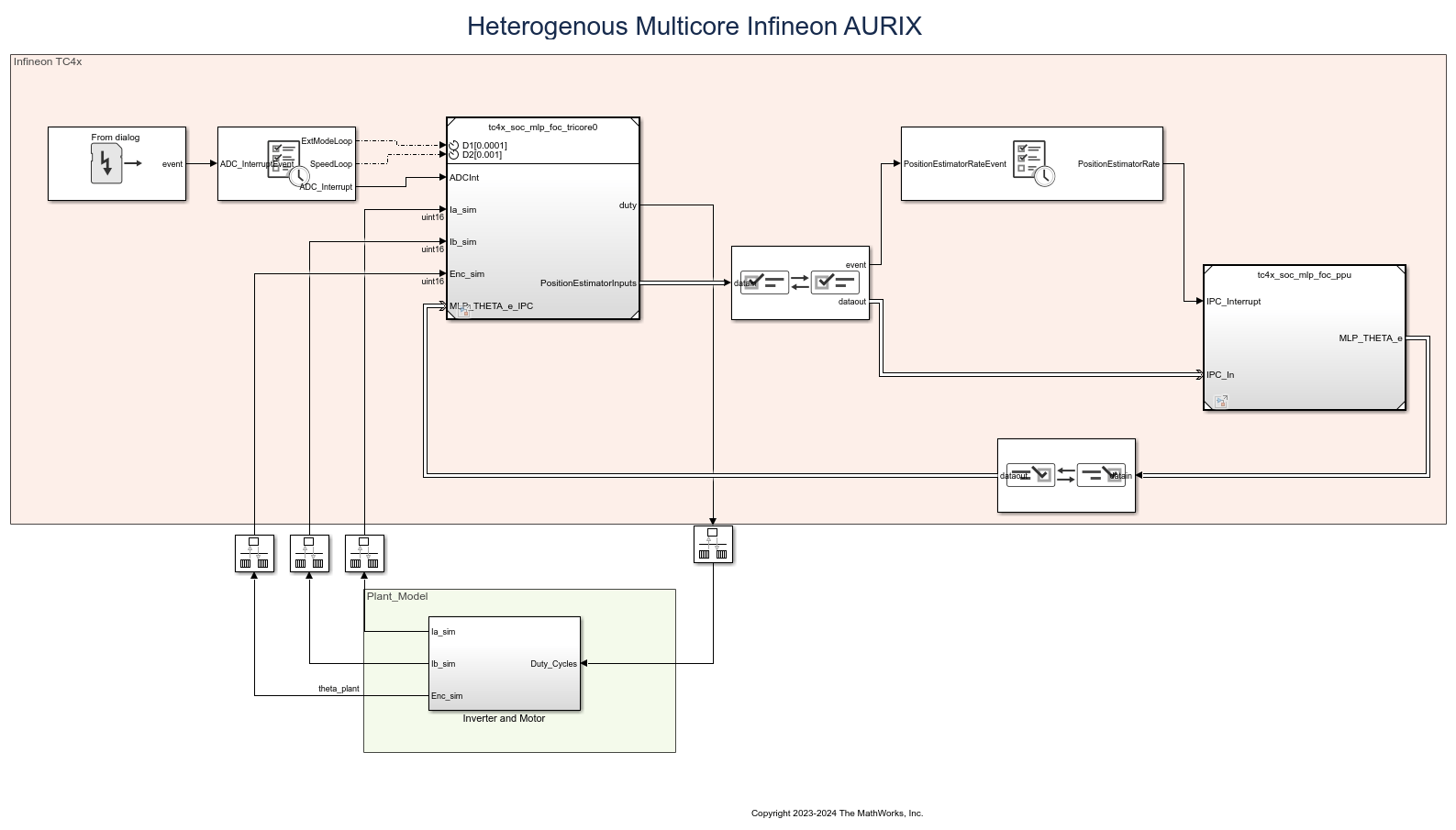

Infineon AURIX TC4x ファミリのマイクロコントローラーには、最大 6 つの TriCore® 処理ユニット (TriCore 0 ~ TriCore 5) が含まれます。TriCore 0 は、AURIX マイクロコントローラーにおいて、システム初期化、起動プロセス、および重要な制御タスクを処理する主要な処理ユニットです。さらに、一部のバリアントには、高度に並列化されたベクトル計算を高速化するために使用できる、専用のハードウェア アクセラレータである並列処理ユニット (PPU) が含まれています。これらの処理ユニットは、独立して、または協調して実行できます。個々の処理ユニットに異なるアプリケーションを割り当てることができます。Simulink® でモジュラーおよび並行設計をサポートするために、複雑なアプリケーションのコンポーネントを複数の処理ユニットに分散できます。

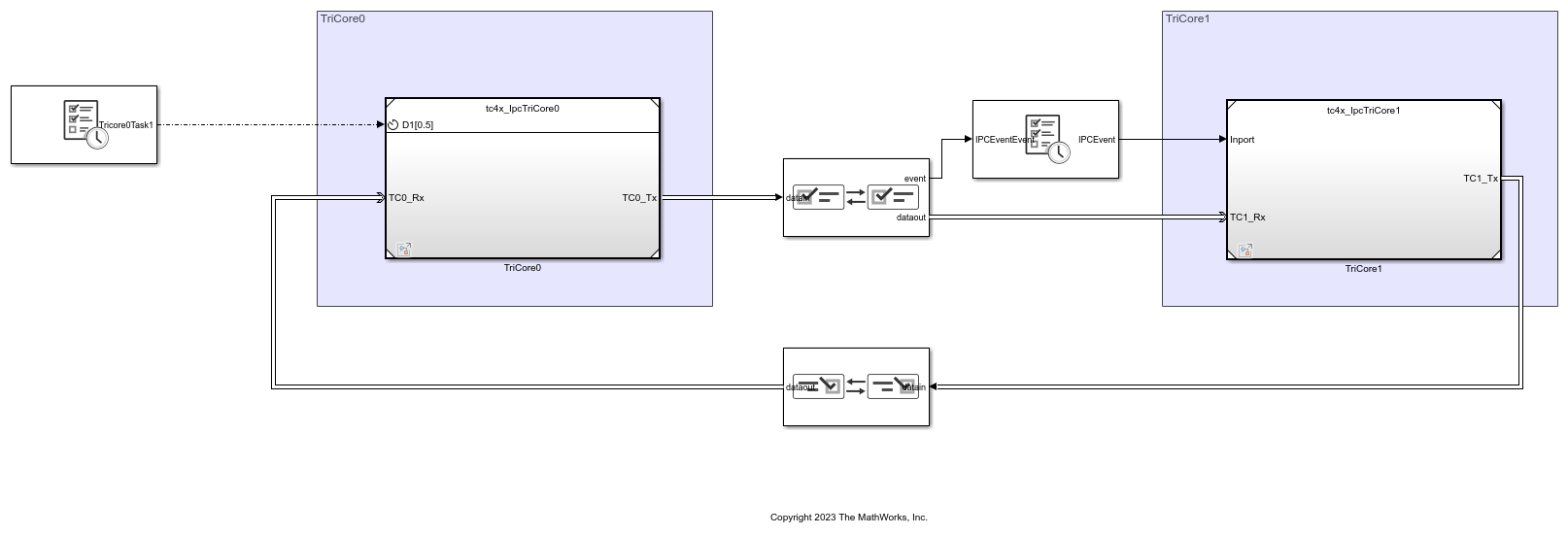

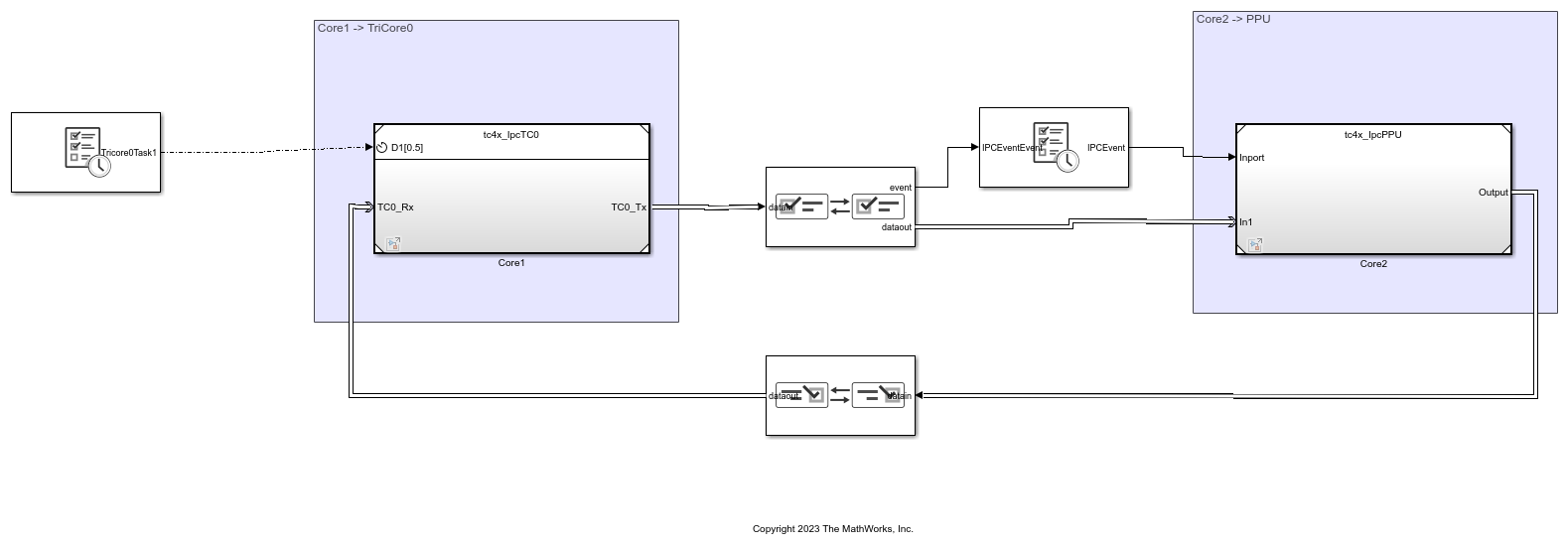

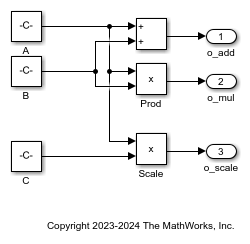

Embedded Coder® Support Package for Infineon AURIX TC4x Microcontrollers は、マルチコアおよびシングルコアのアプリケーション モデルを設計するのに役立ちます。この図は、Infineon AURIX TC4x マイクロコントローラーの異なる処理ユニット (PU) を使用した推奨モデル化シナリオを示します。

モノリシック モデル — 単一の処理ユニット上で Simulink が実行される 1 つの統合アプリケーションを生成する、単一またはスタンドアロンの Simulink モデルです。

SoC ベースのマルチコア モデル — 参加する処理ユニット向けに 1 つ以上の統合アプリケーションを生成する、統合された System-on-Chip (SoC) アーキテクチャです。SoC モデルは、最上位モデルと 2 つ以上の固有の参照モデルで構成されます。最上位モデルは、参照モデル上でアプリケーション アルゴリズムまたはモデルが実行される、組み込みシステム全体を表します。

ブロック

ツール

| SoC Builder | Build, load, and execute multicore application models on Infineon AURIX TC4x hardware boards (R2024b 以降) |

| ハードウェア マッピング | Map tasks and peripherals in a model to hardware board configurations (R2022b 以降) |

トピック

モデル化

- SoC-Based Multicore Modeling for Infineon AURIX Microcontrollers

Design, evaluate, and implement multicore SoC models. - SoC-Based Multicore Modeling Workflow for Infineon AURIX Microcontrollers

Create SoC based multicore models.

- ステップ 1: Design Time-Based Simulink Model

- ステップ 2: Design Event-Based Simulink Model

- ステップ 3: Configure Reference Models

- ステップ 4: Design Top-Level Model

- Monolithic Modeling for Infineon AURIX Microcontrollers

Design, evaluate, and implement single-core models.

コード生成

- Parallel Processing Unit for Optimized Code Generation

Use PPU to implement models with large data processing requirements or fast execution time requirements. - Generate Code and Deploy Using SoC Builder

Generate code and run it on the target hardware board using the SoC Builder tool. - Generate Software Executables for Multicore Models

Generate single or multiple ELF files for all participating cores of Infineon AURIX.

プロセッサインザループ (PIL) シミュレーション

- Model Reference PIL Simulation

Processor-in-the-Loop (PIL) simulation techniques for Infineon AURIX hardware boards. - PIL Simulation Using nSIM Simulator

Run PIL simulations and test PPU based application models using nSIM simulator.