AXI4 Random Access Memory

Libraries:

SoC Blockset /

Memory

Description

The AXI4 Random Access Memory block models a connection between two hardware algorithms through external memory, using the MathWorks® simplified AXI4 manager protocol. Both the writer and the reader are managers, sending read and write requests to memory through the block. The external memory is unmanaged (no logical buffers, no circular buffer). To ensure the integrity of the data, the reader and writer coordinate timing on accesses.

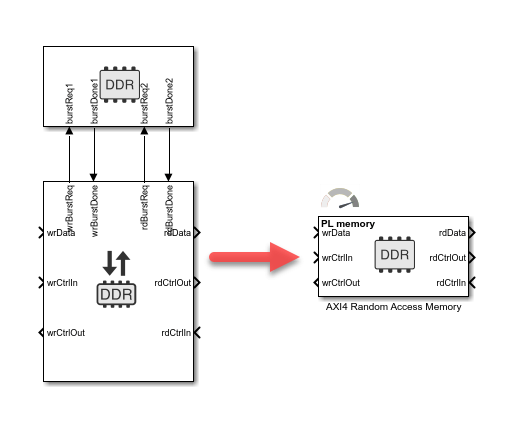

This block is equivalent to a Memory Channel block with the

Channel type parameter set to AXI4 Random

Access connected to a Memory Controller block.

Since the memory controller is implicit to the design - you can instantiate several memory blocks that connect to the same memory unit via a memory controller. Valid blocks are:

The maximum number of manager interfaces in a model is 16.

For more information, see Simplified AXI4 Master Interface.

This image is a conceptual view of this block, with random-access to the memory for writing, and random-access to the memory for reading.

Examples

Random Access of External Memory

Model external memory accesses from FPGA for rotating an ASCII art image. Many applications require FPGA to access memory in random fashion as per the requirements of algorithm. You will learn how to design memory address generation along with other AXI4 master signals to read and write specific regions of memory using SoC Blockset. You will simulate, implement and verify your design on hardware.

Ports

Input

This signal contains the data to the memory.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

This port accepts a control bus from a data consumer block, signaling that the consumer block is ready to accept read data. This input is a read-request from the reader. To create the control bust, use the SoC Bus Creator block.

Data Types: ReadControlM2SBusObj

This port accepts a control bus from a data producer block, signaling that the producer block is ready to send data. This input is a write-request from the writer. To create the control bus, use the SoC Bus Creator block.

Data Types: WriteControlM2SBusObj

Output

This signal contains the data read from the memory.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

This bus represents the protocol bus from the memory channel to the data consumer. To separate the signal from the bus, use the SoC Bus Selector block.

Data Types: ReadControlS2MBusObj

This bus represents the protocol bus from the memory channel to the data producer. To separate the signal from the bus, use the SoC Bus Selector block.

Data Types: WriteControlS2MBusObj

Parameters

Memory simulation provides two levels of timing resolution. Select one of these options:

Burst accurate — Simulates memory contention and high-resolution timing.

Protocol accurate — Simulates AXI4 protocol hand-shaking sequencing and low-resolution timing.

Tip

To enable performance logging, set this parameter to Burst accurate.

Use the Performance Report to

display performance metrics.

Main

Select between processing subsystem (PS) or programming logic (PL) memory.

If the selected board supports only a PL memory, then the default value is

PL memory.If the selected board supports only PS memory or only PL memory, then this parameter is read-only.

If the selected board is not a supported SoC board, then this parameter is not visible.

Specify the size of the memory buffer in bytes.

Select this parameter to enable presimulation memory initialization.

Specify an initial value for memory simulation, as one of the following:

Integer scalar value between 0–255 — The block replicates and loads this value to all memory locations.

Vector of

uint8— The block writes each element of the vector into a memory location.If the vector is smaller than the memory region, the vector is padded with zeros to match the size of the memory region.

If the vector is larger than the memory region, the vector is truncated to match the size of the memory region.

Example: 0 — Initializes all memory locations with

zeros.

Example: 1:10 — Initializes the first ten memory locations with

values 1–10 and the other locations with zeros.

Dependencies

To enable this parameter, select Initialize memory.

Select this parameter to enable postsimulation memory logging.

Name of variable to hold the data of the memory content, specified as a string or character vector.

Example: 'mem_content'

Dependencies

To enable this parameter, select Log memory ending value.

Signal Attributes

Write data signal

wrData can be a multidimensional array. Specify the dimension for the array as a whole number.

Example: 1 — A scalar sample.

Example: [10 1] — A vector of ten scalars.

Example: [1080 1920 3] — A 1080p frame. The frame includes 1080 lines of 1920 pixels per line, and each pixel is represented by three values (for red, green, and blue).

Specify the data type of the wrData port. For help, click the ... button and select Data Type Assistant.

Specify a time interval in seconds to define how often the block updates.

When you do not want the output to have a time offset, specify the

Sample time parameter as a scalar. To add a time offset to

the output, specify the Sample time parameter as a

1-by-2 vector, where the first element is the

sampling period and the second element is the offset. For more information about

sample times in Simulink®, see Specify Sample Time.

Select this parameter to enable data packing across the last dimension of the

signal. The AXI4-Random Access Memory block packs the data along the

last dimension of the signal. For example, if the channel data type is

uint32, the dimensions are [1024 4]. If you

select this sample packing parameter, then the memory channel generates 1024 read or

write transactions of 128 bits. If you clear this sample packing parameter, the memory

channel generates 4096 transactions of 32 bits each.

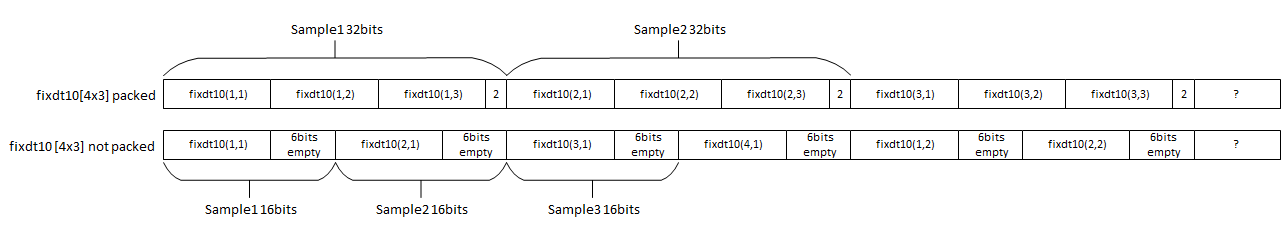

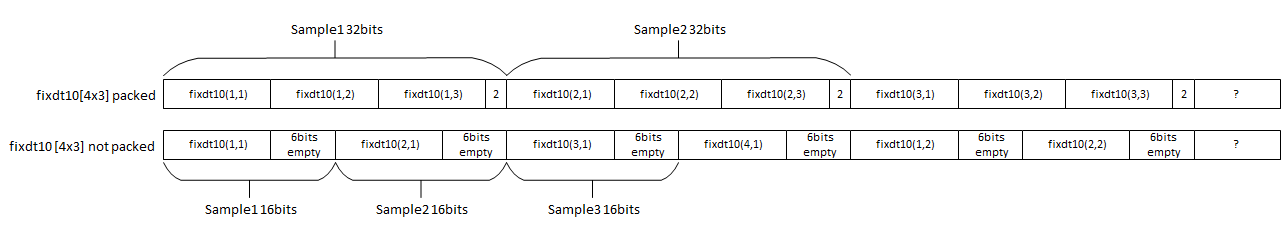

This figure shows how data is aligned for a signal with data type

fixdt10[4x3]. When the data is packed, three 10-bit words are

concatenated and extended by 2 bits to a 32-bit word. When the data is not packed,

each 10-bit word is extended to a 16-bit word.

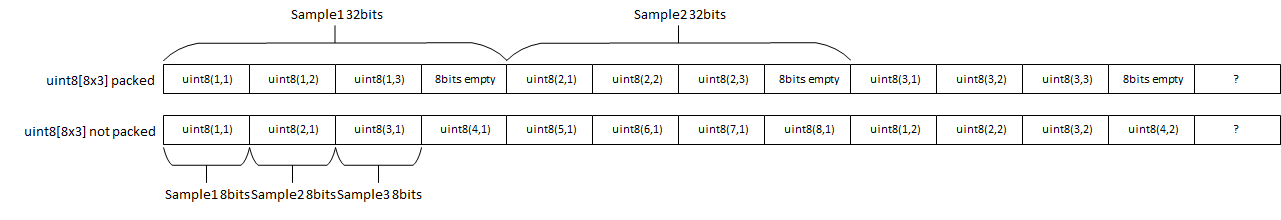

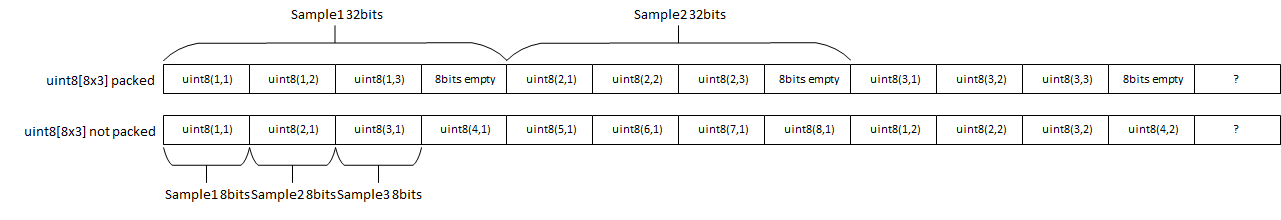

This figure shows how data is aligned for a signal with data type

uint8[8x3]. When the data is packed, three 8-bit words are

concatenated and extended by 8 bits to a 32-bit word. When the data is not packed,

each 8-bit word is represented as an 8-bit sample.

The combined width of the flattened signal must not exceed 512 bits.

Read data signal

Select this box to use the same dimensions and data type for the reader and the writer of this channel. Clear the box to customize different dimensions and data type for the reader and writer interfaces.

rdData can be a multidimensional array. Specify the dimension for the array as a whole number.

Example: 1 — A scalar sample.

Example: [10 1] — A vector of ten scalars.

Example: [1080 1920 3] — A 1080p frame. The frame includes 1080 lines of 1920 pixels per line, and each pixel is represented by three values (for red, green, and blue).

Specify the data type of the rdData port. For help, click the ... button and select Data Type Assistant.

Dependencies

To enable this parameter, clear the Output data signal matches input check box.

Specify a time interval in seconds to define how often the block updates.

When you do not want the output to have a time offset, specify the

Sample time parameter as a scalar. To add a time offset to

the output, specify the Sample time parameter as a

1-by-2 vector, where the first element is the

sampling period and the second element is the offset. For more information about

sample times in Simulink, see Specify Sample Time.

Dependencies

To enable this parameter, clear the Output data signal matches input check box.

Select this parameter to enable data packing across the last dimension of the

signal. The AXI4 Random Access Memory block packs the data along the

last dimension of the signal. For example, if the channel data type is

uint32, the dimensions are [1024 4]. If you

select this sample packing parameter, then the memory channel generates 1024 read or

write transactions of 128 bits. If you clear this sample packing parameter, the memory

channel generates 4096 transactions of 32 bits each.

This figure shows how data is aligned for a signal with data type

fixdt10[4x3]. When the data is packed, three 10-bit words are

concatenated and extended by 2 bits to a 32-bit word. When the data is not packed,

each 10-bit word is extended to a 16-bit word.

This figure shows how data is aligned for a signal with data type

uint8[8x3]. When the data is packed, three 8-bit words are

concatenated and extended by 8 bits to a 32-bit word. When the data is not packed,

each 8-bit word is represented as an 8-bit sample.

The combined width of the flattened signal must not exceed 512 bits.

Dependencies

To enable this parameter, clear the Output data signal matches input check box.

Extended Capabilities

HDL Code Generation

Generate VHDL, Verilog and SystemVerilog code for FPGA and ASIC designs using HDL Coder™.

Fixed-Point Conversion

Design and simulate fixed-point systems using Fixed-Point Designer™.

Version History

Introduced in R2022bThe Performance tab in the block mask has been removed.

Use the Performance Report app to display performance metrics. To enable performance logging, select the Burst accurate parameter.

You can now load an initial value before simulation or log memory content after simulation.

To initialize the memory, open the block mask and select Initialize memory in the main tab. Then, specify the initial value in the Initial value box.

To log the contents of the memory after simulation, open the block mask and select Log memory ending value in the main tab. Then, specify the initial value in the Initial value box.

In previous releases, you can specify the size of the memory region in the Buffer size box, and that was reflected as a read-only Region size parameter. In R2023a, specify that size in the Region size (bytes) parameter.

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)