デッド ロジックの検出

デッド ロジックは、シミュレーション中にアクティブにできないモデルの要素を表します。デッド ロジックの検出では、判定カバレッジと条件カバレッジの起こり得ない結果を特定します。場合によっては、設計内のエラーが原因でデッド ロジックが発生します。モデルのシミュレーションを実行する前に、デッド ロジックの検出を使用して、デッド ロジックについてモデルを解析します。Simulink® Design Verifier™ におけるデッド ロジックの設計エラー検出には、次の 2 つの解析方法があります。

デッド ロジック (一部):このオプションを選択した場合、Simulink Design Verifier は、浮動小数点の有理近似などの近似を行わずに、またはループの近似中にモデルを解析します。詳細については、Approximations During Model Analysisを参照してください。このオプションを使用すると、Simulink Design Verifier でアクティブ ロジックまたは未判定のオブジェクティブがレポートされず、モデルのデッド ロジックが特定されない場合があります。

このオプションは次で使用できます。

モデル アドバイザー。モデル アドバイザーを使用した設計エラーのチェックを参照してください。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [Design Verifier]、[設計エラー検出] ペインで、次を行います。

網羅的解析を実行:このオプションを使用すると、Simulink Design Verifier は、デッド ロジックと未判定のオブジェクティブに加えて、アクティブ ロジックをレポートします。このオプションにより、場合によっては追加のデッド ロジックが特定または検出される場合があります。解析では近似が使用され、それに応じてレポートされます。

このオプションは、[コンフィギュレーション パラメーター] ダイアログ ボックスの [Design Verifier]、[設計エラー検出] ペインで使用できます。

デッド ロジックの部分チェックを実行

モデル アドバイザーを使用していない場合、デッド ロジックを検出するには、次を行います。

[Design Verifier] タブの [モード] セクションで、[設計エラー検出] を選択します。

[エラー検出の設定] をクリックします。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [Design Verifier]、[設計エラー検出] ペインで、次を行います。

デッド ロジック (一部)オプションを有効にします。

網羅的解析を実行オプションが選択されている場合、オフにします。

解析するカバレッジ オブジェクティブを

[MCDC]に設定します。ドロップダウン メニューから選択できるオプションは、[判定]、[条件判定]、および[MCDC]です。

[OK] をクリックしてこれらの設定を適用し、[コンフィギュレーション パラメーター] ウィンドウを閉じます。

[設計エラーの検出] をクリックします。

デッド ロジックの網羅的解析を実行

[Design Verifier] タブの [モード] セクションで、[設計エラー検出] を選択します。

[エラー検出の設定] をクリックします。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [Design Verifier]、[設計エラー検出] ペインで、次を行います。

デッド ロジック (一部)オプションを有効にします。

網羅的解析を実行オプションを選択します。

解析するカバレッジ オブジェクティブを

[MCDC]に設定します。ドロップダウン メニューから選択できるオプションは、[判定]、[条件判定]、および[MCDC]です。

[OK] をクリックしてこれらの設定を適用し、[コンフィギュレーション パラメーター] ダイアログ ボックスを閉じます。

[設計エラーの検出] をクリックします。

デッド ロジック解析の実行および結果の確認

この例では、sldvSlicerdemo_dead_logic モデル例でのデッド ロジックの検出方法を説明します。デッド ロジックの検出では、モデル要素が非アクティブで残される原因となる、モデル内の到達不可能なオブジェクティブを見つけます。

sldvSlicerdemo_dead_logicモデルを開きます。openExample('slcheck/AnalyzeTheDeadLogicExample',... 'supportingFile','sldvSlicerdemo_dead_logic');

[Design Verifier] タブの [モード] セクションで、[設計エラー検出] を選択します。

[エラー検出の設定] をクリックします。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [Design Verifier]、[設計エラー検出] ペインで、次を行います。

デッド ロジック (一部)オプションを有効にします。

網羅的解析を実行オプションが選択されている場合、オフにします。

解析するカバレッジ オブジェクティブを

[MCDC]に設定します。ドロップダウン メニューから選択できるオプションは、[判定]、[条件判定]、および[MCDC]です。

[設計エラーの検出] をクリックします。

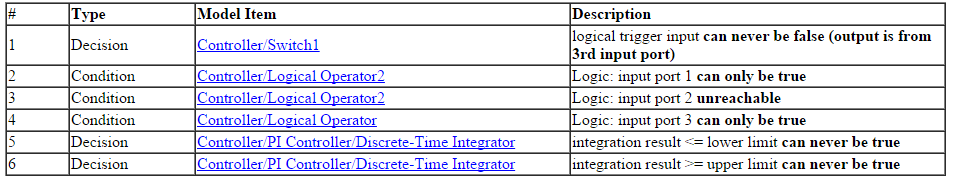

デッド ロジックについてモデルが解析され、結果が [結果の概要] ウィンドウに表示されます。結果から、

32個のオブジェクティブ中8個がデッド ロジックであることがわかります。[解析結果をモデル上で強調表示] をクリックします。デッド ロジックのモデル要素は赤で強調表示されます。

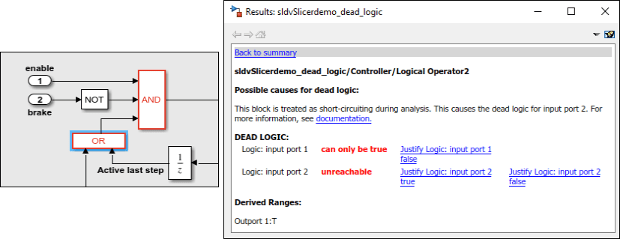

Controllersubsystem を開き、赤で強調表示された OR ブロックをクリックします。結果インスペクターにはデッド ロジックの概要が表示されます。set入力は1と等しいため、OR ブロックのinput port 1は [true のみ可能] となります。ステータスは、input port 1の偽条件がデッド ロジックであることを示しています。同様に、オブジェクティブが実行されないため、input port 2はunreachableであり、これはデッド ロジックです。

[結果の概要] ウィンドウで [HTML] をクリックして、詳細な解析レポートを参照します。

レポートには、モデル内でデッド ロジックとなるすべての結果の概要が表示されます。

デッド ロジック

詳細な解析結果は、データ ファイルの解析結果の表示と解釈の

DeadLogic fieldに格納されます。このデータ ファイルは、結果のさらなる解析に使用できます。

提案:

次の手順を実行すると、モデル スライサーを使用して特定のブロックに影響を与える可能性のあるパラメーターを確認できます。

a. モデル スライサーを使用して SLSlicerAPI.ParameterDependence のオブジェクトを作成します。

slicerObj = slslicer('sldvSlicerdemo_dead_logic');

pd = slicerObj.parameterDependence;b. Discrete-Time Integrator ブロックに影響を与えるパラメーターを見つけます。

param = parametersAffectingBlock(pd, 'sldvSlicerdemo_dead_logic/Controller/PI Controller/Discrete-Time Integrator');

上の図には、Discrete-Time Integrator ブロックに影響を与える関数 parametersAffectingBlock から返されたパラメーターが示されています。関数で返されるパラメーターは、調整用と考えることができます。

c. クリーンアップ操作を実行してモデルのコンパイル状態を終了します。

slicerObj.terminate;