グローバルな Simulink 関数を使用したエクスポート関数モデルの解析

この例では、AUTOSAR サーバー ランナブルとして使用されるグローバルな Simulink 関数で構成されるエクスポート関数モデル sldvexGlobalSimFcn の解析方法を説明します。

1.sldvexGlobalSimFcn モデルを開きます。

open_system('sldvexGlobalSimFcn');2.テスト生成解析を実行するには、[Design Verifier] タブで [テストの生成] をクリックします。

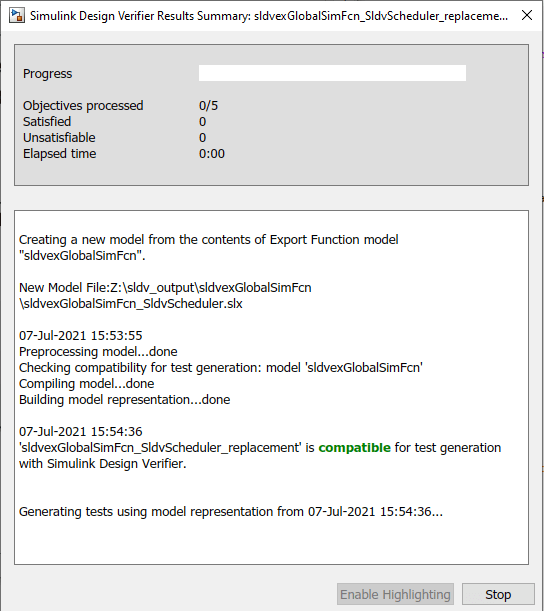

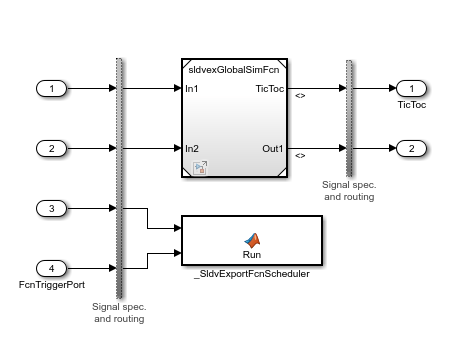

[Simulink Design Verifier の結果の概要] ウィンドウには、スケジューラ モデル sldvexGlobalSimFcn_sldvScheduler.slx が作成されたことが示されます。スケジューラ モデルはsldvextractを使用して生成することもできます。

このスケジューラ モデルは、MATLAB® Function ブロック _SldvExportFcnScheduler と、周期的に関数呼び出しを行う Function-Call Subsystem で構成されています。この MATLAB Function ブロックは、Simulink 関数の入力引数を表す入力端子によって駆動されます。FcnTriggerPort と呼ばれる追加の Inport ブロックの値は、タイム ステップ内で特定の関数を呼び出すかどうかを示します。

3.テスト生成解析後、[Simulink Design Verifier の結果の概要] ウィンドウには 5/5 のオブジェクティブが達成されたという結果が示されます。