リアルタイム モデルの準備

参照結果の取得、パフォーマンスの最適化

リアルタイム用の Simscape モデルの準備には、ターゲット マシンに対して十分に小さいコストとタイム ステップで正確な結果が得られるように、パフォーマンスと忠実度のバランスを反復的に調整することが含まれます。最初に、モデルから参照結果を取得します。固定ステップ ソルバーを使用することで参照結果と比較して正確な結果がモデルから得られる場合、そのモデルについて、リアルタイム ターゲットへの展開を試すことができます。必要に応じて、次の手順に従ってパフォーマンスと忠実度のバランスを調整します。

より複雑なブロックやパラメーター化の代わりに理想的またはシステムレベルのブロックや理想的なパラメーター化を使用する。

高速なダイナミクスの原因を取り除く。

数値的スティッフネスの原因を取り除く。

ゼロクロッシングの原因を取り除く。

分割ソルバーを使用する。

モデルを分割する。

ソルバーの反復を最小限にする。

FPGA 展開の場合、モードの原因を減らす。

高速なダイナミクスや数値的スティッフネスについて、ソルバーのパフォーマンスを解析するには、ソルバー プロファイラー ツールを使用します。固定ステップ固定コストに変換する準備ができたら、simscape.getLocalSolverFixedCostInfo 関数を使用して非線形反復の実行回数を決定します。

ツール

| ソルバー プロファイラー | ソルバー性能のボトルネックを特定します。 |

関数

simscape.getLocalSolverFixedCostInfo | Determine iteration requirement when transitioning to fixed cost (R2021b 以降) |

トピック

固定ステップ固定コストのセットアップ

- ソルバー プロファイラーを使用したモデル ダイナミクスの確認

ソルバー プロファイラーを使用してモデルのシミュレーションに影響する要因を特定します。 - リアルタイム シミュレーションのソルバー

指定される固定ステップ ソルバー、ステップ サイズおよび反復回数は、Simscape™ モデルがリアルタイムでどのようにシミュレーションが行われるかに影響します。 - Simscape のスティッフネス影響分析

Simscape ネットワークの全体的なシステムのスティッフネスに対する特定のブロック変数の効果を解析する。 - ステップ サイズと反復回数の選択

許容可能な精度と速度を提供するステップ サイズと反復回数の組み合わせを指定することで、Simscape モデルをリアルタイム シミュレーション用に最適化し、オーバーランを回避します。 - 計算コストの推定

リアルタイム ターゲット マシンで Simscape モデルのシミュレーションを行う際にオーバーランが発生する可能性が高いかどうかを、計算コストを推定して判断します。

パフォーマンスの最適化

- ゼロクロッシングの削減

ゼロクロッシングを引き起こすコンポーネントを排除することで、固定ステップ シミュレーションの最小ステップ サイズを大きくし、Simscape モデルをリアルタイム対応にします。 - 分割ソルバーを使用したシミュレーションの高速化

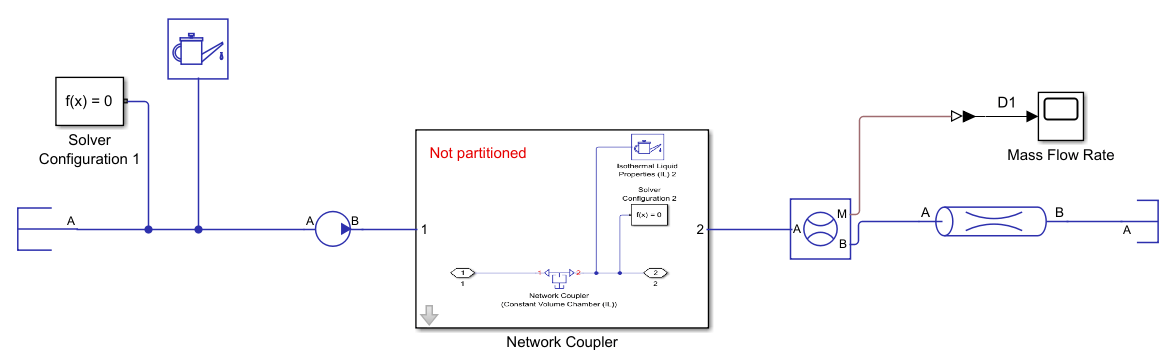

Simscape 分割ソルバーを使用して、大規模な連立方程式を、解きやすい複数の小規模な連立方程式に変換することにより、パフォーマンスを改善する。

FPGA 展開

- Simscape ハードウェアインザループ ワークフロー入門 (HDL Coder)

Simscape ハードウェアインザループ ワークフローのモデル化のガイドラインと制限。 - Simscape Language Support for FPGA HIL Deployment (HDL Coder)

Simscape language support in Simscape Hardware-in-the-Loop Workflow. - Simscape サブシステム置換のモデリング ガイドライン (HDL Coder)

Simscape サブシステムを状態空間アルゴリズムに置き換えるための、Simscape モデル化のベスト プラクティス。 - Piecewise-Constant Resistor を線形スイッチド コンポーネントに置き換え (HDL Coder)

非線形コンポーネントをもつ Simscape モデルを線形スイッチド モデルに変換する。 - Estimate Achievable Target Frequency Without Running Synthesis (HDL Coder)

Estimate the optimal frequency that you want your Simscape models to achieve on FPGA without running synthesis. - Modeling Techniques for Simscape Converters for FPGA HIL Deployment (HDL Coder)

Model your power electronic converter by using hardware-in-the-loop (HIL) simulation in a real-time target machine.

汎用プラットフォーム

- 代替プラットフォームを使用する場合の要件

ハードウェア、ソフトウェア、コンパイラの最低限の推奨仕様に従い、カスタム スタンドアロン アプリケーションを使用してハードウェアインザループ (HIL) シミュレーション用の Simscape モデルを展開する。 - 組み込みおよび汎用リアルタイム リソース

Simulink® Coder™ および Embedded Coder® では、システム ターゲット ファイル (STF) を使用して、特定のリアルタイム オペレーティング システムとのインターフェイスに用いるコードを生成します。