Design and Simulate SerDes Systems

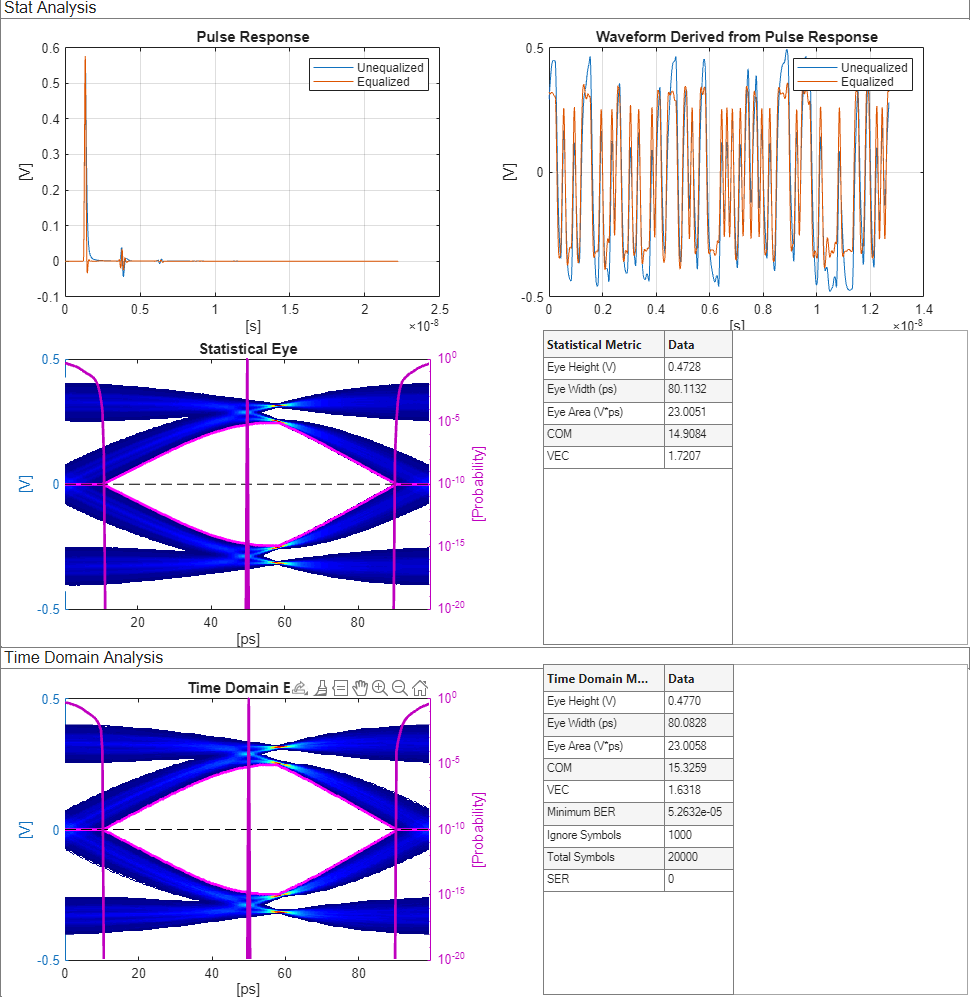

High-speed electronic systems suffer from signal degradation caused by various impairments such as impedance mismatch, attenuation, and crosstalk. Using the equalization and gain modulation blocks in the SerDes Toolbox™, you can compensate for the distortions introduced by the lossy channels.

Starting with the SerDes Designer app, you can design the top-level SerDes systems and perform statistical analysis. Use the building blocks and system objects to design, configure, simulate and analyze the SerDes system including the transmitter and the receiver.

Apps

| SerDes Designer | Design and analyze SerDes systems for export to Simulink, MATLAB and IBIS-AMI |

| S-Parameter Fitter | Convert S-Parameter network to impulse response (Since R2021b) |

| CTLE Fitter | Fit poles and zeros to CTLE transfer functions (Since R2022a) |

Blocks

Objects

Functions

Topics

- Design SerDes System and Export IBIS-AMI Model

Create and analyze a SerDes system, and export an IBIS-AMI model using the SerDes Designer app.

- Clock and Data Recovery in SerDes System

Explore the behavior, control and characteristics of a first order clock data recovery (CDR).

- Phase Detectors: Baud-Rate Type-A Versus Bang-Bang

To successfully send and receive data between a SerDes transmitter and receiver you need to satisfy a myriad of conditions.

- Symbol Error Rate

Compare symbol error rates from input stimulus and equalized waveforms.

- The SerDes Toolbox DFE Adaptation

The SerDes Toolbox Decision Feedback Equalizer (DFE) adaptation is a "blind" correlation-based adaptive equalization algorithm.

- ADC IBIS-AMI Model Based on COM with Genetic Algorithm Optimization

This example shows how to improve the performance of SerDes global optimization through the use of genetic algorithms and statistical analysis.

- Statistical Analysis in SerDes Systems

Customize and explore the statistical analysis of SerDes systems.

- Jitter Analysis in SerDes Systems

Inject Jitter into link analysis and equalization design.

- Analog Channel Loss in SerDes System

Define the loss model to represent the analog channel in a SerDes system.

- Linux Version Compatibilities

Generate shared objects on compatible Linux versions.

- Model and Measure Jitter in Serial Data Systems

Model and measure jitter in serial data systems. (Since R2026a)