このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

UART レシーバー用の FIFO インターフェイス DPI コンポーネントを生成する

この例では、UART レシーバーと統合することを目的とした FIFO バッファー インターフェイス用の SystemVerilog DPI コンポーネントを生成する方法の完全なワークフローを示します。インターフェースは MATLAB で記述され、HDL シミュレータにエクスポートされます。UART レシーバーとそのテストベンチ用の SystemVerilog ファイルも提供されます。

説明のために、この例では 64 ビット Windows 7 の Modelsim 10.3c を使用します。ただし、この同じ手順は他のシステムやシミュレータでも簡単に再現できます。

要件と前提条件

この例に必要なサードパーティ製品:

シミュレーター:Mentor Graphics® ModelSim®/QuestaSim® または Cadence® Xcelium™

サポートされている C コンパイラの 1 つ:Microsoft® Visual C++、または GNU GCC

背景

汎用非同期送受信機 (UART) は、シリアル ラインを介してデータを送受信する回路です。UART は通常、RS-232 標準で使用され、受信機と送信機が含まれています。ただし、この例では受信機のみが使用されます。

シリアル伝送は、0 の「スタート ビット」で始まり、その後にデータ ビットが続き、「パリティ ビット」と「ストップ ビット」で終わります。1 バイトの送信は次の図に示されています。

転送は非同期です。つまり、クロック情報はありません。そのため、受信機と送信機は、使用するボー レート、ストップ ビット、パリティ ビットについて合意する必要があります。この例では、ボーレート 19,200、ストップ ビット 1、パリティ ビットなしで 1 バイトが転送されます。

下の図に示すように、オーバーサンプリング方式を使用して、ボーレートの 16 倍のレートでデータ ビットの中間点を推定します。

次の回路図は、UART 受信機の設計を示しています。

手順 1: MATLAB 設計

最初のステップは、設計の要件を満たす MATLAB コードを記述することです。テストベンチで要件をキャプチャする必要があります。この例では、設計は 8 ワードの先入れ先出し (FIFO) バッファで構成されています。

デザイン:FIFO_バッファ

テスト ベンチ:FIFO_バッファ_tb

手順 2: MATLABテストベンチが要件を満たしていることを確認する

テストベンチを実行して実行時エラーがないことを確認すると、以下の図がプロットされるはずです。

FIFO_Buffer_tb

テストベンチは次のように設計を実行していることに注意してください。

クロックサイクル<15:6 バイトを書き込み (書き込み信号が有効、読み取り信号が無効)、次に 6 バイトを読み取ります (読み取り信号が有効、書き込み信号が無効)。

クロックサイクル>15:読み取りと書き込みを同時に行います。(例:書き込まれたバイトは次のクロック サイクルで読み取られます。

手順 3: DPIコンポーネントを生成し、HDLシミュレータで動作を検証する

コンポーネントを生成するには、次のコマンドを実行します。

dpigen -testbench FIFO_Buffer_tb FIFO_Buffer -args {0,int8(0),0}

下の図は、この例に関連するファイルを示しています。

DPIGEN が DPI コンポーネントとそのテストベンチを生成したら、以下の手順に従って SystemVerilog テストベンチを実行できます。

ModelSim/QuestaSim を GUI モードで起動します。

HDL シミュレータのコード生成ディレクトリの下の

codegen/dll/FIFO_Buffer/dpi_tbに現在のディレクトリを変更します。シミュレーションを開始するには次のコマンドを入力してください

do run_tb_mq.do

次の波形が生成されます。

これは、6 バイトを書き込んでからそれを読み取り、続いて 8 バイトの書き込みと読み取りを同時に行う MATLAB テストベンチと一致していることに注意してください。

シミュレーションが終了すると、コンソールに次のテキストが表示されます。

**************TEST COMPLETED (PASSED)**************

手順 4: 生成されたDPIコンポーネントをUARTレシーバー設計に統合する

DPI コンポーネントの動作が検証されたら、それを UART レシーバーに統合します。次の図は、さまざまなコンポーネントに必要なファイルを示しています。

DPI コンポーネントが統合された UART レシーバーを実行するために、「uart_rx_FIFO_tb.sv」という名前のテストベンチが提供されています。UART コンポーネントは、以下に示すようにテストベンチでインスタンス化されます。

// Instantiate DUT generated using MATLAB Based SystemVerilog DPI FIFO_Buffer_dpi u_FIFO_Buffer_dpi( .clk(clk), .clk_enable(clk_enable), .reset(reset), .wr(rx_done_tick), .w_data(dout), .rd(rd), .Empty(Empty), .r_data(r_data), .Full(Full) );

手順 5: UART 受信機のシミュレーション

設計を正常にシミュレートするには、次のファイルが同じフォルダーにあることを確認してください。

手順 3 と同様に、Modelsim を開き、次のコマンドを使用して .do ファイルを実行します。

do run_tb.do

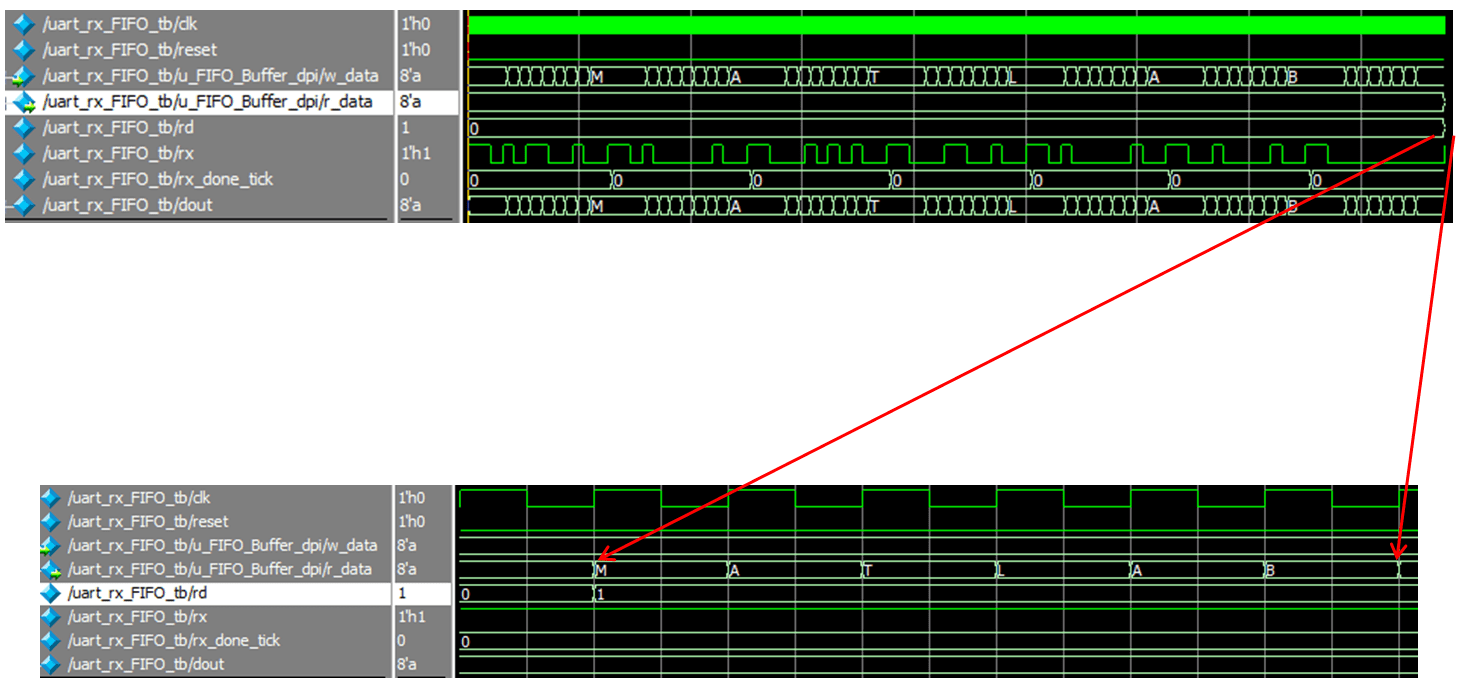

次の波形が生成されます。

テストベンチでは、6 つの ASCII 文字 ('MATLAB') がシリアル 'rx' 信号を介して転送され、FIFO バッファに書き込まれます。6 番目の文字の転送が完了すると、「rd」信号がアサートされ、文字 (「MATLAB」) が「r_data」に戻されます。

参考文献

Pong P. Chu (2008), FPGA Prototyping by Verilog Examples. Hoboken, New Jersey: John Wiley & Sons, Inc.