このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

速度を最適化した後の数値的相違の検出

この例では、HDL コード生成後、Trigonometric Function ブロックを含むモデルにどのような数値の差が生じる可能性があるかを示します。これらの数値の差を、生成された検証モデルで確認できます。検証モデルは、元のモデルを、ブロック実装および速度と面積の最適化の影響を示す生成されたモデルと比較します。

Trigonometric Function モデル

モデル hdlcoder_sincos_cordic_optimization を開きます。

open_system('hdlcoder_sincos_cordic_optimization') set_param('hdlcoder_sincos_cordic_optimization', 'SimulationCommand', 'Update')

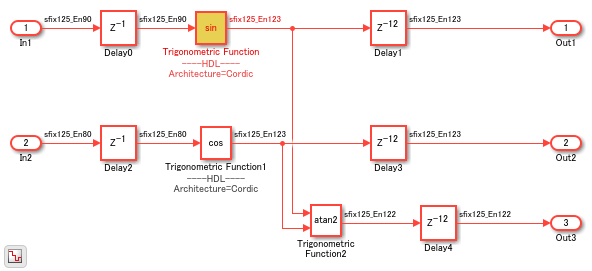

HDL_DUT サブシステム内部では、このモデルは HDL アーキテクチャが CORDIC に設定されていて、[LatencyStrategy] が MAX に設定されている Trigonometric Function ブロックを使用します。ブロック設定は、Trigonometric Function ブロックの入力でパイプラインを導入します。

open_system('hdlcoder_sincos_cordic_optimization/HDL_DUT')

モデルでは、さまざまな最適化が有効になっています。モデルで保存されている HDL パラメーターを確認するには、関数 hdlsaveparams を使用します。

hdlsaveparams('hdlcoder_sincos_cordic_optimization')

%% Set Model 'hdlcoder_sincos_cordic_optimization' HDL parameters

hdlset_param('hdlcoder_sincos_cordic_optimization', 'ClockRatePipelining', 'off');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'EDAScriptGeneration', 'off');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'EnableTestpoints', 'on');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'GenerateCoSimModel', 'ModelSim');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'GenerateValidationModel', 'on');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'HDLGenerateWebview', 'on');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'HDLSubsystem', 'hdlcoder_sincos_cordic_optimization/sin_cordic');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'HDLSynthCmd', 'set_global_assignment -name VHDL_FILE "$src_dir/%s"\n');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'HDLSynthFilePostfix', '_quartus.tcl');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'HDLSynthInit', 'load_package flow\nset top_level %s\nset src_dir "[pwd]"\nset prj_dir "q2dir"\nfile mkdir ../$prj_dir\ncd ../$prj_dir\nproject_new $top_level -revision $top_level -overwrite\nset_global_assignment -name FAMILY "Cyclone IV"\nset_global_assignment -name DEVICE EP4CE115F29C7\nset_global_assignment -name TOP_LEVEL_ENTITY $top_level\n');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'HDLSynthTerm', 'execute_flow -compile\nproject_close\n');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'HDLSynthTool', 'Quartus');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'MaskParameterAsGeneric', 'on');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'MinimizeClockEnables', 'on');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'MinimizeIntermediateSignals', 'on');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'ResetType', 'Synchronous');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'ShareAdders', 'on');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'TargetLanguage', 'Verilog');

hdlset_param('hdlcoder_sincos_cordic_optimization', 'Traceability', 'on');

hdlset_param('hdlcoder_sincos_cordic_optimization/HDL_DUT/Trigonometric Function', 'Architecture', 'Cordic');

hdlset_param('hdlcoder_sincos_cordic_optimization/HDL_DUT/Trigonometric Function1', 'Architecture', 'Cordic');

HDL コードと検証モデルの生成

最適化の影響を確認するには、関数 makehdl を使用して HDL_DUT サブシステムの HDL コードと検証モデルを生成します。

makehdl('hdlcoder_sincos_cordic_optimization')

HDL チェック レポートを開くと、ブロックの入力で導入された遅延を示す警告メッセージが表示されていることがわかります。検証モデルのシミュレーションを実行するときに、最初のサイクルで数値の不一致が生じる可能性があります。

コードの生成が完了したら、モデル gm_hdlcoder_sincos_cordic_optimization_vnl が表示されます。この例では、モデルは hdlcoder_sincos_cordic_optimization_validation という名前で保存されています。

open_system('hdlcoder_sincos_cordic_optimization_validation') set_param('hdlcoder_sincos_cordic_optimization_validation', 'SimulationCommand', 'Update')

数値の差の確認

シアンで強調表示されている HDL_DUT サブシステムは、このサブシステムが元のモデル HDL_DUT_vnl のサブシステムと異なることを示します。HDL_DUT サブシステムは、HDL コードの生成の完了後に生成されたモデルの一部であり、最適化の効果を示します。また、Trigonometric Function ブロックによって導入されたパイプラインも表示されます。

open_system('hdlcoder_sincos_cordic_optimization_validation/HDL_DUT')

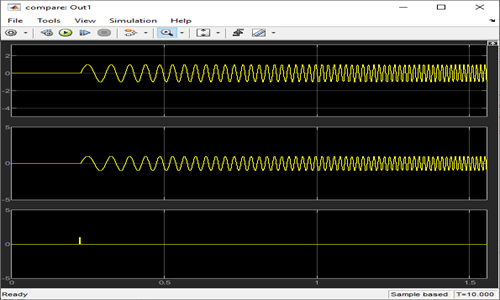

モデルのシミュレーションを実行すると、シミュレーションの最初のサイクルで検出されたアサーションが表示されます。これは数値の不一致を示します。不一致は、ブロックの入力で導入されたパイプラインによって生じます。不一致を修正するには、ブロック実装、[InputPipeline] などの HDL ブロック プロパティ、またはブロックの入力でパイプラインを導入する最適化の使用を回避します。