このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

速度と面積の最適化

ターゲット ハードウェアに対し、速度と面積の最適化を使用して、タイミングおよび面積の要件を満たす SystemC™ コードを MATLAB® 関数から生成します。面積の最適化は、設計のリソース使用率を削減します。速度の最適化は、クリティカル パスを最適化することで設計がより高い周波数で実行されるように、ターゲット ハードウェアでの設計のタイミングを改善します。

クラス

hdl.WorkingSet | Working set object that generates working sets form input image for HLS code generation (R2023a 以降) |

関数

coder.hdl.loopspec | Unroll or stream loops in generated HDL and High-Level Synthesis (HLS) code |

coder.hdl.constrainlatency | Specify the minimum and maximum acceptable hardware latency for a MATLAB function for High-Level Synthesis (HLS) code generation (R2022a 以降) |

coder.hdl.arraydistance | Specify minimum or maximum array distance inside pipelined

for-loop (R2022b 以降) |

coder.hdl.stable | MATLAB 設計で安定した入力を定義する (R2022b 以降) |

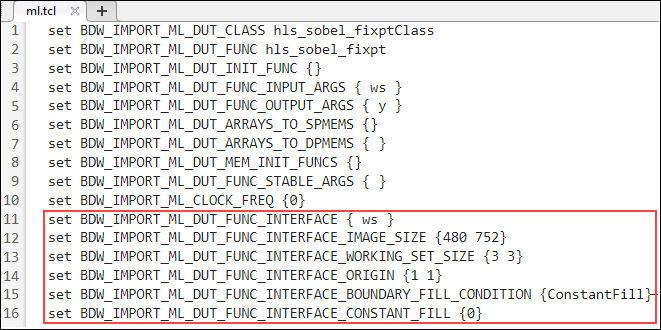

coder.hdl.interface | Specify input to be mapped to the line buffer interface in HLS (R2023a 以降) |

トピック

- Map Persistent Arrays to RAM

To map the persistent variables to RAMs in the generated High-Level Synthesis (HLS) code use the RAM Mapping optimization. Without this optimization, the variables are mapped to registers. RAM mapping is an area optimization. It reduces the area of your design in the target hardware.

- Pipelining of for-Loops

Pipelining allows concurrent execution of multiple iterations. The next iteration of a loop can begin execution before the previous iteration completes its execution. Pipelining optimises the execution speed and improves the throughput of the code at the expense of increased resources.